没有合适的资源?快使用搜索试试~ 我知道了~

LPC17xx中文用户手册

温馨提示

试读

498页

第一章 概述 第二章 存储器映射 第三章 系统控制 第四章 计时和功率控制 第五章 存储器加速模块 第六章 嵌套向量中断控制器 第七章 引脚配置 第八章 引脚连接模块 第九章 通用输入输出GPIO 第十章 以太网 第十一章 USB设备控制器 第十二章 USB主机控制器 第十三章 USB OTG控制器 第十四章 通用异步收发器UART1 第十五章 通用异步收发器UART0、2... 第十六章 CAN1/2 第十七章 SPI控制器 第十八章 SSP0、1接口控制器 第十九章 I2C0、1、2 第二十章 I2S接口 第二十一章 定时器0~3 第二十二章 重复中断定时器0~3 第二十三章 系统节拍定时器0~3 第二十四章 脉宽调制器 第二十五章 电机控制PWM 第二十六章 正交编码接口(QEI) 第二十七章 实时时钟和备用寄存器 第二十八章 看门狗定时器 第二十九章 模数转换器ADC 第三十章 数模转换器DAC 第三十一章 通用DMA 第三十二章 Flash存储器接口和编程 第三十三章 JTAG、(SWD)串行调试

资源推荐

资源详情

资源评论

第1章 概述

1.1 简介

LPC1700 系列 Cortex-M3 微控制器用于处理要求高度集成和低功耗的嵌入式应用。ARM

Cortex-M3 是下一代新生内核,它可提供系统增强型特性,例如现代化调试特性和支持更高级

别的块集成。

LPC1700 系列 Cortex-M3 微控制器的操作频率可达 100MHz。ARM Cortex-M3 CPU 具有 3

级流水线和哈佛结构,带独立的本地指令和数据总线以及用于外设的稍微低性能的第三条总线。

ARM Cortex-M3 CPU 还包含一个支持随机跳转的内部预取指单元。

LPC1700 系列 Cortex-M3 微控制器的外设组件包含高达 512KB 的 Flash 存储器、64KB 的

数据存储器、以太网 MAC、USB 主机/从机/OTG 接口、8 通道的通用 DMA 控制器、4 个 UART、

2 条 CAN 通道、2 个 SSP 控制器、SPI 接口、3 个 I

2

C 接口、2-输入和 2-输出的 I

2

S 接口、8 通

道的 12 位 ADC、10 位 DAC、电机控制 PWM、正交编码器接口、4 个通用定时器、6-输出的

通用 PWM、带独立电池供电的超低功耗 RTC 和多达 70 个的通用 I/O 管脚。

1.2 特性

ARM Cortex-M3 处理器,可在高至 100MHz 的频率下运行,并包含一个支持 8 个区的

存储器保护单元(MPU);

ARM Cortex-M3 内置了嵌套的向量中断控制器(NVIC);

具有在系统编程(ISP)和在应用编程(IAP)功能的 512KB 片上 Flash 程序存储器。

把增强型的 Flash 存储加速器和 Flash 存储器在 CPU 本地代码/数据总线上的位置进行

整合,则 Flash 可提供高性能的代码;

64KB 片内 SRAM 包括:

–32KB SRAM 可供高性能 CPU 通过本地代码/数据总线访问;

–2 个 16KB SRAM 模块,带独立访问路径,可进行更高吞量的操作。这些 SRAM 模

块可用于以太网、USB、DMA 存储器,以及通用指令和数据存储;

AHB 多层矩阵上具有 8 通道的通用 DMA 控制器,它可结合 SSP、I

2

S、UART、模数

和数模转换器外设、定时器匹配信号和 GPIO 使用,并可用于存储器到存储器的传输;

多层 AHB 矩阵内部连接,为每个 AHB 主机提供独立的总线。AHB 主机包括 CPU、

通用 DMA 控制器、以太网 MAC 和 USB 接口。这个内部连接特性提供无仲裁延迟的

通信,除非 2 个主机尝试同时访问同一个从机;

分离的 APB 总线允许在 CPU 和 DMA 之间提供更多的带宽,更少的延迟。CPU 无须

等待 APB 写操作完成;

串行接口

–以太网 MAC 带 RMII 接口和相关的 DMA 控制器;

–USB 2.0 全速从机/主机/OTG 控制器,带有用于从机、主机功能的片内 PHY 和相关

的 DMA 控制器;

–4 个 UART,带小数波特率发生功能、内部 FIFO、DMA 支持和 RS-485 支持。1 个

UART 带有 modem 控制 I/O 并支持 RS-485/EIA-485,全部的 UART 都支持 IrDA;

–CAN 控制器,带 2 个通道;

–SPI 控制器

,具有同步、串行、全双工通信和可编程的数据长度;

–2 个 SSP 控制器,带有 FIFO,可按多种协议进行通信。其中一个可选择用于 SPI,

并且和 SPI 共用中断。

SSP 接口可以与 GPDMA 控制器一起使用;

1/498

–3 个增强型的 I

2

C 总线接口,其中 1 个具有开漏输出功能,支持整个 I

2

C 规范和数据

速率为 1Mbit/s 的快速模式,另外 2 个具有标准的端口管脚。增强型特性包括多个

地址识别功能和监控模式;

–I

2

S(Inter-IC Sound)接口,用于数字音频输入或输出,具有小数速率控制功能。I

2

S

接口可与 GPDMA 一起使用。I

2

S 接口支持 3-线的数据发送和接收或 4-线的组合发

送和接收连接,以及主机时钟输入/输出;

其它外设:

–70 个(100 个管脚封装

)通用 I/O(GPIO)管脚

,带可配置的上拉/下拉电阻。AHB

总线上的所有 GPIO 可进行快速访问,支持新的、可配置的开漏操作模式;GPIO 位

于存储器中,它支持 Cortex-M3 位带宽并且由通用 DMA 控制器使用;

–12 位模数转换器(ADC),可在 8 个管脚间实现多路输入,转换速率高达 1MHz,

并具有多个结果寄存器。12 位 ADC 可与 GPDMA 控制器一起使用;

–10 位数模转换器(DAC),具有专用的转换定时器,并支持 DMA 操作;

–4 个通用定时/计数器,共有 8 个捕获输入和 10 个比较输出。每个定时器模块都具

有一个外部计数输入。可选择特定的定时器事件来产生 DMA 请求;

–1 个电机控制 PWM,支持三相的电机控制;

–正交编码器接口,可监控一个外部正交编码器;

–1 个标准的 PWM/定时器模块,带外部计数输入;

–实时时钟(RTC)带有独立的电源域。RTC 通过专用的 RTC 振荡器来驱动。RTC

模块包括 20 字节电池供电的备用寄存器,当芯片的其它部分掉电时允许系统状态存

储在该寄存器中。

电池电源可由标准的 3V 锂电池供电。当电池电压掉至 2.1V 的低

电压时,RT

C 仍将会继续工作。RTC 中断可将 CPU 从任何低功率模式中唤醒;

–看门狗定时器(WDT),该定时器的时钟源可在内部 RC 振荡器、RTC 振荡器或 APB

时钟三者间进行选择;

–支持 ARM Cortex-M3 系统节拍定时器,包括外部时钟输入选项;

–重复性的中断定时器提供可编程和重复定时的中断;

标准 JTAG 测试/调试接口以及串行线调试和串行线跟踪端口选项;

仿真跟踪模块支持实时跟踪;

4 个低功率模式:睡眠、深度睡眠、掉电、深度掉电;

单个 3.3V 电源(2.4V – 3.6V)。温度范围为-40C - 85C;

4 个外部中断输入,可配置为边沿/电平触发。PORT0 和 PORT2 上的所有管脚都可用

作边沿触发的中断源;

不可屏蔽中断(NMI)输入;

时钟输出功能,可反映主振荡器时钟、IRC 时钟、RTC 时钟、CPU 时钟或 USB 时钟

的输出状态;

当处于掉电模式时,可通过中断(包括外部中断、RTC 中断、USB 活动中断、

以太网

唤醒中断、CAN 总线活动中断、PORT0/2 管脚中断

和 NMI)将处理器从掉电模式中

唤醒;

每个外设都自带时钟分频器,以进一步节省功耗;

带掉电检测功能,可对掉电中断和强制复位分别设置阀值;

片内有上电复位电路;

片内晶振工作频率为 1MHz 到 24MHz;

4MHz 内部 RC 振荡器可在±1%的精度内调整,可选择用作系统时钟;

2/498

通过片内 PLL,没有高频晶振,CPU 也可以最高频率运转。用户可从主振荡器、内部

RC 振荡器或 RTC 振荡器三者中选择一个作为 PLL 时钟源;

第二个专用的 PLL 可用于 USB 接口,以允许增加主 PLL 设置的灵活性;

用户可在管脚对应的多种功能中进行选择;

可采用 100 脚和 80 脚 LQFP 封装(14×14×1.4mm)。

1.3 应用

静电计;

照明设备;

工业网络;

报警系统;

白色家电;

电机控制;

1.4 订购信息

表 1.1 订购信息

封装

器件型号

名称 描述 版本

LPC1768FBD100

LPC1766FBD100

LPC1765FBD100

LPC1764FBD100

LQFP100

LQFP 封装;100 脚;本体 14×14×1.4mm

SOT407-1

LPC1758FBD80

LPC1756FBD80

LPC1754FBD80

LPC1752FBD80

LPC1751FBD80

LQFP80

LQFP 封装;80 脚;本体 12×12×1.4mm

SOT315-1

1.4.1 器件选项汇总

表 1.2 LPC1700 系列 Cortex-M3 微控制器器件的订购选项

器件型号

Flash SRAM

以太网

USB CAN I

2

S DAC

封装 采样

LPC1768FBD100 512KB 64KB

有

Device/Host/OTG 2

有 有 100 脚 待定

LPC1766FBD100 256KB 64KB

有

Device/Host/OTG 2

有 有 100 脚 待定

LPC1765FBD100 256KB 64KB

无

Device/Host/OTG 2

有 有 100 脚 待定

LPC1764FBD100 128KB 32KB

有

Device 2

无 无 100 脚 待定

LPC1758FBD80 512KB 64KB

有

Device/Host/OTG 2

有 有 80 脚 待定

LPC1756FBD80 256KB 32KB

无

Device/Host/OTG 2

有 有 80 脚 待定

LPC1754FBD80 128KB 32KB

无

Device/Host/OTG 1

无 有 80 脚 待定

LPC1752FBD80 64KB 16KB

无

Device 1

无 无 80 脚 待定

LPC1751FBD80 32KB 8KB

无

Device 1

无 无 80 脚 待定

3/498

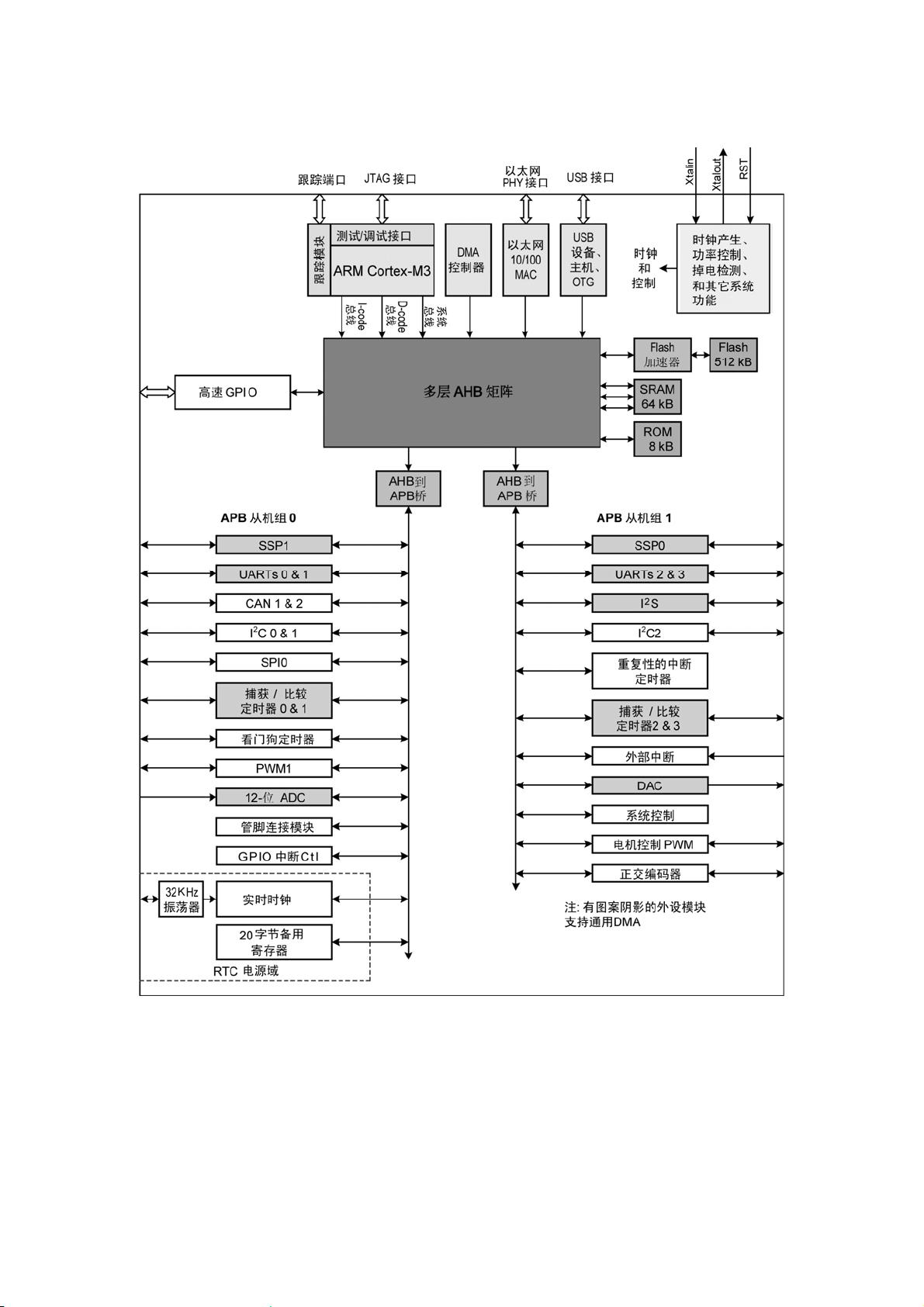

1.5 简化方框图

图 1.1 LPC1768 简化方框图

1.6 结构概述

ARM Cortex-M3 包含三条 AHB-Lite 总线,一条系统总线以及 I-code 和 D-code 总线,后二

者的速率较快,且在 TCM 接口的用法类似:一条总线专用于指令取指(I-code),另一条总线

用于数据访问(D-code)。这二条内核总线的用法允许同时执行操作,即使同时要对不同的设

备目标进行操作。

4/498

LPC1700 系列Cortex-M3 微控制器使用多层AHB矩阵来连接上Cortex-M3 总线,并以灵活

的方式将其它总线主机连接到外设,允许矩阵的不同从机端口上的外设可以同时被不同的总线

主机访问,从而能获取到最优化的性能。图 1.

2所示为多层矩阵连接的详细情况。

APB 外设使用多层 AHB 矩阵的独立从机端口通过两条 APB 总线连接到 CPU。这减少了

CPU 和 DMA 控制器之间的争用,可实现更好的性能。APB 总线桥配置为缓冲区写操作,

使得

CPU 或 DMA 控制器无需等待 APB 写操作结束。

1.7 ARM Cortex-M3 处理器

ARM Cortex-M3 是一个通用的 32 位微处理器,它具有高性能和超低功耗的特性。Cortex-M3

还提供许多新的特性,包括 Thumb-2 指令集、低中断延时、硬件除法、可中断/可持续的多次加

载和存放指令、对中断的自动状态进行保存和恢复、紧密结合中断控制器与唤醒中断控制器、

多条内核总线可同时用于访问。

采用这样的流水处理技术,使得各个器件的处理和存储器系统可以连续进行操作。通常,

当一个指令正在执行时,第二个指令正在进行解码,而第三个指令正在存储器中被取指出来。

ARM Cortex-M3 处理器的详细描述请查看 ARM 官方网站的 Cortex-M3 技术参考手册。

1.7.1 Cortex-M3 配置选项

LPC1700 系列 Cortex-M3 微控制器使

用 Cortex-M3 CPU 的 r2p0 版本,其中包含了下面所标

记的众多可配置选项。

系统选项:

包含嵌套的向量中断控制器(NVIC)

。NVIC 包括 SYSTICK 定时器;

包含唤醒中断控制器(WIC)。WIC 可实现更有效的选项,将 CPU 从低功耗模式中唤

醒;

包含存储器保护单元(MPU);

包含 ROM 表。ROM 表提供了调试部件到外部调试系统的地址;

调试相关的选项:

包含 JTAG 调试接口;

包含串行线调试。串行线调试允许仅使用两条线进行调试操作,简单的跟踪功能可增

加第三条线;

包含嵌入式跟踪宏单元(ETM)。ETM 提供指令跟踪功能;

包含数据观察点和跟踪(DWT)单元。DWT 允许数据地址或数据值匹配为跟踪信息

或触发其它事件。DWT 包含 4 个比较器和计数器以用于特定的内部事件;

包含指令跟踪宏单元(ITM)。软件可写 ITM 以发送信息到跟踪端口;

包含跟踪端口接口单元(TPIU)。TPIU 编码并向外面提供跟踪信息。

这可以在串行线

浏览器管脚(Serial Wire

Viewer pin)或 4 位并行跟踪端口上实现;

包含 Flash 修补和断点(FPB)。FPB 可产生硬件断点并且在代码空间中重新映射特定

的地址到 SRAM 作为更改非易失性代码的暂时方法。FPB 包括 2 个文字比较器(literal

comparator)和 6 个指令比较器。

1.8 片上Flash存储器系统

LPC1700 系列 Cortex-M3 微控制器含有 512KB 的片上 Flash 存储器。一个新的 2-端口 Flash

存储器加速器通过两条快速 AHB-Lite 总线将其使用性能扩至极限。该存储器可用于存放代码

和数据。对 Flash 存储器的编写有若干种方式来实现。它可通过串口来进行在系统编程。应用

5/498

剩余497页未读,继续阅读

资源评论

z8893662014-12-18很好,资料可以使用

z8893662014-12-18很好,资料可以使用

qq_15290961

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功