第 10 章 Verilog 操作符

学习内容:

•

熟悉 Verilog 语言的操作符

操作符类型

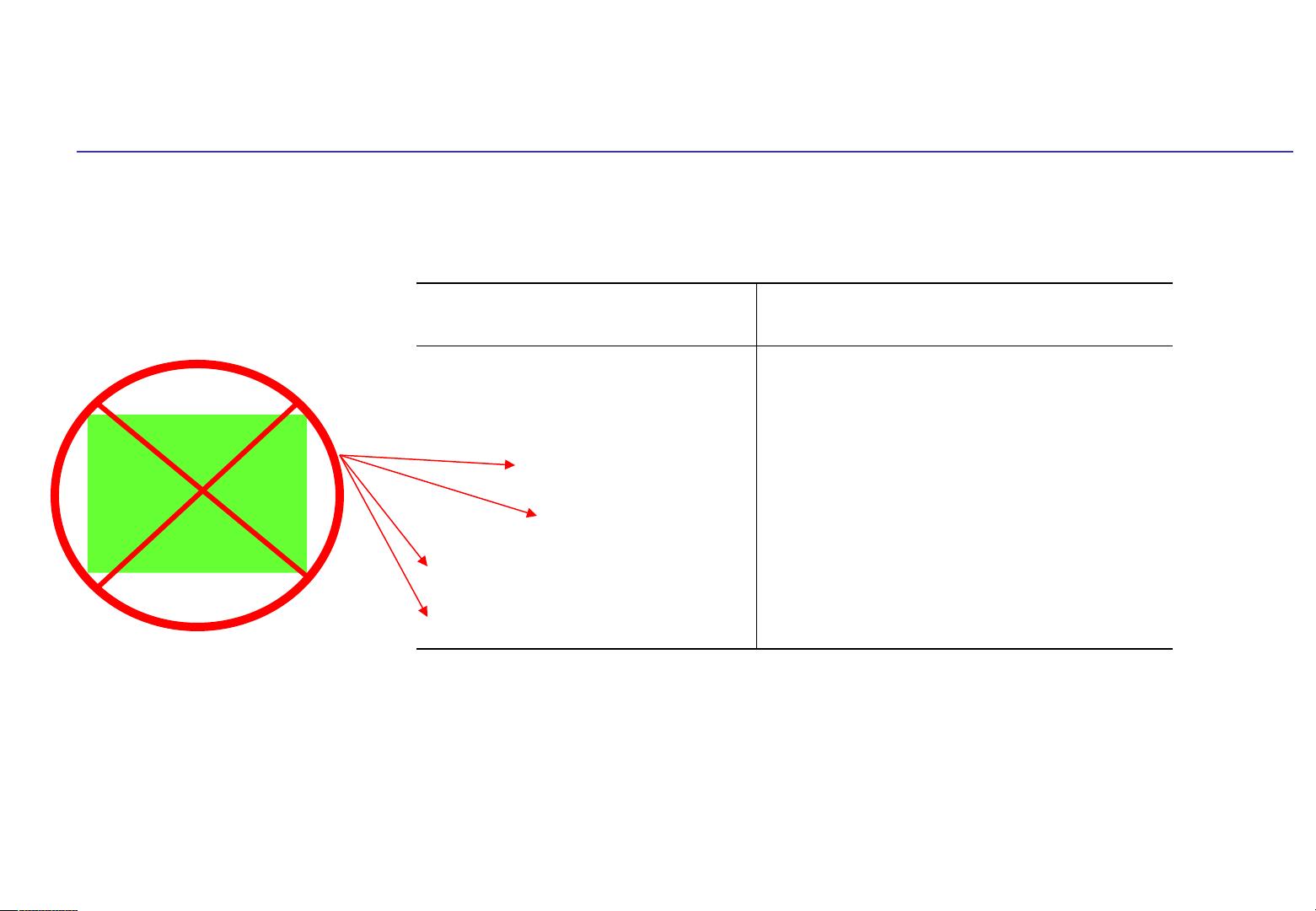

下表以优先级顺序列出了 Verilog 操作符。注意“与”操作符的优先级总是比相同

类型的“或”操作符高。本章将对每个操作符用一个例子作出解释。

操作符类型 符号

连接及复制操作符

一元操作符

算术操作符

逻辑移位操作符

关系操作符

相等操作符

按位操作符

逻辑操作符

条件操作符

{} {{}}

! ~ & | ^

* / %

+ -

<< >>

> < >= <=

= = = = = != != =

&

^ ~^

|

&&

||

? :

最高

最低

优先级

Verilog 中的大小 (size) 与符号

•

Verilog 根据表达式中变量的长度对表达式的值自动地进行调整。

•

Verilog 自动截断或扩展赋值语句中右边的值以适应左边变量的长度。

•

当一个负数赋值给无符号变量如 reg 时, Verilog 自动完成二进制补码计算

module sign_size;

reg [3:0] a, b;

reg [15:0] c;

initial begin

a = -1; // a 是无符号数,因此其值为

1111

b = 8; c= 8; // b = c = 1000

#10 b = b + a; // 结果 10111 截断 , b = 011

1

#10 c = c + a; // c = 10111

end

endmodule

算术操作符

module arithops ();

parameter five = 5;

integer ans, int;

reg [3: 0] rega, regb;

reg [3: 0] num;

initial begin

rega = 3;

regb = 4'b1010;

int = -3; //int = 1111……1111_1101

end

initial fork

#10 ans = five * int; // ans = -15

#20 ans = (int + 5)/ 2; // ans = 1

#30 ans = five/ int; // ans = -1

#40 num = rega + regb; // num = 1101

#50 num = rega + 1; // num = 0100

#60 num = int; // num = 1101

#70 num = regb % rega; // num = 1

#80 $finish;

join

endmodule

+ 加

- 减

* 乘

/ 除

% 模

•

将负数赋值给 reg 或其它无符号变

量使用 2 的补码算术。

•

如果操作数的某一位是 x 或 z ,则

结果为 x

•

在整数除法中,余数舍弃

•

模运算中使用第一个操作数的符号

注意 integer 和 reg

类型在算术运算

时的差别。 intege

r 是有符号数,而

reg 是无符号数。

按位操作符

module bitwise ();

reg [3: 0] rega, regb, regc;

reg [3: 0] num;

initial begin

rega = 4'b1001;

regb = 4'b1010;

regc = 4'b11x0;

end

initial fork

#10 num = rega & 0; // num = 0000

#20 num = rega & regb; // num = 1000

#30 num = rega | regb; // num = 1011

#40 num = regb & regc; // num = 10x0

#50 num = regb | regc; // num = 1110

#60 $finish;

join

endmodule

~ not

& and

| or

^ xor

~ ^ xnor

^ ~ xnor

•

按位操作符对矢量中相对应位运算。

regb = 4'b1 0 1

0

regc = 4'b1 x 1

0

num = regb & regc = 1 0 1 0 ;

•

位值为 x 时不一定产生 x 结果。如 #50

时的 or 计算。

当两个操作数位数不同时,位数少

的操作数零扩展到相同位数。

a = 4'b1011;

b = 8'b01010011;

c = a | b; // a 零扩展为 8'b00001011

- 1

- 2

- 3

前往页