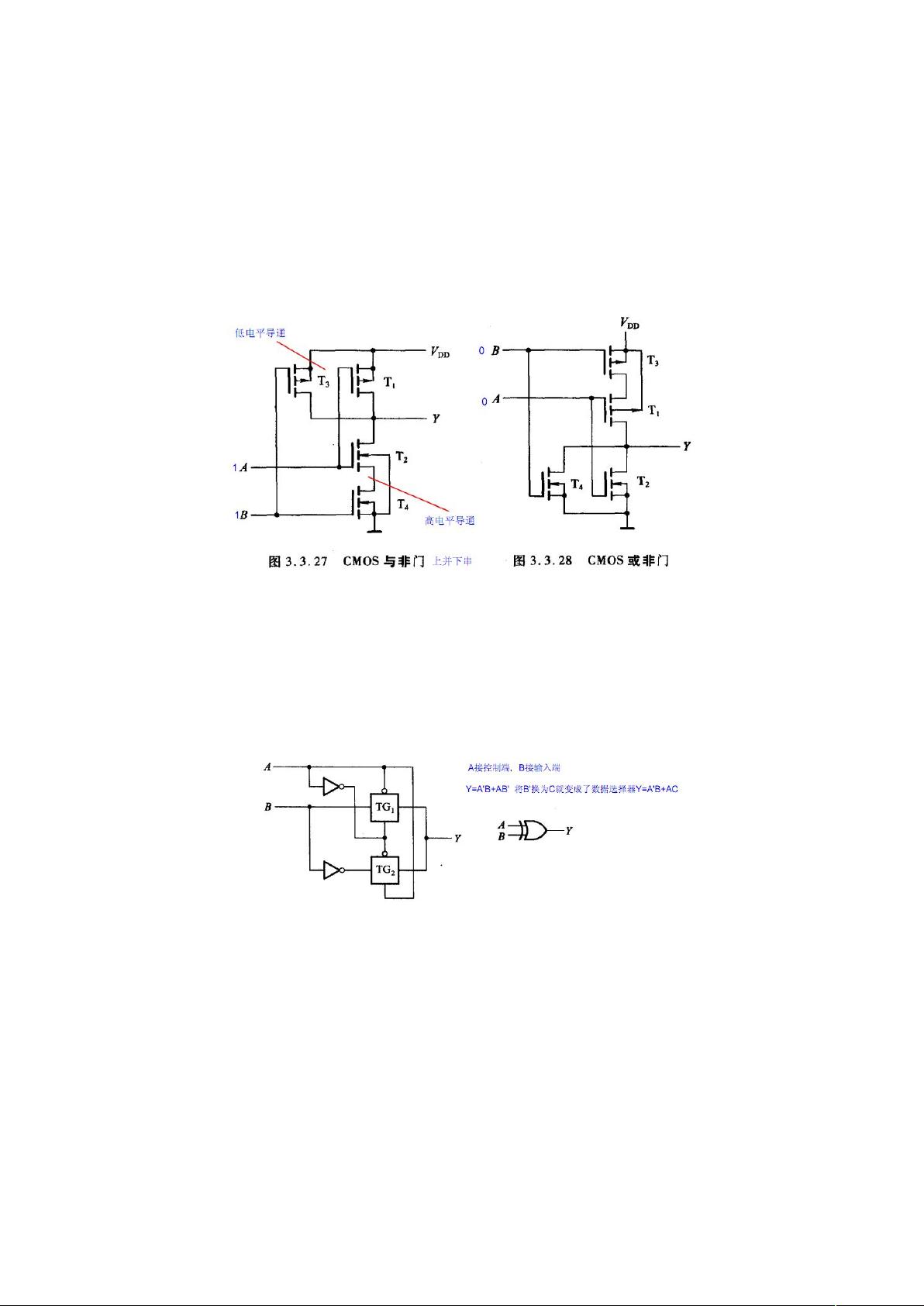

"数字设计工程师笔试面试" 数字设计工程师笔试面试是一份涵盖数电模电基础知识的笔试题汇集,涵盖同步逻辑、异步逻辑、时序设计、触发器、建立时间、保持时间、亚稳态、同步器、线与逻辑、竞争与冒险现象等重要知识点。 同步逻辑和异步逻辑 同步逻辑是时钟之间有固定的因果关系,异步逻辑是各时钟之间没有固定的因果关系。同步时序逻辑电路的特点是各触发器的时钟端全部连接在一起,并接在系统时钟端,只有当时钟脉冲到来时,电路的状态才能改变。 同步电路和异步电路的区别 同步电路是存储电路中所有触发器的时钟输入端都接同一个时钟脉冲源,因而所有触发器的状态的变化都与所加的时钟脉冲信号同步。异步电路是电路没有统一的时钟,有些触发器的时钟输入端与时钟脉冲源相连,只有这些触发器的状态变化与时钟脉冲同步,而其他的触发器的状态变化不与时钟脉冲同步。 时序设计的实质 时序设计的实质就是满足每一个触发器的建立/保持时间的要求。 建立时间与保持时间 建立时间是触发器在时钟上升沿到来之前,其数据输入端的数据必须保持不变的最小时间。保持时间是触发器在时钟上升沿到来之后,其数据输入端的数据必须保持不变的最小时间。 为什么触发器要满足建立时间和保持时间 因为触发器内部数据的形成是需要一定的时间的,如果不满足建立和保持时间,触发器将进入亚稳态,进入亚稳态后触发器的输出将不稳定,在0和1之间变化,这时需要经过一个恢复时间,其输出才能稳定,但稳定后的值并不一定是你的输入值。 亚稳态 亚稳态是指触发器无法在某个规定的时间段内到达一个可以确认的状态。使用两级触发器来使异步电路同步化的电路其实叫做“一位同步器”,他只能用来对一位异步信号进行同步。 线与逻辑 线与逻辑是两个输出信号相连可以实现与的功能。在硬件上,要用oc门来实现, 同时在输出端口应加一个上拉电阻。 竞争与冒险现象 在组合电路中,某一输入变量经过不同途径传输后,到达电路中某一汇合点的时间有先有后,这种现象称竞争;由于竞争而使电路输出发生瞬时错误的现象叫做冒险。 常用逻辑电平 常用逻辑电平包括TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVDS、GTL、BT等。TTL与COMS电平可以直接互连吗?答案是可以,但需要注意电平转换的问题。

剩余20页未读,继续阅读

- 粉丝: 0

- 资源: 3

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功