没有合适的资源?快使用搜索试试~ 我知道了~

VHDL程序练习题含答案.doc

1.该资源内容由用户上传,如若侵权请联系客服进行举报

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

版权申诉

0 下载量 200 浏览量

2021-10-04

14:58:47

上传

评论

收藏 1.1MB DOC 举报

温馨提示

试读

35页

VHDL程序练习题含答案.doc

资源推荐

资源详情

资源评论

- -

VHDL 程序填空题

(一) 在下面横线上填上适宜的 VHDL 关键词,完成 2 选 1 多路选择器的设计。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

1 MUX21 IS

PORT(SEL:IN STD_LOGIC;

A,B:IN STD_LOGIC;

Q: OUT STD_LOGIC );

END MUX21;

2 BHV OF MUX21 IS

BEGIN

Q<=A WHEN SEL=’1’ ELSE B;

END BHV;

(二) 在下面横线上填上适宜的语句,完成 BCD-7 段 LED 显示译码器的设计。

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY BCD_7SEG IS

PORT( BCD_LED : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

LEDSEG : OUT STD_LOGIC_VECTOR(6 DOWNTO 0));

END BCD_7SEG;

ARCHITECTURE BEHAVIOR OF BCD_7SEG IS

BEGIN

PROCESS(BCD_LED)

3

IF BCD_LED="0000" THEN LEDSEG<="0111111";

ELSIF BCD_LED="0001" THEN LEDSEG<="0000110";

ELSIF BCD_LED="0010" THEN LEDSEG<= 4 ;

ELSIF BCD_LED="0011" THEN LEDSEG<="1001111";

ELSIF BCD_LED="0100" THEN LEDSEG<="1100110";

ELSIF BCD_LED="0101" THEN LEDSEG<="1101101";

ELSIF BCD_LED="0110" THEN LEDSEG<="1111101";

ELSIF BCD_LED="0111" THEN LEDSEG<="0000111";

ELSIF BCD_LED="1000" THEN LEDSEG<="1111111";

ELSIF BCD_LED="1001" THENLEDSEG<="1101111";

ELSE LEDSEG<= 5 ;

END IF;

END PROCESS;

END BEHAVIOR;

(三) 在下面横线上填上适宜的语句,完成数据选择器的设计。

- word.zl-

- -

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY MUX16 IS

PORT( D0, D1, D2, D3: IN STD_LOGIC_VECTOR(15 DOWNTO 0);

SEL: IN STD_LOGIC_VECTOR( 6 DOWNTO 0);

Y: OUT STD_LOGIC_VECTOR(15 DOWNTO 0));

END;

ARCHITECTURE ONE OF MUX16 IS

BEGIN

WITH 7 SELECT

Y <= D0 WHEN "00",

D1 WHEN "01",

D2 WHEN "10",

D3 WHEN 8 ;

END;

(四) 在下面横线上填上适宜的语句,完成 JK 触发器的设计。

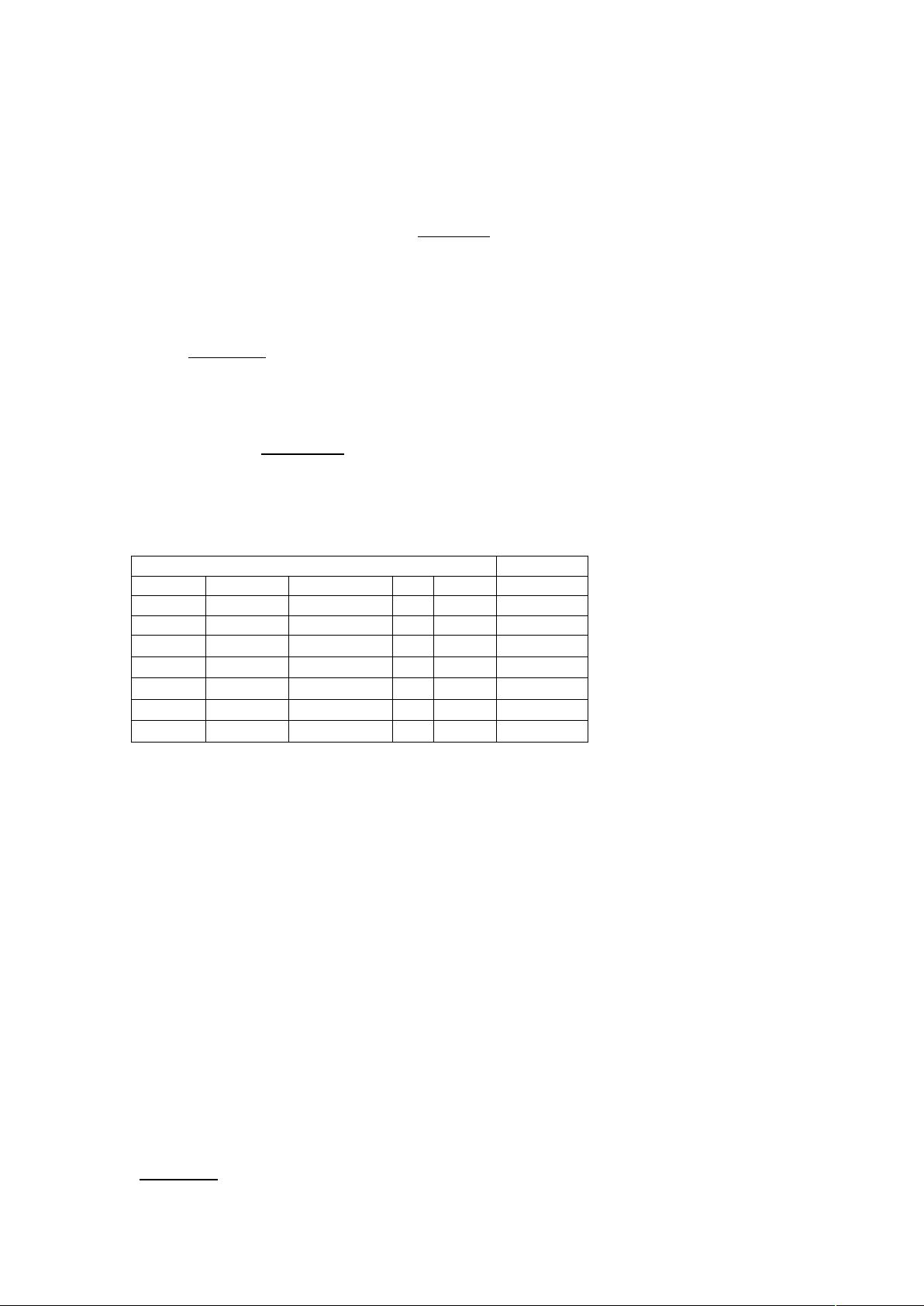

说明:设计一个异步复位/置位 JK 触发器,其真值表如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY JKFF1 IS

PORT (PSET,CLR,CLK,J,K: IN STD_LOGIC;

Q : OUT STD_LOGIC);

END JKFF1;

ARCHITECTURE MAXPLD OF JKFF1 IS

SIGNAL TEMP:STD_LOGIC;

BEGIN

PROCESS(PSET,CLR,CLK)

BEGIN

IF (PSET='0'AND CLR='1' ) THEN TEMP<='1';

ELSIF (PSET='1'AND CLR='0' ) THEN TEMP<='0';

ELSIF (PSET='0'AND CLR='0' ) THEN NULL;

9 (CLK'EVENT AND CLK='1') THEN

- word.zl-

INPUT OUTPUT

PSET CLR CLK J K Q

0 1 X X X 1

1 0 X X X 0

0 0 X X X

不定

1 1

上升沿

0 1 0

1 1

上升沿

1 0 1

1 1

上升沿

1 1

翻转

1 1

上升沿

0 0

保持

- -

10 (J='0' AND K='0') THEN TEMP<=TEMP;

ELSIF (J='0' AND K='1') THEN TEMP<='0';

ELSIF (J='1' AND K='0') THENTEMP<='1';

ELSIF (J='1' AND K='1') THEN TEMP<= 11 ;

END IF;

END IF;

END PROCESS;

Q<=TEMP;

END ;

(五) 在下面横线上填上适宜的语句,完成计数器的设计。

说明:设电路的控制端均为高电平有效,时钟端 CLK,电路的预置数据输入端为 4 位 D,计

数输出端也为 4 位 Q,带同步始能 EN、异步复位 CLR 和预置控制 LD 的六进制减法计数

器。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT6 IS

PORT(EN,CLR,LD,CLK:IN STD_LOGIC;

D: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

Q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END CNT6;

ARCHITECTURE BEHA OF CNT6 IS

SIGNAL QTEMP:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(CLK,CLR,LD)

BEGIN

IF CLR='1' THEN QTEMP<="0000"; --CLR=1 清零

ELSIF (CLK'EVENT AND CLK='1') THEN --判断是否上升沿

IF LD='1' THEN QTEMP<= 12 ; --判断是否置位

ELSIF EN='1' THEN --判断是否允许计数

IF QTEMP="0000" THEN QTEMP<= 13 ; --等于 0,计数值置 5

ELSE QTEMP<= 14 ; --否那么,计数值减 1

END IF;

END IF;

END IF;

Q<=QTEMP;

END PROCESS;

END BEHA;

(六) 在下面横线上填上适宜的语句,完成状态机的设计。

说明:设计一个双进程状态机,状态 0 时如果输入〞10〞那么转为下一状态,否那么输

- word.zl-

- -

出〞1001〞;状态 1 时如果输入〞11〞那么转为下一状态,否那么输出〞0101〞;状态

2 时如果输 入 〞 01 〞那么转为下 一状态,否那 么输出 〞1100〞;状态 3 时如果输

入〞00〞那么转为状态 0,否那么输出〞0010〞。复位时为状态 0。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY MOORE1 IS

PORT (DATAIN: IN STD_LOGIC_VECTOR(1 DOWNTO 0);

CLK, RST:IN STD_LOGIC;

Q: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END;

ARCHITECTURE ONE OF MOORE1 IS

TYPE ST_TYPE IS (ST0, ST1, ST2, ST3); --定义 4 个状态

SIGNAL CST, NST: ST_TYPE; --定义两个信号〔现态和次态〕

SIGNAL Q1:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

REG: PROCESS(CLK, RST) --主控时序进程

BEGIN

IF RST='1' THEN CST<= 15 ; --异步复位为状态 0

ELSIF CLK'EVENT AND CLK='1' THEN

CST<= 16 ; --现态=次态

END IF;

END PROCESS;

COM: PROCESS(CST, DATAIN)

BEGIN

CASE CST IS

WHEN ST0 => IF DATAIN="10" THEN NST<=ST1;

ELSE NST<=ST0; Q1<="1001"; END IF;

WHEN ST1 => IF DATAIN="11" THEN NST<=ST2;

ELSE NST<=ST1; Q1<="0101"; END IF;

WHEN ST2 => IF DATAIN="01" THEN NST<=ST3;

ELSE NST<=ST2; Q1<="1100"; END IF;

WHEN ST3 => IF DATAIN="00" THEN NST<=ST0;

ELSE NST<=ST3; Q1<="0010"; END IF;

17 ;

END PROCESS;

Q<=Q1;

END;

(七) 在下面横线上填上适宜的语句,完成减法器的设计。

由两个 1 位的半减器组成一个 1 位的全减器

--1 位半减器的描述

LIBRARY IEEE;

- word.zl-

- -

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY HALF_SUB IS

PORT(A,B : IN STD_LOGIC;

DIFF,COUT : OUT STD_LOGIC);

END HALF_SUB;

ARCHITECTURE ART OF HALF_SUB IS

BEGIN

COUT<= 18 ; --借位

DIFF<= 19 ; --差

END ;

--1 位全减器描述

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY FALF_SUB IS

PORT(A,B,CIN: IN STD_LOGIC;

DIFF,COUT : OUT STD_LOGIC);

END FALF_SUB;

ARCHITECTURE ART OF FALF_SUB IS

COMPONENT HALF_SUB

PORT(A,B : IN STD_LOGIC;

DIFF,COUT : OUT STD_LOGIC);

END COMPONENT;

20 T0,T1,T2:STD_LOGIC;

BEGIN

U1: HALF_SUB PORT MAP(A,B, 21 ,T1);

U2: HALF_SUB PORT MAP(T0, 22 , 23 ,T2);

COUT<= 24 ;

END ;

(八) 在下面横线上填上适宜的语句,完成分频器的设计。

说明:占空比为 1:2 的 8 分频器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CLKDIV8_1TO2 IS

PORT(CLK:IN STD_LOGIC;

CLKOUT:OUT STD_LOGIC );

END CLKDIV8_1TO2;

ARCHITECTURE TWO OF CLKDIV8_1TO2 IS

SIGNAL CNT:STD_LOGIC_VECTOR(1 DOWNTO 0);

SIGNAL CK:STD_LOGIC;

BEGIN

PROCESS(CLK)

BEGIN

- word.zl-

剩余34页未读,继续阅读

资源评论

pyhm63

- 粉丝: 6

- 资源: 20万+

下载权益

C知道特权

VIP文章

课程特权

开通VIP

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功