AMBAAXI总线学习笔记.pdf

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

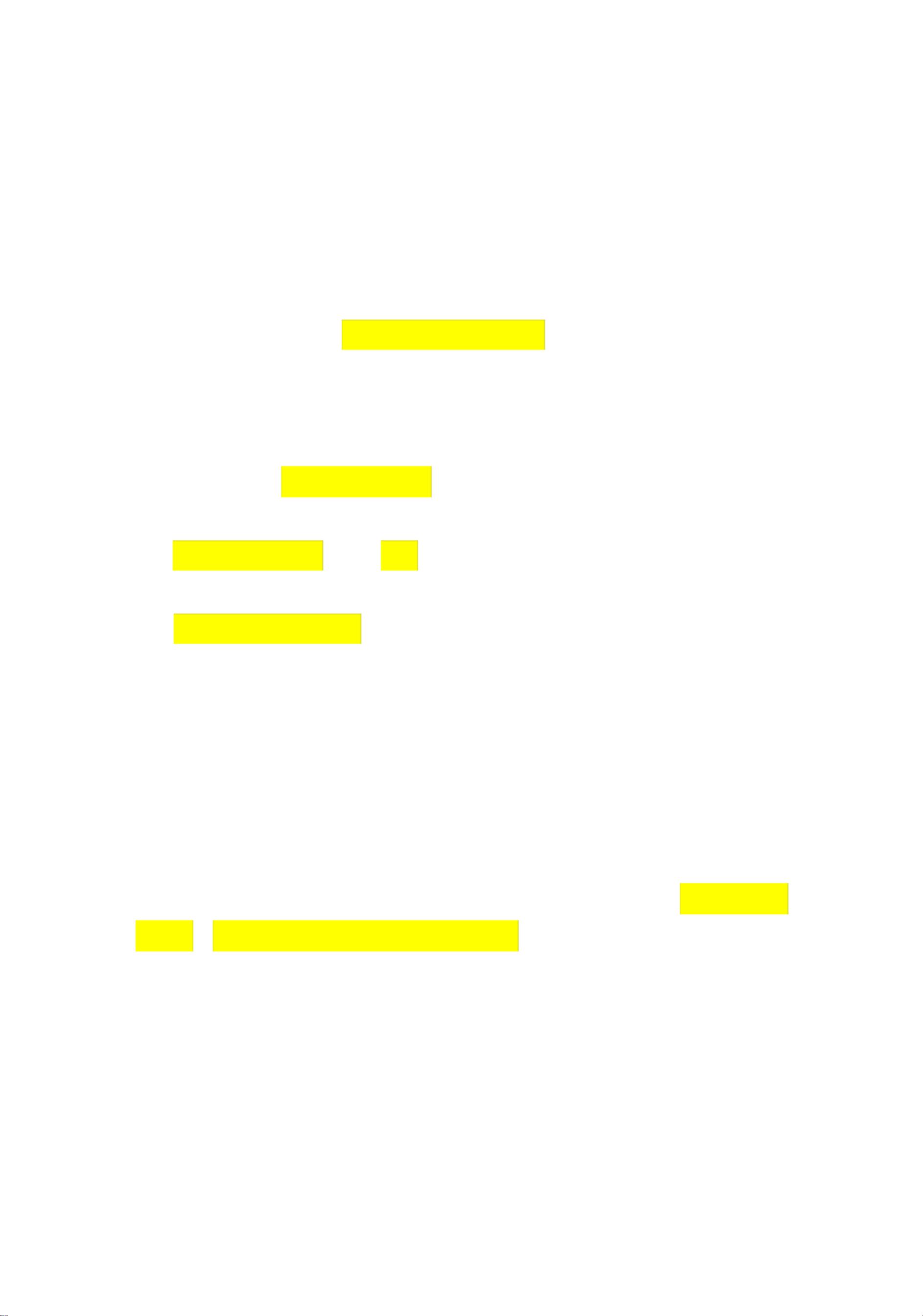

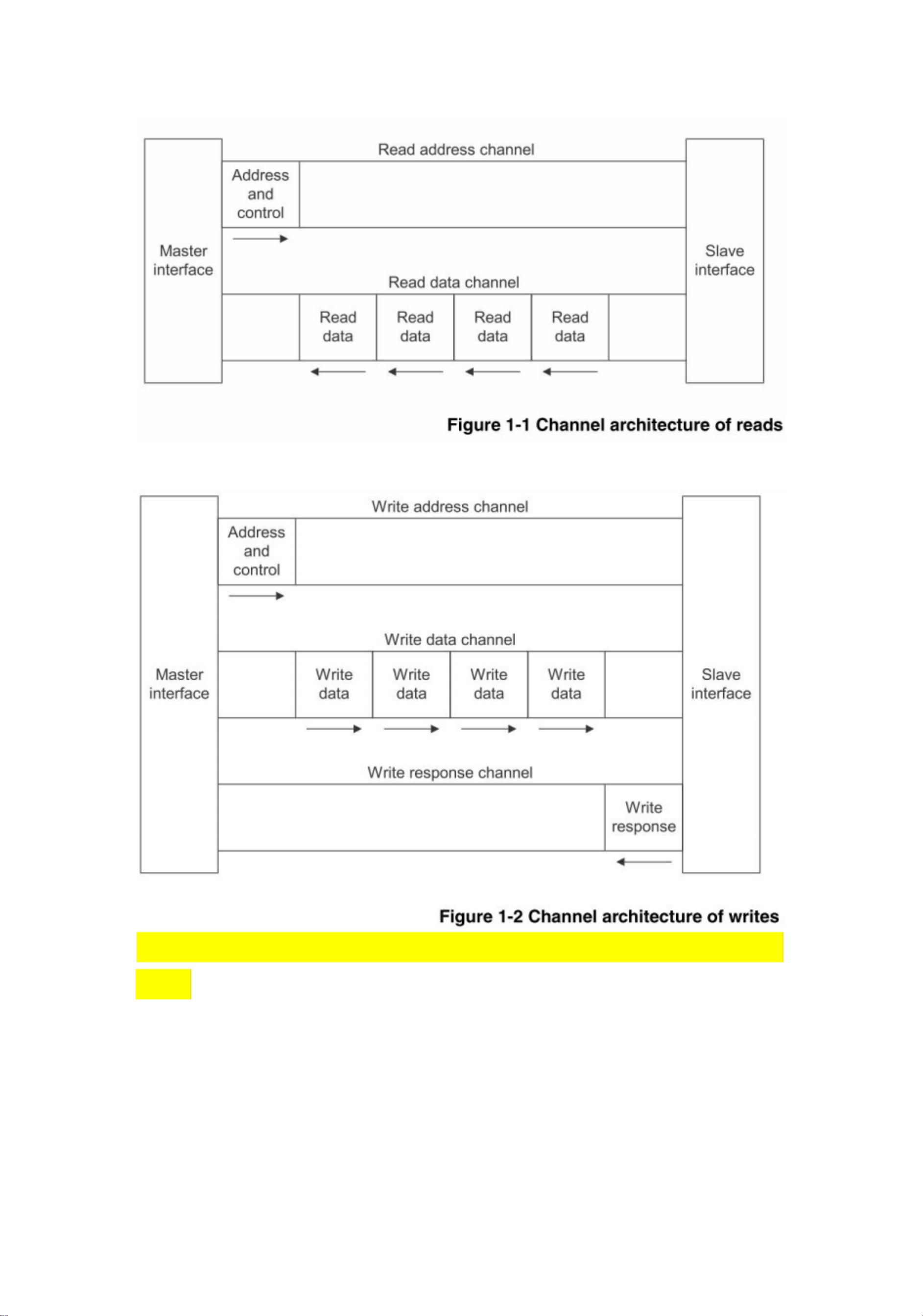

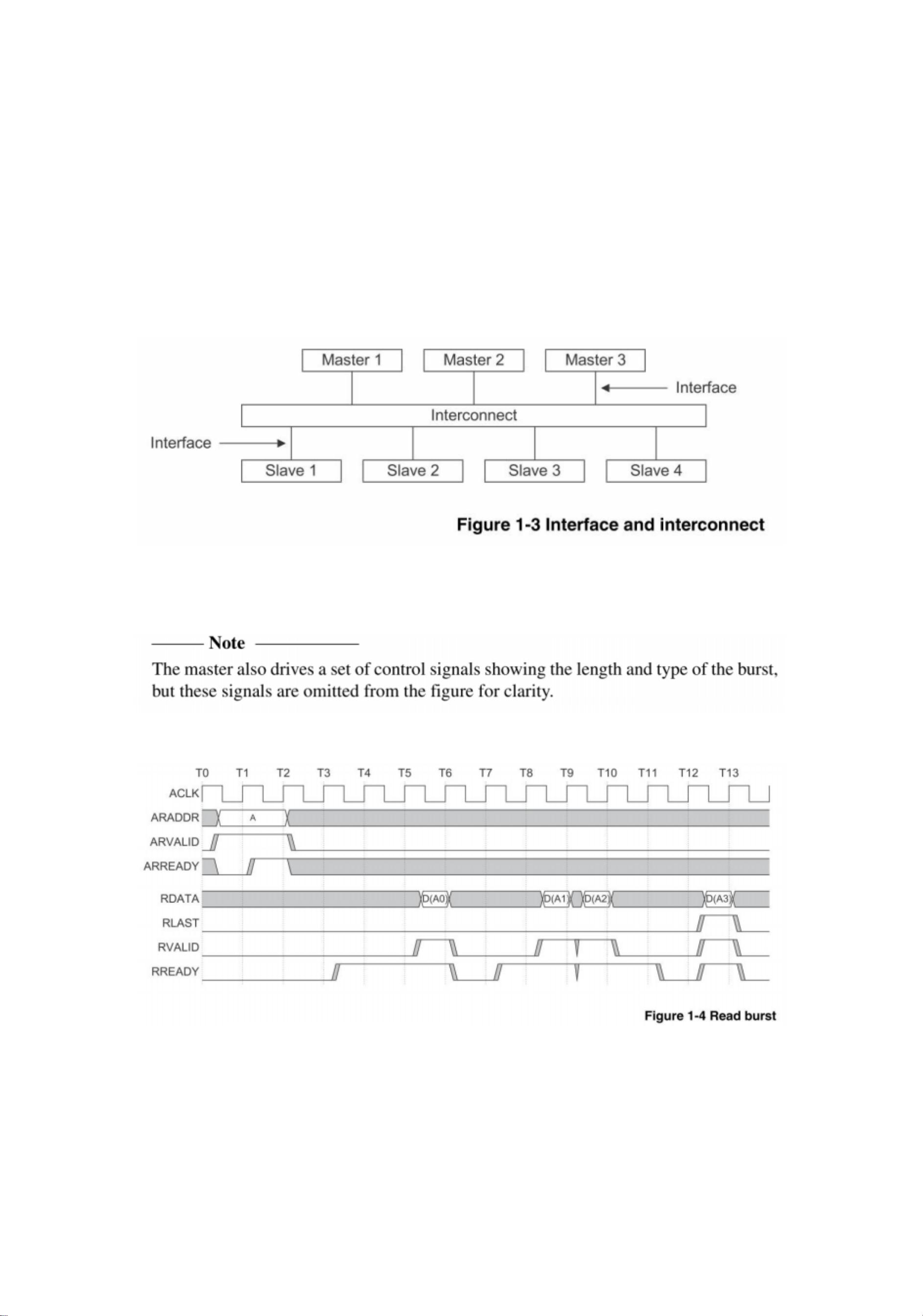

AXI (Advanced eXtensible Interface) 是一种由ARM公司推出的高级可扩展接口,它是AMBA(Advanced Microcontroller Bus Architecture)3.0协议的核心部分,专门设计用于高速、高带宽和低延迟的片上系统(SoC)内部通信。AXI协议的主要特点是将地址/控制和数据传输分开,支持非对齐数据传输,以及突发传输,从而提高了系统的效率和性能。 AXI协议的特性主要包括以下几点: 1. **单向通道体系结构**:AXI协议采用单向通道,信息仅在一个方向上传输,简化了跨时钟域的桥接,减少了门电路的数量,降低了延迟,尤其是在复杂SoC设计中。 2. **多数据交换支持**:AXI允许并行执行突发操作,提高了数据吞吐量,可以在较短时间内完成大量数据传输,同时降低功耗,满足高性能需求。 3. **独立的地址和数据通道**:地址和数据通道分离,允许对每个通道独立优化,可以独立调整时序,提高时钟频率,减少延迟。 AXI总线协议有5个独立的传输通道: 1. **Read Address Channel**:传输读取操作的地址和控制信息。 2. **Write Address Channel**:传输写入操作的地址和控制信息。 3. **Read Data Channel**:从设备到主机的读取数据和读响应信息的传输。 4. **Write Data Channel**:从主机到设备的写入数据传输。 5. **Write Response Channel**:设备响应写入操作的通道。 在每个传输通道中,都有VALID和READY握手信号,用来标记数据和控制信息的有效性。READ和WRITE事务都有自己的地址通道,携带必要的地址和控制信息。READ Data Channel还包括LAST信号,表示事务的最后一个数据。WRITE Data Channel则有byte lane,指出数据总线上有效的字节。 AXI协议还支持乱序传输,通过ID tag确保相同ID的事务按序完成,不同ID的事务可以乱序完成。例如,突发式读写过程中,设备可以通过LAST信号(如RLAST和WLAST)来标识传输结束,而写响应(Write Response Channel)提供设备确认写操作完成的方式。 第二章涉及的信号描述详细列出了全局信号、各种通道的信号,如写地址通道的AWID、AWADDR、AWLEN等,以及低功耗接口信号,这些都是实现AXI协议通信的基础。 AXI总线协议是现代SoC设计中的关键组成部分,其设计特点和信号机制为高效、灵活的片上通信提供了强大的支持。

剩余25页未读,继续阅读

- 粉丝: 10

- 资源: 15万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功