Contents

Contents

1 Introduction and Conventions

:::::::::::::::::::::::

4

1.1 Outline

::::::::::::::::::::::::::::::::::::::::::

4

1.2 Motivation

:::::::::::::::::::::::::::::::::::::::

4

1.3 Conventions

:::::::::::::::::::::::::::::::::::::

5

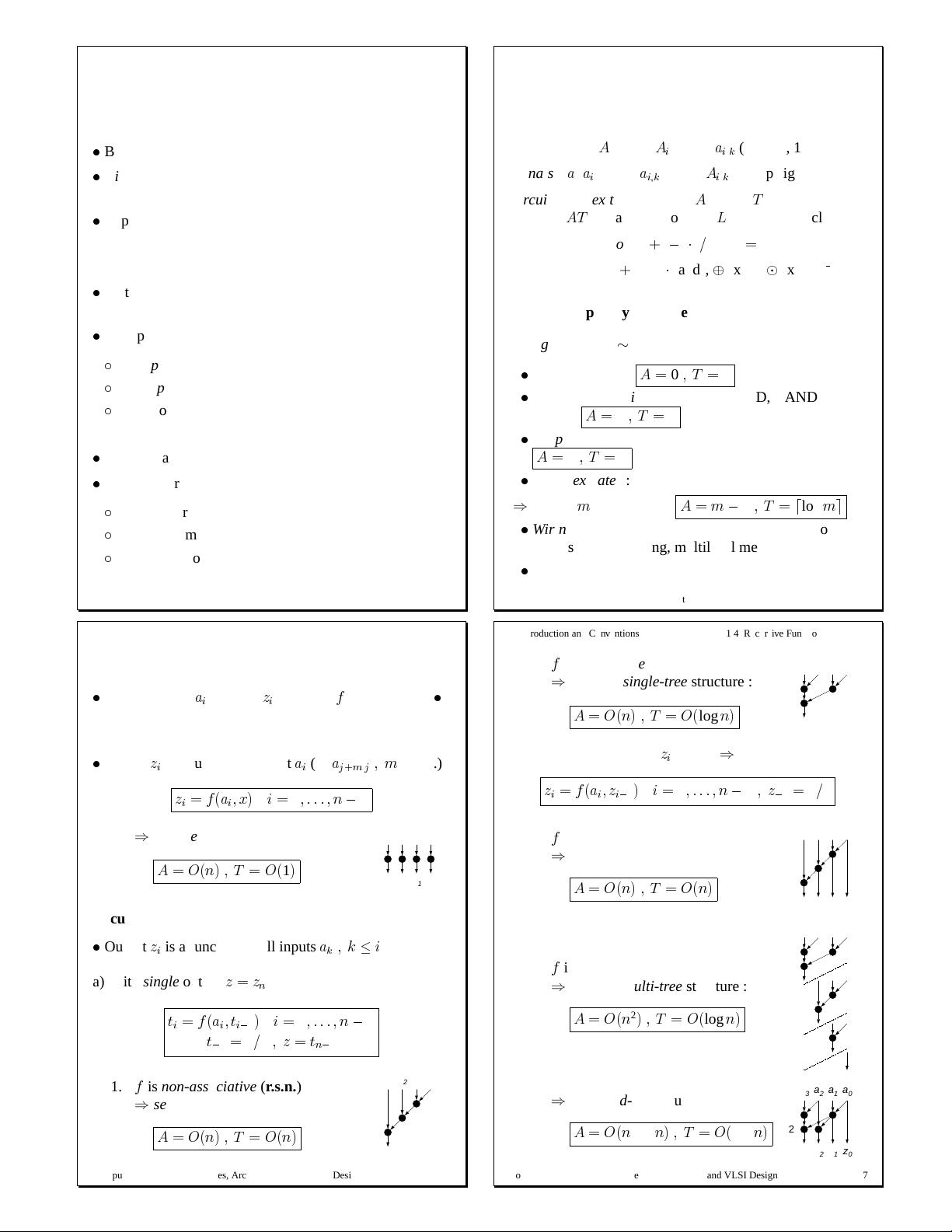

1.4 Recursive Function Evaluation

:::::::::::::::::::::

6

2 Arithmetic Operations

::::::::::::::::::::::::::::::

8

2.1 Overview

::::::::::::::::::::::::::::::::::::::::

8

2.2 Implementation Techniques

:::::::::::::::::::::::

9

3 Number Representations

:::::::::::::::::::::::::::

10

3.1 Binary Number Systems (BNS)

:::::::::::::::::::

10

3.2 Gray Numbers

::::::::::::::::::::::::::::::::::

13

3.3 Redundant Number Systems

::::::::::::::::::::::

14

3.4 Residue Number Systems (RNS)

::::::::::::::::::

16

3.5 Floating-Point Numbers

::::::::::::::::::::::::::

18

3.6 Logarithmic Number System

:::::::::::::::::::::

19

3.7 Antitetrational Number System

:::::::::::::::::::

19

3.8 Composite Arithmetic

:::::::::::::::::::::::::::

20

3.9 Round-Off Schemes

:::::::::::::::::::::::::::::

21

4 Addition

::::::::::::::::::::::::::::::::::::::::::

22

4.1 Overview

:::::::::::::::::::::::::::::::::::::::

22

4.2 1-Bit Adders, (m,k)-Counters

::::::::::::::::::::

23

Computer Arithmetic: Principles, Architectures, and VLSI Design 1

Contents

4.3 Carry-Propagate Adders (CPA)

:::::::::::::::::::

26

4.4 Carry-Save Adder (CSA)

:::::::::::::::::::::::::

45

4.5 Multi-Operand Adders

:::::::::::::::::::::::::::

46

4.6 Sequential Adders

:::::::::::::::::::::::::::::::

52

5 Simple / Addition-Based Operations

::::::::::::::::

53

5.1 Complement and Subtraction

:::::::::::::::::::::

53

5.2 Increment / Decrement

:::::::::::::::::::::::::::

54

5.3 Counting

:::::::::::::::::::::::::::::::::::::::

58

5.4 Comparison, Coding, Detection

:::::::::::::::::::

60

5.5 Shift, Extension, Saturation

::::::::::::::::::::::

64

5.6 Addition Flags

::::::::::::::::::::::::::::::::::

66

5.7 Arithmetic Logic Unit (ALU)

:::::::::::::::::::::

68

6 Multiplication

:::::::::::::::::::::::::::::::::::::

69

6.1 Multiplication Basics

::::::::::::::::::::::::::::

69

6.2 Unsigned Array Multiplier

:::::::::::::::::::::::

71

6.3 Signed Array Multipliers

:::::::::::::::::::::::::

72

6.4 Booth Recoding

:::::::::::::::::::::::::::::::::

73

6.5 Wallace Tree Addition

:::::::::::::::::::::::::::

75

6.6 Multiplier Implementations

:::::::::::::::::::::::

75

6.7 Composition from Smaller Multipliers

:::::::::::::

76

6.8 Squaring

:::::::::::::::::::::::::::::::::::::::

76

7 Division / Square Root Extraction

::::::::::::::::::

77

7.1 Division Basics

:::::::::::::::::::::::::::::::::

77

Computer Arithmetic: Principles, Architectures, and VLSI Design 2

Contents

7.2 Restoring Division

::::::::::::::::::::::::::::::

78

7.3 Non-Restoring Division

::::::::::::::::::::::::::

78

7.4 Signed Division

:::::::::::::::::::::::::::::::::

79

7.5 SRT Division

:::::::::::::::::::::::::::::::::::

80

7.6 High-Radix Division

:::::::::::::::::::::::::::::

81

7.7 Division by Multiplication

:::::::::::::::::::::::

81

7.8 Remainder / Modulus

::::::::::::::::::::::::::::

82

7.9 Divider Implementations

:::::::::::::::::::::::::

83

7.10 Square Root Extraction

:::::::::::::::::::::::::

84

8 Elementary Functions

:::::::::::::::::::::::::::::

85

8.1 Algorithms

:::::::::::::::::::::::::::::::::::::

85

8.2 Integer Exponentiation

:::::::::::::::::::::::::::

86

8.3 Integer Logarithm

:::::::::::::::::::::::::::::::

87

9 VLSI Design Aspects

:::::::::::::::::::::::::::::::

88

9.1 Design Levels

:::::::::::::::::::::::::::::::::::

88

9.2 Synthesis

:::::::::::::::::::::::::::::::::::::::

90

9.3 VHDL

:::::::::::::::::::::::::::::::::::::::::

91

9.4 Performance

::::::::::::::::::::::::::::::::::::

93

9.5 Testability

::::::::::::::::::::::::::::::::::::::

95

Bibliography

::::::::::::::::::::::::::::::::::::::

96

Computer Arithmetic: Principles, Architectures, and VLSI Design 3

sunzhemin2013-04-09很好的算法介绍

sunzhemin2013-04-09很好的算法介绍 我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功