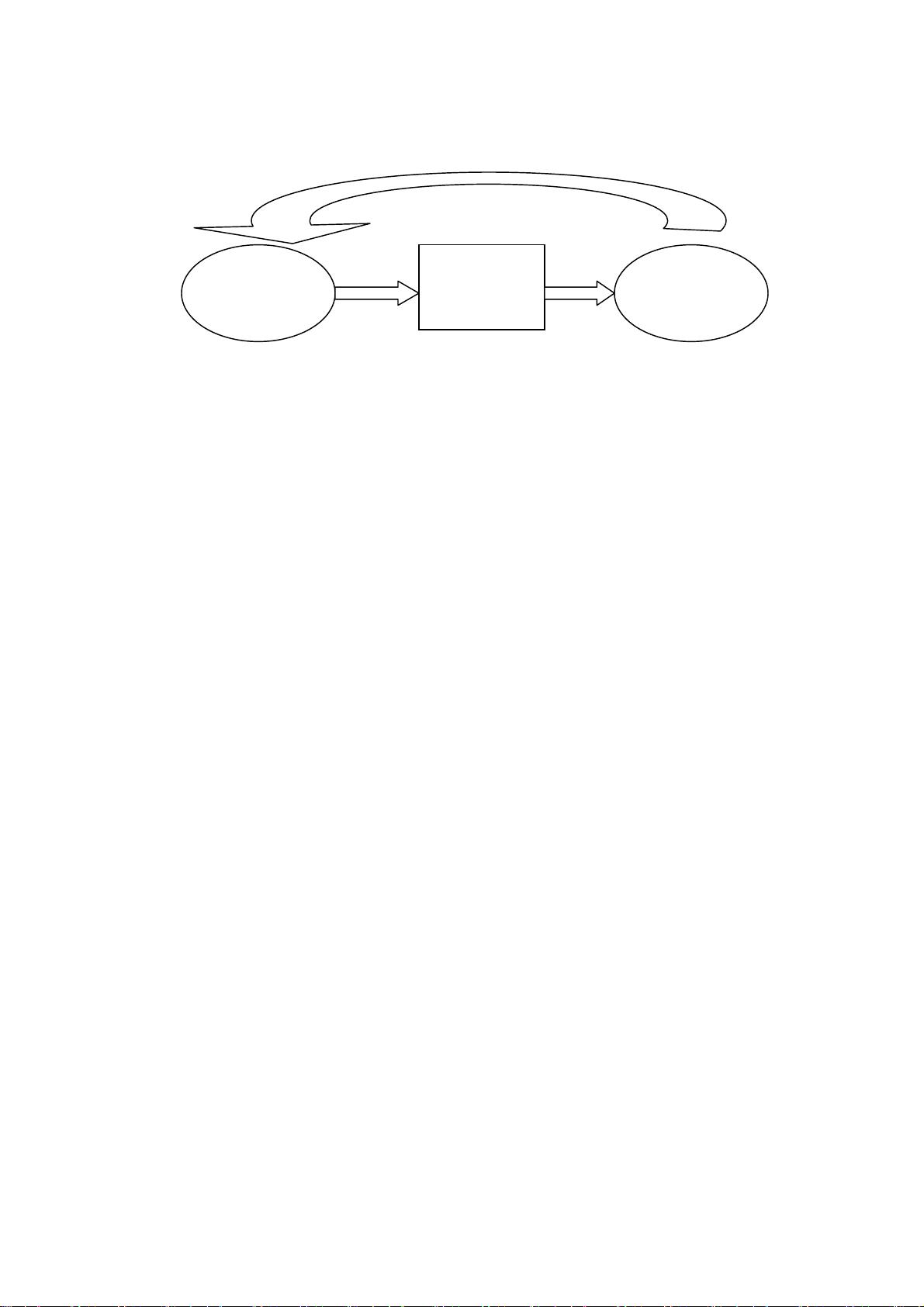

验证与VCS使用 本章节将详细介绍验证与VCS使用相关的知识点。 一、什么是验证 验证是指在设计流程中,确保代码正确、可靠、符合设计要求的过程。验证的目的是找到代码中的错误,不管是编写错误还是功能错误,并尽量多地发现错误。验证在设计中具有非常重要的地位,从设计流程中可以看到,几乎设计工作每前进一步,都要进行验证。 二、验证的等级 验证可以大致分为单独子模块验证、功能模块验证、系统顶级验证。单独子模块验证需要验证它的功能和逻辑是否符合设计要求。功能模块验证需要验证这个模块的功能是否可以满足要求,是否会有非法数据或不该有的输出、错误的状态等。系统顶级验证更关注于系统整体的行为方式、模块间的联系和通讯、总线信号、数据流路径是否满足设计要求、数据处理或时序正确与否等。 三、testbench testbench是一个支持验证的平台,在这个测试平台上,有激励信号产生器、被测模块、响应分析和监测器。testbench可以用Verilog描述语言搭建,也可以用C语言编写,如果用C语言编写,还需要相关的编译器并和与Verilog的接口。 四、VCS的使用方法 VCS的全称是Verilog Compile Simulator,是Synopsys公司的强有力的电路仿真工具,可以进行电路的时序模拟。VCS的工作方式是首先把输入的Verilog源文件编译,然后生成可执行的模拟文件,也可以生成VCD或者VCD+记录文件。然后运行这个可执行的文件,可以进行调试与分析;或者查看生成的VCD或者VCD+记录文件。 五、VCS的简单使用方法 使用VCS进行仿真测试一个模块的大致步骤如下:首先需要编写好模块的Verilog代码。搭建testbench,充分了解被测模块的特性,编写测试向量,输入端口的激励,编写响应分析和监测部分。运行VCS进行模拟,查看输出或者波形。如果发现错误,分析错误类型和原因,修改代码或者修正测试方法,直到符合测试要求。 六、VCS的运行方式 VCS的运行方式有两种,一种是交互模式(interactive mode),一种是批处理模式(batch mode)。交互模式适合测试小模块或者底层模块,情况不太复杂的时候,可以提供详细信息;批处理模式适合进行复杂测试关注于整体性能,而不必去查看每个信号的时候。 七、VCS的简单使用例子 下面是一个简单的使用VCS的例子,模块Monitor & Analyzer Stimulus & Control是一个四位全加器的Verilog代码,存储为add4.v。这个例子展示了如何使用VCS进行仿真测试。

剩余19页未读,继续阅读

- 粉丝: 38

- 资源: 728

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- postman1111

- 快递盒打包机sw18可编辑全套技术资料100%好用.zip

- 画流程图程序的资源包,下载后npm执行就可以

- 基于OOD、JAVA和SWING的足球联赛管理系统软件的设计与实现

- 冷却收卷生产线(sw18可编辑+工程图+bom)全套技术资料100%好用.zip

- 雷达主板测试设备sw19可编辑全套技术资料100%好用.zip

- 龙门桁架sw18可编辑全套技术资料100%好用.zip

- 流水线贴标机sw18全套技术资料100%好用.zip

- 链式传输带sw18可编辑全套技术资料100%好用.zip

- CrystalDiskInfo可检测固态硬盘NAND写入量

- 龙门架双机械手sw18可编辑全套技术资料100%好用.zip

- SSD系列X2.zipSSD系列X2.zip

- 闪迪SSD管理工具Dashboard-V2.3.1.0.zip

- 龙门架快递搬运机器人sw18全套技术资料100%好用.zip

- 闪迪SSD工具Dashboard-v3.2.2.9.zip

- 计算机网络实验报告:使用Wireshark嗅探来自两个HTTP网站的数据包

信息提交成功

信息提交成功