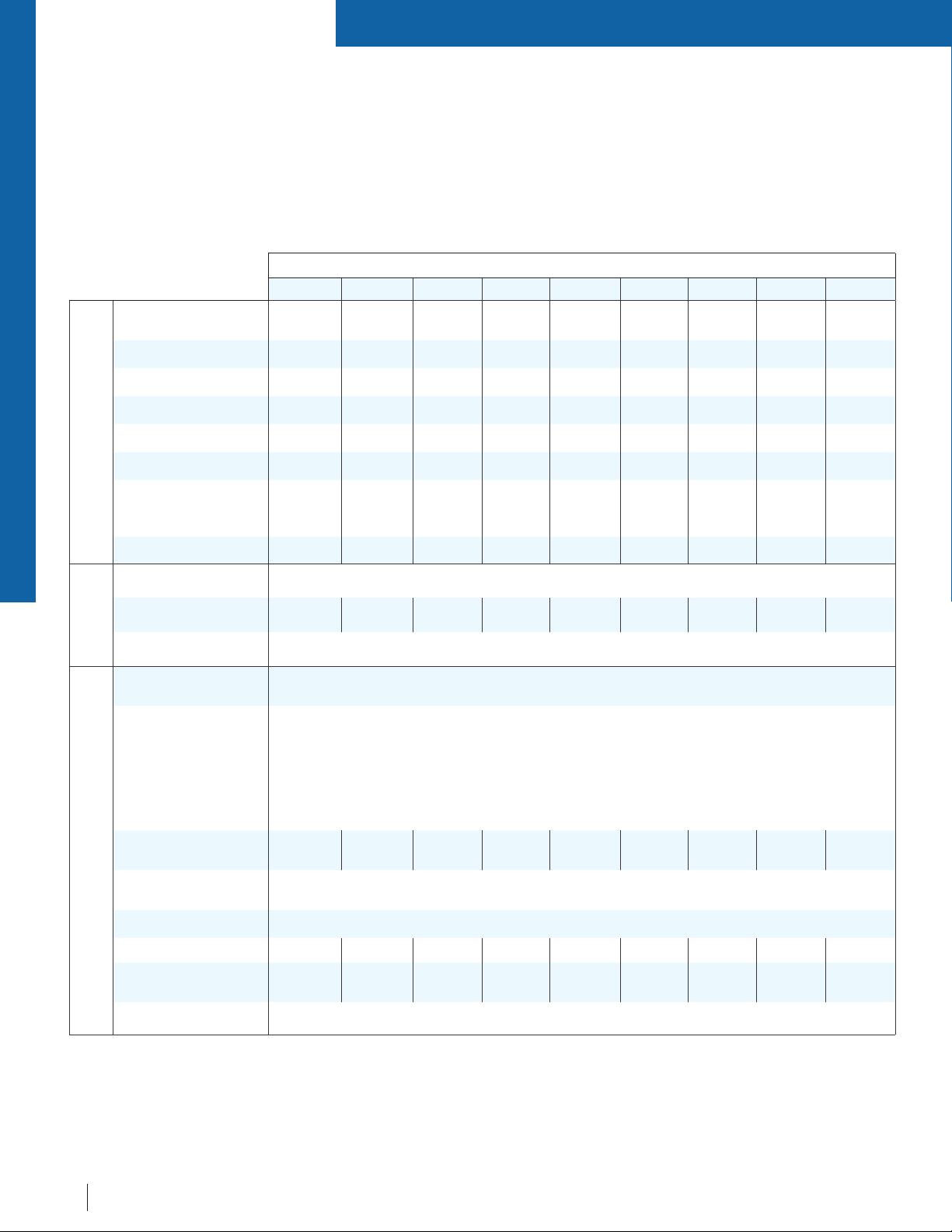

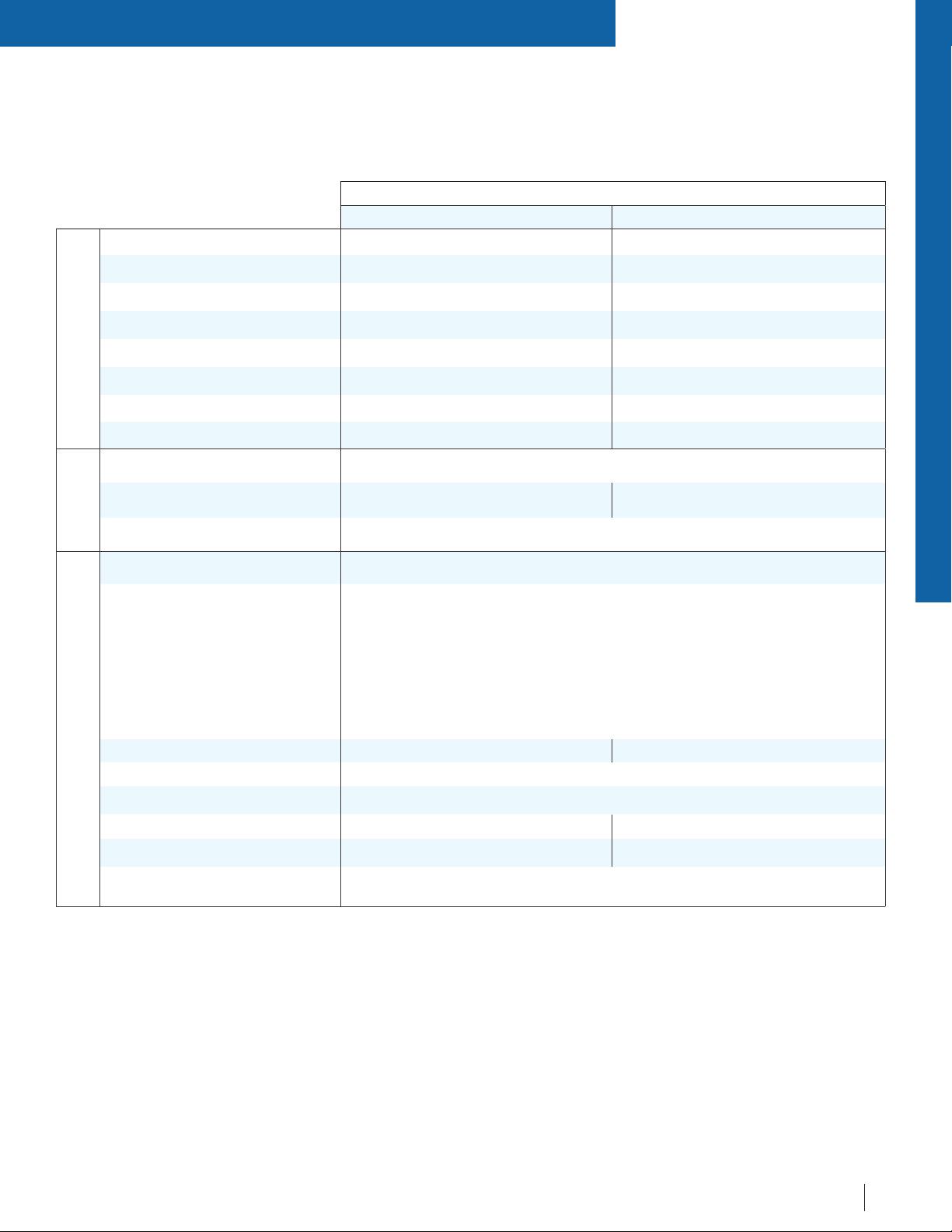

根据给出的文件信息,我们可以得到以下知识点: 1. 器件选型:文件提到的Altera器件选型主要指FPGA(现场可编程门阵列)、CPLD(复杂可编程逻辑器件)以及配置器件的选择。这是一个涉及到硬件设计与系统集成的关键步骤,设计者需要根据项目需求、性能标准、成本预算等因素综合考虑,选择最合适的器件。 2. Altera公司及产品介绍:Altera现在是英特尔(Intel)旗下的一个部门,提供业界领先的可编程逻辑解决方案。Altera的解决方案组合包括FPGA、SoC(系统级芯片)、CPLD等,以及软件工具、IP(知识产权)、嵌入式处理器、客户支持和技术培训。 3. FPGA技术:FPGA为可编程逻辑器件,提供了高度灵活性与可定制性。文件提到的FPGA分为三个类别: - 高端FPGA:具备最高密度和性能,适用于性能要求极高的市场领域。 - 中端FPGA:提供了成本、功耗和性能的平衡。 - 低成本低功耗FPGA:系统成本和功耗最低,适用于成本敏感型应用。 4. SoC技术:SoC(System on Chip)技术将FPGA的功能与硬处理器系统(HPS)集成在同一芯片上。这样可以减少系统功耗、成本和电路板面积,同时提高性能。Altera的SoC通常集成了基于ARM的处理器核心,配备外设和内存控制器,并通过高速互联骨架与FPGA逻辑相连接。 5. CPLD技术:与FPGA不同,CPLD是复杂可编程逻辑器件,具有固定的逻辑块和可编程互连,适用于逻辑较为固定的场合,相对于FPGA有成本更低、功耗更小的优势。 6. 配置器件:配置器件用于存储FPGA或CPLD的配置信息,当设备上电时,配置器件通过将配置数据加载到可编程逻辑器件中来初始化或重配置器件。 7. 软件工具和嵌入式处理:Altera提供一系列设计软件和开发工具,包括Quartus II软件、Altera SDK for OpenCL™、SoC嵌入式设计套件等,以便于用户能够设计和开发基于Altera器件的应用程序。 8. 可编程逻辑器件的市场应用:Altera的FPGA和SoC广泛应用于数据通信、广播、测试设备、航空航天、军事、工业、消费电子以及汽车等众多领域。 9. 技术支持和培训:Altera提供丰富的技术支持和培训资源,包含在线培训、虚拟和现场授课课程等,帮助设计人员提升设计能力,缩短产品上市时间。 10. 产品和服务的持续更新:Altera不断推陈出新,发布最新产品和服务。2014年发布的14.0版本产品目录介绍了当时可用的全系列Altera产品,包括不同工艺节点的设备组合以及相关的软件和开发工具套件。 了解这些知识点可以帮助IT专业人士更好地进行Altera器件的选型、设计、开发和应用,充分发挥Altera可编程逻辑器件在各自领域中的优势。

剩余95页未读,继续阅读

chenwei9992014-10-21还不错,新的

chenwei9992014-10-21还不错,新的

- 粉丝: 5

- 资源: 15

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功