omyligaga

- 粉丝: 97

- 资源: 2万+

最新资源

- 基于ssm的学生综合测评管理系统源码(java毕业设计完整源码+LW).zip

- 基于ssm的理发店管理系统源码(java毕业设计完整源码+LW).zip

- 不同颜色字母标记检测15-YOLO(v5至v11)、COCO、CreateML、Paligemma、TFRecord、VOC数据集合集.rar

- 永磁同步电机PMSM负载状态估计(龙伯格观测器,各种卡尔曼滤波器)矢量控制,坐标变,永磁同步电机负载转矩估计、PMSM负载转矩测量、负载预测、转矩预测的MATLAB simulink仿真模型,模型包可

- 基于ssm的美容院管理系统源码(java毕业设计完整源码+LW).zip

- 一种萃盘叠放上料设备sw18可编辑全套技术资料100%好用.zip

- 一种包胶前后整平设备sw18可编辑全套技术资料100%好用.zip

- PLC随机密码 动态验证码 动态分期付款 锁机例程 这次是信捷Plc例程 只供参考算法学习,详细功能看下图介绍 学会信捷基本也能自己改为日系PLC(三菱台达等等)本次配送对应信捷触摸屏简单界面,如

- 基于ssm的面向学生成绩分析系统源码(java毕业设计完整源码+LW).zip

- 一种产线开治具下料设备sw18可编辑全套技术资料100%好用.zip

- 基于ssm的网上电子书店源码(java毕业设计完整源码+LW).zip

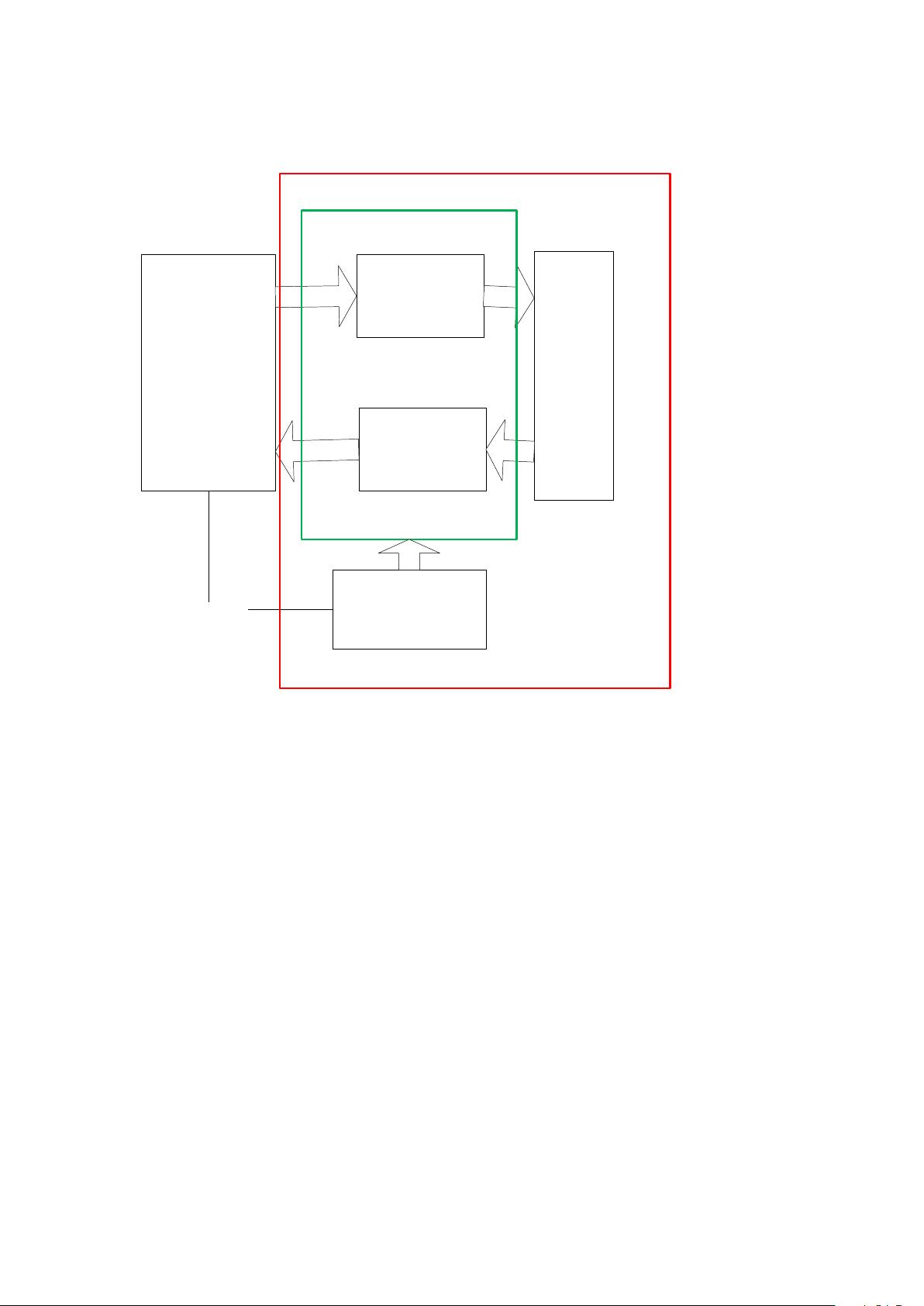

- LIV-handhold

- PLC 西门子smart200 锁机 最新原创有图片证明配对应西门子smart700IE V3程序,分期期付款 动态验证码,无限次加密 程序例程

- 基于ssm的物业管理系统源码(java毕业设计完整源码+LW).zip

- QT,mingw集成IntelRealSense双目摄像头,完整项目代码

- 基于python的充电桩协议解析工具-根据充电桩与电动汽车通信协议(国标)+用支持其中常用的二十来种协议解析

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈