没有合适的资源?快使用搜索试试~ 我知道了~

基于FPGA的小数分频器设计.doc

1.该资源内容由用户上传,如若侵权请联系客服进行举报

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

版权申诉

0 下载量 45 浏览量

2023-06-20

15:31:15

上传

评论

收藏 278KB DOC 举报

温馨提示

试读

38页

基于FPGA的小数分频器设计.doc

资源推荐

资源详情

资源评论

1

第 1 章 本课题内容

频率合成技术是现代通讯系统的重要组成部分,是对一个高精度和高稳定度的基准

频率进行加、减、乘、除四则运算,产生具有同样稳定度和基准度的频率。分频器是数

字逻辑电路设计中经常使用的一个基本电路。通常,整数分频可以很容易地用计数器或

状态机来实现。但在某些场合下,时钟源与所需要的频率并不成整数关系,此时便需要

采用小数分频器进行分频。

一般来说,小数分频电路可以分为半整数分频电路和非半整数分频电路两类。对于

小数分频的 FPGA 设计,目前广泛采用的方法是双模前置小数分频,以及一种由双模前

置小数分频改进而得到的小数分频——用一个半整数分频器和一个整数分频器代替双

模前置小数分频中的两个整数分频器。虽然这两种方案输出时钟的占空比误差和抖动性

能方面有所差别,但其工作原理却是一致的。双模前置小数分频器在理论上可以实现任

意小数分频。但在实际的电路设计中,不可能真正实现任意小数分频。小数分频器的精

度受控制计数器的影响,而控制计数器的设计会受硬件资源的限制,尽管 FPGA 有相当

丰富的硬件资源。另外,基于 FPGA 实现的双模前置小数分频器在两个整数分频时钟之

间的切换点上,有时候会出现毛刺,而时钟是不应该有毛刺存在的。此时,就要结合脉

冲删除技术,设计出一种可以进行任意小数分频且不会出现毛刺的小数分频方案,并通

过编程实现。本文利用 VHDL 硬件描述语言的设计方式,通过 MAXPLUS II 开发平台,

使用 Altera 公司的 FPGA 器件,设计并实现了一种不同占空比的任意小数分频器。

2 小数分频的基本原理

假设时钟源的频率为 f

0

,期望得到的频率为 f

1

,则其分频比 X 为:

X=

1

0

f

f

(式

1-1)

其中,X>1。

若 M<X<M+1,M 为整数,则有

X=M+

21

2

NN

N

�

=

21

21 )1(

NN

NMNM

�

����

(式

1-2)

2

其中,N

1

和 N

2

均为整数。当 N

1

和 N

2

取不同的正整数时,从

)( 21

2

NN

N

�

可以得到任意一

个小数,就可以从理论上实现任意小数分频比的分频。由于 0

�

�

�

�

��

1

2

i

i

ia

1�

,(a

i

=0,

1),所以从工程的角度可以进一步构造出下列关系:

21

2

NN

N

�

=

�

�

�

�

�

1

2

i

i

ia

(式 1-3)

式 1-3 有明确的物理意义,它的右边实际上是个多位累加器。例如,要把 13MHz 的时

钟信号分频为 8MHz 的时钟信号,则

21

2

NN

N

�

=

�

�

�

�

�

1

2

i

i

ia

=0.625,a

1

=1,a

2

=0,a

3

=1。显

然,当分频比 X 为无限小数时,例如把 13MHz 的时钟信号分频为 11MHz 的时钟信号

时,x=1.18181818…,此时,尽管在理论上可以设计这样的多位累加器,但在实际电路

中却是不可实现的。因此,实际所设计的小数分频器的分频比,有时候与实际期望得到

的分频比存在一个微小的偏差;当分频器长时间工作,就会导致累计误差。

利用脉冲删除电路,有规律地删除时钟源中的一些脉冲,从而实现平均意义上的小

数分频。在硬件电路的设计过程中,利用脉冲删除电路,就不会出现上述竞争冒险和毛

刺的问题,而且可以很容易地用硬件实现任意小数分频。

吞脉冲原理:吞脉冲电路通过小数分频器实现吞食脉冲的功能。在脉冲传输信道上

增加一个脉冲删除控制器,脉冲删除器在适当的时候吞掉一个脉冲,脉冲删除时机的选

择受脉冲删除控制器的控制。

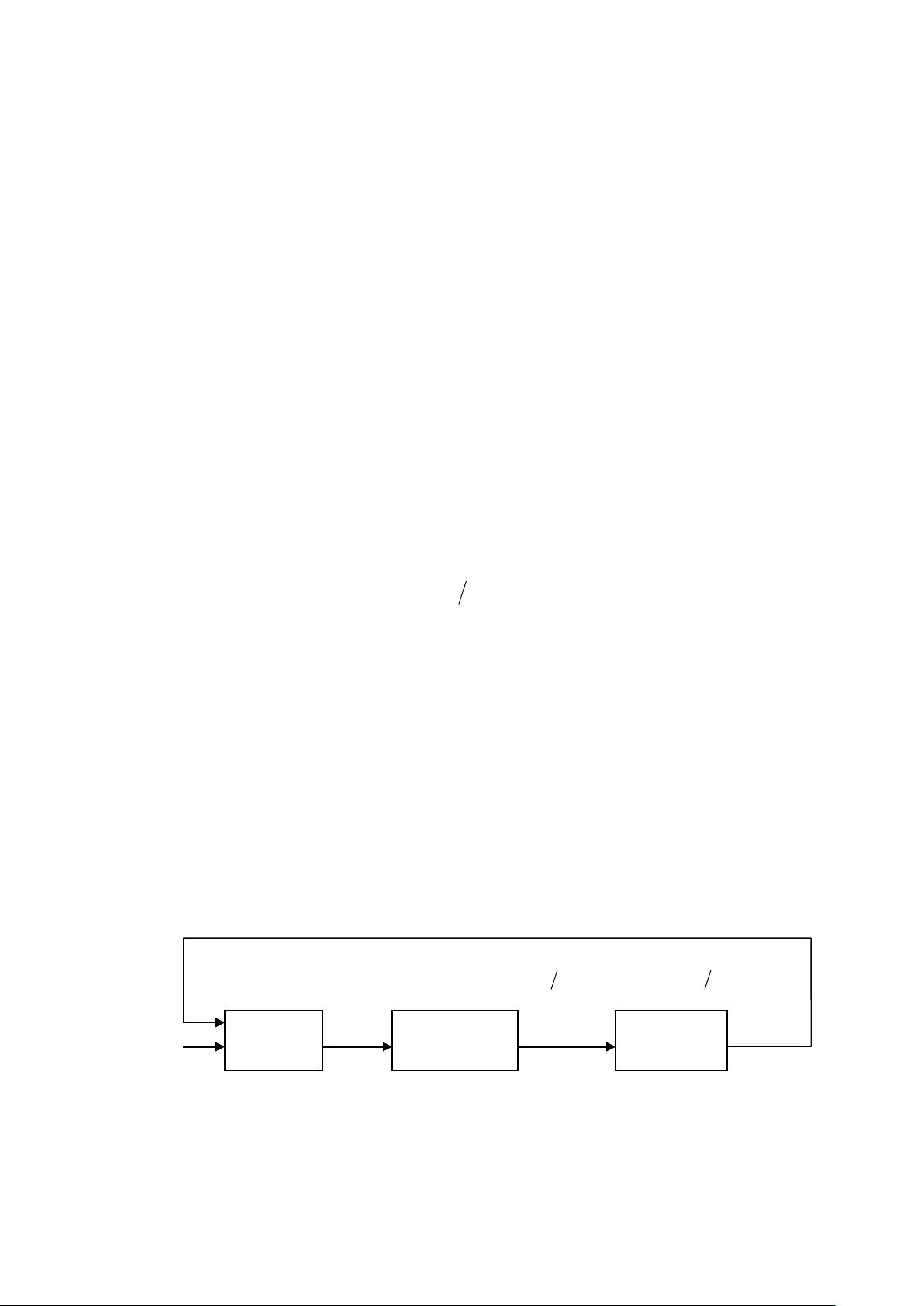

图 1.1 给出了脉冲删除电路原理。该电路主要由三部分组成:n 倍频计数累加器、

余数发生器和脉冲删除控制器。

图 1.1 脉 冲 删 除 原 理

输出脉冲

溢出脉冲

n 倍计数累加器

余数发生器

脉冲删除控制器

步进预置

基频 f

r

3

电路工作原理:首先设置 n 倍频计数累加器的模 m,在输入基频 f

r

的作用下,每来

一个基频脉冲 f

r

,n 倍频计数累加器就加 n。当计数值大于计数器的模 m 时,就产生一

个删除脉冲,并传送给脉冲删除控制器。从而实现了脉冲删除。

设有一个 5MHz 时钟源,但电路中需要产生一个 2MHz 的时钟信号,由于分频比为

2.5,因此整数分频器将不能胜任。

采用可变成逻辑器件实现分频系数为 2.5 的分频器,可采用以下方法:设计一个模

3 的计数器,再设计一个扣除脉冲电路,加在模 3 计数器输出之后,每来两个脉冲就扣

除一个脉冲,就可以得到分频系数为 2.5 的小数分频器。采用类似的方法,可以设计分

频系数为任意半整数的分频器。

小数分频的基本原理是:采用脉冲吞吐计数,设计两个不同的分频比的整数分频器,

通过控制单位时间内两种分频比出现的不同次数,从而获得所需的小数分频值。例如,

设计一个分频系数为 8.7 的分频器,可以将分频器设计成 3 次 8 分频,7 次 9 分频,这

样总的分频值为:

7.8)73()9783( �����

从这种实现方法的特点可以看出,由于分频器的分频值在不断改变,因此分频后得

到的信号抖动大。

当分频系数为

5.0�N

(N 为整数)时,可控制扣除脉冲的时间,使输入为一个稳定

的脉冲频率,而不是一次 N 分频,一次 N-1 分频。

3 本课题实现方法

本课题以 CPLD/FPGA 作为可编程 ASIC 器件。其电路可由一个模 N 计数器、二分频

器和一个异或门组成。如图 1.2 所示。

最后结果可通过 VHDL 程序,在 MAX+PLUS II 环境中进行仿真。

异或门

模 N 计数器

2 分频器

)5.0(

0

�Nf

)12(

0

�Nf

图 1.2 通用半整数分频器电路

组成

4

第 2 章 开发环境

1 电子系统设计与 ASIC 技术

随着 21 世纪的到来,人类正跨入信息时代。从计算机到移动电话,从家用无了使

用的 VCD、HDTV、多媒体电脑到军用雷达、医用 CT 仪器等设备,无不由各种各样的电子

系统组成。在这些电子系统中,数字化技术的应用比比皆是。由于数字技术在处理和传

输信息方面的各种优点,数字技术与数字集成电路的使用已经成为后成现代电子系统的

重要标志。

1.1 电子系统的设计方法

现代电子系统一般由模拟子系统、数字子系统和微处理器子系统三大部分组成。从

概念上讲,凡是利用数字技术处理和传输信息的电子系统都可以称为数字系统。像其他

电子系统一样,数字系统以往是采用传统的搭积木式的方法进行设计,即由器件搭成电

路板,由电路板搭成电子系统。数字系统最初的“积木块”是木顶功能的标准集成电路。

用户只要根据需要选择合适的器件,并按照器件推荐的电路搭成系统。在设计时,设计

者几乎没有灵活性可言,搭成的电子系统所需的芯片种类多且数目大。

随着半导体技术、集成技术和计算机技术的发展,电子系统的设计方法和设计手段

发生了很大的变化。特别是进入到 20 世纪 90 年代以后,EDA 技术的发展和普及给电子

系统的设计带来了革命性的变化,并已渗透到电子系统设计的各个领域。

在半导体技术方面,可编程技术被广泛地应用到器件的设计上,给数字系统的设计

带来了很大的灵活性。传统的数字系统设计只能对电路板进行设计,通过设计电路板来

实现系统功能。利用 EDA 工具,采用可编程器件,通过设计芯片来实现系统功能,这种

方法称为基于芯片的设计方法。新的设计方法能够由设计者定义器件的内部逻辑和管脚,

将原来由电路板设计完成的大部分工作放在芯片的设计中进行。这样不仅可以通过芯片

设计实现多种数字逻辑系统功能,而且由于管脚定义的灵活性,大大减轻了电路图设计

和电路板设计的工作量和难度,从而有效地增强了设计的灵活性,提高了工作效率。同

时,基于芯片的设计可以减少芯片的数量,缩小系统体积,降低能源消耗,提高系统的

性能和可靠性。

5

可编程逻辑器件和 EDA 技术给今天的硬件系统设计提供了强有力的工具,使得电子

系统的设计方法发生了质的变化。传统的“固定功能集成块+连续”的设计方法正逐步

地退出历史舞台,而基于芯片的设计方法正在成为现代电子系统设计的主流。现在,只

要拥有一台计算机、一套相应的 EDA 软件和空白的可编程逻辑器件芯片,在实验室就可

以完成数字系统的设计和生产。可以说,当今的数字系统设计已经离不开可编程逻辑器

件和 EDA 设计工具。

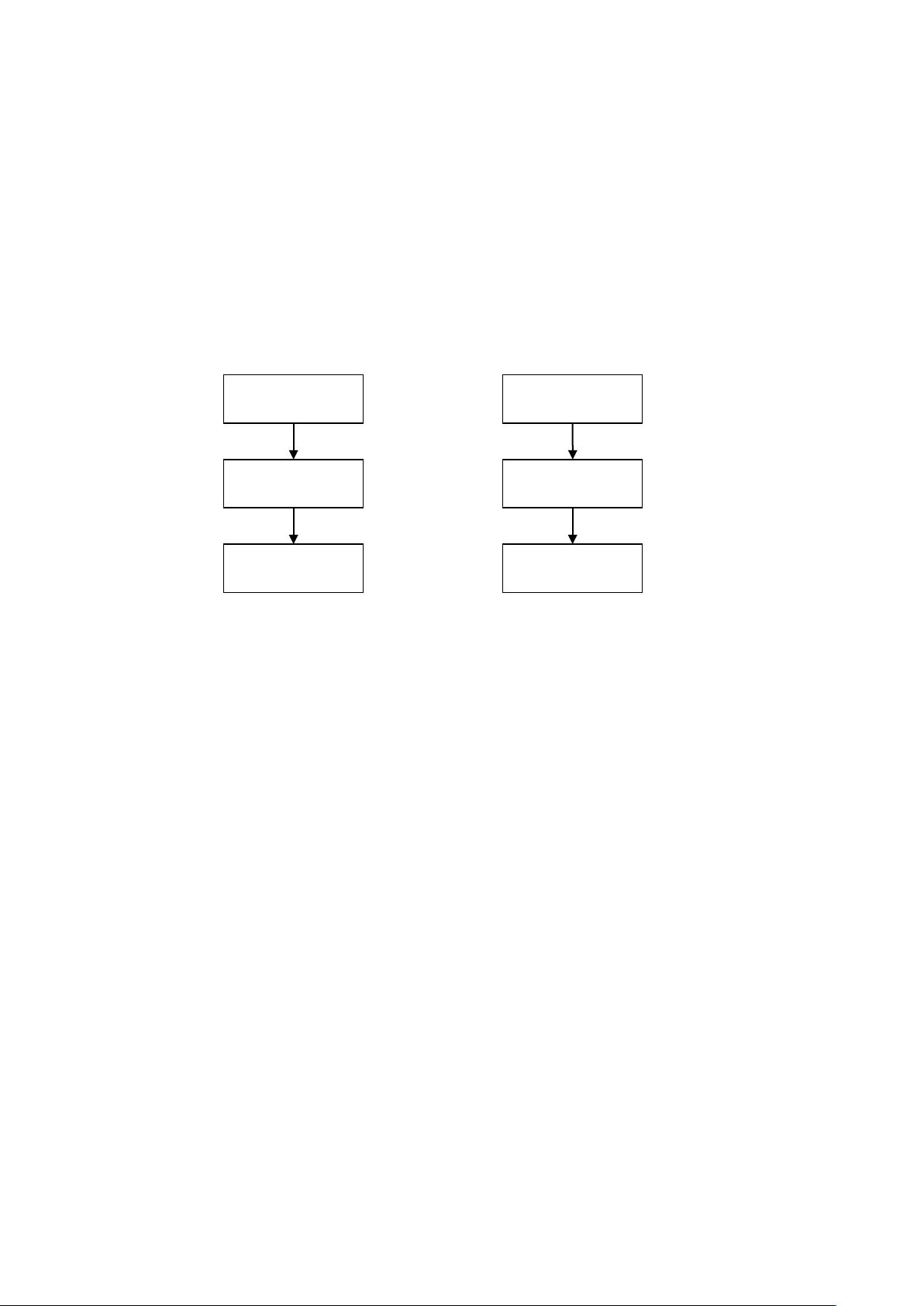

图 2.1 所示为电子系统的传统设计方法和基于芯片的设计方法。

“自顶向下” 与“自底向上”设计方法:

近 10 年来,电子系统的设计方法发生很大的变化。过去,电子产品设计的基本思

路一直是先选用标准通用集成电路芯片,再由这些芯片和其他元件自下而上地构成电路、

子系统和系统。这些设计出的电子系统所用元件的种类和数量均较多。体积与功耗大,

可靠性差。随着集成电路技术的不断进步,现在人们可以把数以亿计的进体管,几万门、

几十万门、甚至几百万门的电路集成在一块芯片上。半导体集成电路已由早期的单元集

成、部件电路集成发展到整机电路集成和系统电路集成。电子系统的设计方法也由过去

的那种集成电路厂家提供通用芯片,整机系统用户采用这些芯片组成电子系统的“自底

向上”设计方法改变为一种新的“自顶向下”的设计方法。在这种新的设计方法中,由

整机系统用户对整个系统进行方案设计和功能划分,系统的关键电路用一片或几片专用

集成电路 ASIC 来实现,且这些专用集成电路是由系统和电路设计师亲自参与设计的,

直至完成电路到芯片版图的设计,再交由 IC 工厂投片加工,或者是用可编程 ASIC 现场

编程实现。

固定功能元件

电路板设计

电子系统

可编程器件

芯片设计

电子系统

(a) 传统设计方法

(b)基于芯片的设计方法

图 2.1 电子系统的设计方法

剩余37页未读,继续阅读

资源评论

oligaga

- 粉丝: 50

- 资源: 2万+

下载权益

C知道特权

VIP文章

课程特权

开通VIP

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功