简易数字存储示波器设计设计.doc

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

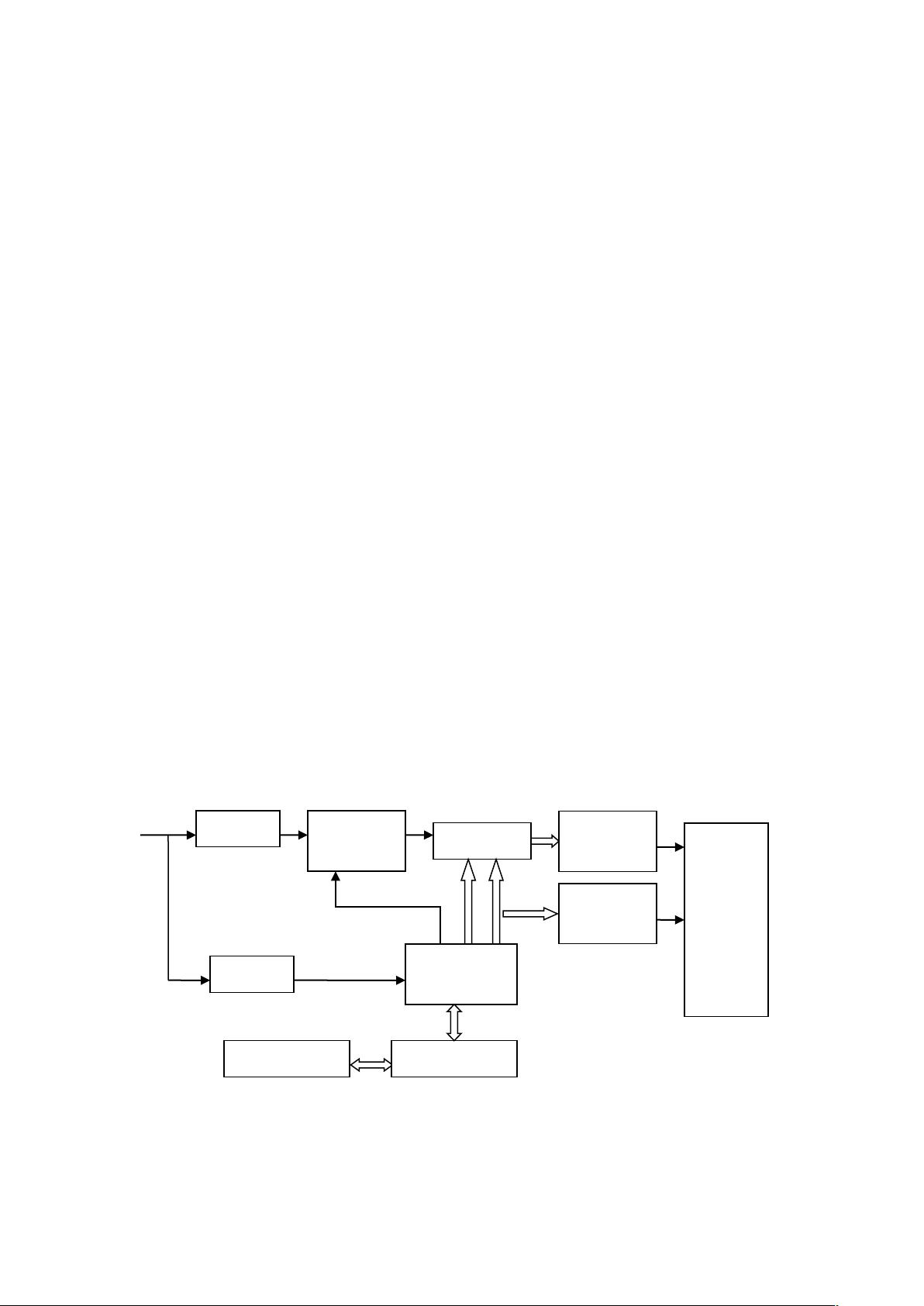

"简易数字存储示波器设计设计" 该简易数字存储示波器的设计是介绍基于 FPGA 高速数据实时采集与存储、显示技术,采用 FPGA 中的 A/D 采样控制器负责对 A/D 模拟信号的采样控制,并将 A/D 转换好的数据送到 FPGA 的内部 RAM 中存储;RAM 的地址信号由地址发生计数器产生。 在该设计中,ADC0809 芯片作为高速信号的 A/D 转换,SRAM6264 存储器作为采样后数据的存储,DAC0832 芯片作为信号的 D/A 转换。程序设计采用超高速硬件描述语言 VHDL 描述,对其 A/D 转换、A/D 采样控制器及数据的存储、数字输出进行编程、仿真,完成硬件和软件的设计,以及实验样机的部分调试。 该设计的主要特点是采用 FPGA 高速数据实时采集与存储、显示技术,能够实时采集和存储高速信号,并将其显示出来。同时,该设计还具有灵活性强、扩展性好、可靠性高等优点,能够满足不同的应用需求。 在该设计中,A/D 采样控制器是整个系统的核心组件,负责对 A/D 模拟信号的采样控制,并将其转换为数字信号。A/D 转换后的数据将被送到 FPGA 的内部 RAM 中存储,并由地址发生计数器产生的地址信号来控制数据的存储和读取。 在该设计中,还使用了 SRAM6264 存储器作为采样后数据的存储,能够快速存储和读取大量的数据。同时,DAC0832 芯片作为信号的 D/A 转换,能够将数字信号转换为模拟信号,显示在示波器上。 该简易数字存储示波器的设计是基于 FPGA 高速数据实时采集与存储、显示技术,能够实时采集和存储高速信号,并将其显示出来。该设计具有灵活性强、扩展性好、可靠性高等优点,能够满足不同的应用需求。 在该设计中,程序设计采用超高速硬件描述语言 VHDL 描述,对其 A/D 转换、A/D 采样控制器及数据的存储、数字输出进行编程、仿真,完成硬件和软件的设计,以及实验样机的部分调试。 在该设计中,VHDL 语言是一种基于事件驱动的硬件描述语言,能够对数字电路进行描述和仿真。该语言具有强大的描述能力和灵活性强的特点,能够满足复杂的数字电路设计需求。 在该设计中,使用 VHDL 语言对 A/D 转换、A/D 采样控制器及数据的存储、数字输出进行编程、仿真,能够快速地完成硬件和软件的设计,并且能够对系统进行仿真和调试,从而提高设计的效率和可靠性。 该简易数字存储示波器的设计是基于 FPGA 高速数据实时采集与存储、显示技术,采用 FPGA 中的 A/D 采样控制器负责对 A/D 模拟信号的采样控制,并将 A/D 转换好的数据送到 FPGA 的内部 RAM 中存储。该设计具有灵活性强、扩展性好、可靠性高等优点,能够满足不同的应用需求。

剩余36页未读,继续阅读

- 粉丝: 100

- 资源: 2万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于滑模观测器(SMO)的电池SOC估计Simulink仿真模型:多工况下的参数估计与比较,基于滑模观测器(SMO)的电池SOC估计Simulink仿真模型 主要内容: 1)Simulink模型:锂铅

- 基于NSGAII遗传算法的MATLAB 7次非均匀B样条轨迹规划:时间、能量、冲击最优化解决方案,matlabB样条轨迹规划,7次非均匀B样条轨迹规划,基于NSGAII遗传算法,实现时间 能量 冲击最

- 人工势场法路径规划:碰撞检测与航向调整的船舶危险度计算方法,人工势场法路径规划 可以找到碰撞点,复航点,计算船舶危险度,两船之间的距离,船的方向变化 ,核心关键词:人工势场法; 路径规划; 碰撞点

- 直流电机转速与电流双闭环控制的Simulink仿真研究,直流电机转速电流双闭环控制simulink仿真 ,核心关键词:直流电机;转速控制;电流控制;双闭环控制;Simulink仿真;,"直流电机转速电

- MATLAB SIMULINK下的MMC整流器仿真:双闭环控制与载波移相调制策略,实现PI控制电容电压均衡与多电平端口相电压调节(学习参考),MATLAB SIMULINK,MMC整流器仿真,双闭环控

- DAB转换器与DPS控制的变压器变比调节技术:输入200V电压转换至输出24V,开关频率达50kHz,DAB DPS控制 输入200V 输出24V 变压器变比5:1 开关频率50k ,核心关键词:DA

- 考虑风电不确定性的电力系统潮流计算研究:策略与方法探讨,考虑风电不确定性的电力系统潮流计算 ,核心关键词:风电不确定性; 电力系统; 潮流计算; 影响因素分析 ,"电力系统潮流计算:应对风电不确定性

- 融合多种改进策略的ISCSO沙丘猫群优化算法:性能评估与对比分析,改进沙丘猫群优化算法(2022年新算法,ISCSO),目前对这个算法的改进较少,融合了多种改进策略,效果比较理想 对比算法:与基础北

- COMSOL超声无损tfm与saft全聚焦模型介绍:压力声学与固体力学仿真,自定义参数,一键激发接收,波形成像对比,6.0版本及以上适用 ,COMSOL超声无损tfm,saft,全聚焦,合成孔径模型

- 高性能MQTT C#开源框架,自主开发无限制无版权约束,单节点支持百万并发,c# mqtt高性能服务器端源代码 你还在找免费的吗?你还在找便宜的吗?你还在使用第三方服务软件吗?不如试试这个开发框架

- 模拟IC设计:Pipeline ADC仿真测试,基于10bit 100MHz精度,搭载完整Testbench与虚拟机,适合初学者入门学习,采用0.18um工艺实现有效位9.5bit,模拟ic设计,10

- 三电平T型变换器双闭环PI控制:高效调制实现与矢量计算优化在60度坐标系下的探讨,三电平T型变器双闭环PI控制-调制实现在60度坐标系 变器 减少了普通SVPWM的矢量计算时间,在60度坐标系完成高效

- "TSMC 28nm器件库全面解析:高效仿真助力设计与性能优化",tsmc28nm器件库,可仿真 ,tsmc28nm器件库; 可仿真,"TSMC 28nm器件库:实现可仿真高精度集成电路设计"

- 单相PET电力电子变压器:PWM整流器双闭环控制输入级与开关频率达10kHz,中间级移相全桥输出500V,输出级单相逆变器输出交流电 ,单相PET电力电子变压器 输入级单相pwm整流器双闭环控制 输出

- 分班.exe (pyqt6)

- 碱性水电解槽中的气液两相流模拟:氢气在KOH溶液中的积聚现象研究-基于fluent与comsol软件的模拟学习,碱性水电解槽气液两相流模拟,模拟氢气在KOH溶液中运动积聚现象,软件采用fluent或

信息提交成功

信息提交成功