没有合适的资源?快使用搜索试试~ 我知道了~

嵌入式脉象采集仪电路设计 电子技术.doc

1.该资源内容由用户上传,如若侵权请联系客服进行举报

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

版权申诉

0 下载量 43 浏览量

2022-06-13

02:17:03

上传

评论

收藏 163KB DOC 举报

温馨提示

试读

4页

嵌入式脉象采集仪电路设计 电子技术

资源推荐

资源详情

资源评论

嵌入式脉象采集仪电路设计

FPGA 采集

摘要:该脉象 FPGA 内部,并自主进行了脉象采集控制的 FPGA 设计。该设计采用在

SoPC 系统外做控制电路部分,三路脉搏信号共用一个 ADC,只需要很少的外部器件就能实

现。与早期采用工控机、PC 机,或者现在多采用的 ARM 设计方法相比,该脉象采集仪具有

成本低,功耗低,体积小,便于扩展,稳定性高和系统维护方便等优点。

关键词:脉象采集;FPGA;IP 核;嵌入式系统

脉诊作为中医最重要的一种诊断方式,具有模糊性、不确定性的特点,是近年来中

医现代化研究中的热点。随着电子、计算机技术的快速进步,将嵌入式技术、 FPGA 技术、

IP 核技术结合在一起,融合电子技术、信号处理方法等学科知识,在中医基本理论的指导下,

设计脉象诊断设备,构建一个灵活高效,可扩展性强,可靠性高,功耗低,可便携的脉象采

集仪具有重要的现实意义和良好的市场前景。

1 仪器总体设计

嵌入式脉象采集仪的前期设计目标是脉搏信号的采集、存储、显示、简单处理、通

信等,后期要对所采集到的信号处理,得到脉象特征,对病人做出诊断。在 FPGA 的选型时,

不但要考虑当前功能是否够用,价格适中,而且要考虑产品的升级换代,所以设计的系统选

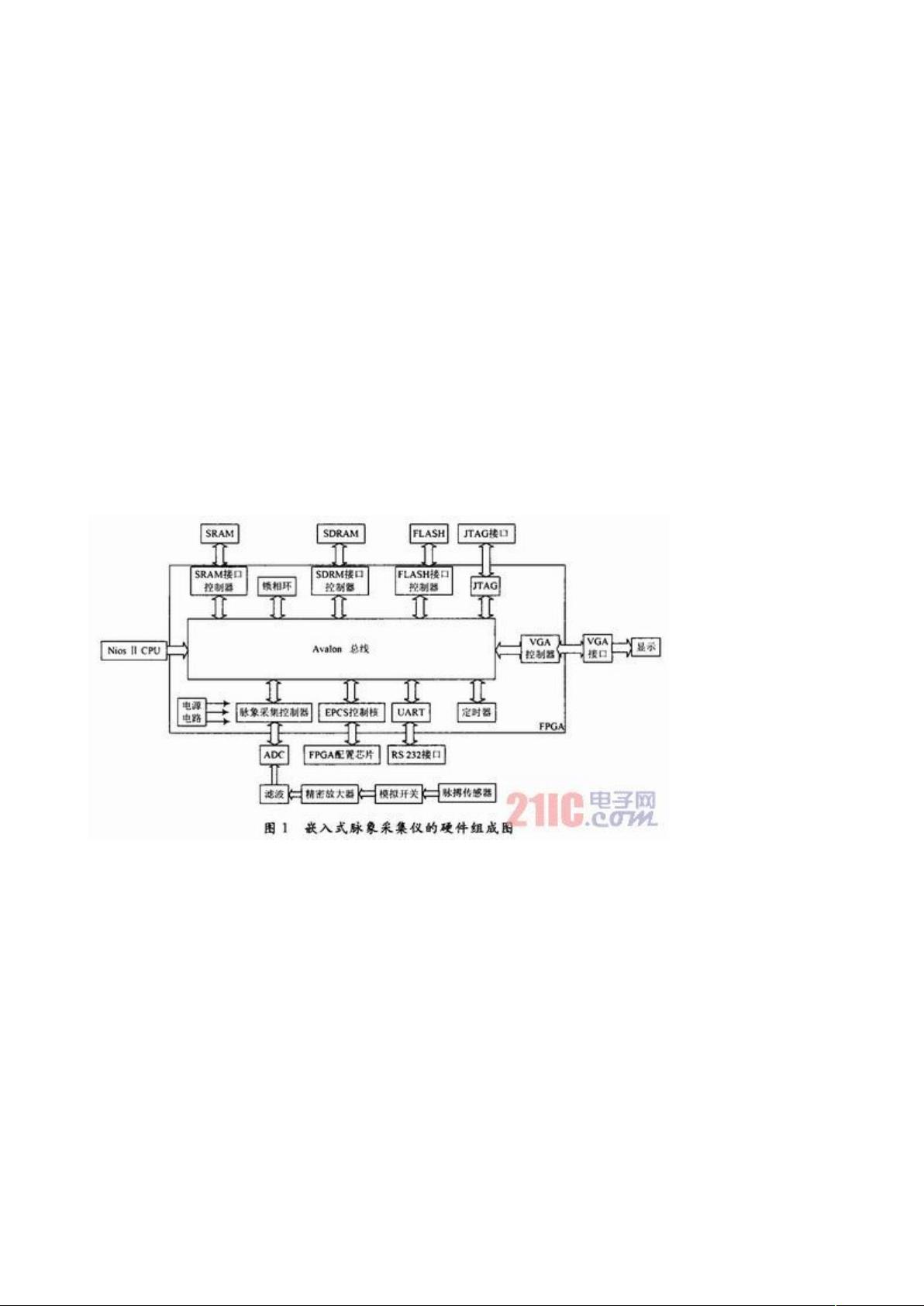

择 Alt-era 公司 Cyclone II 系列 EP2C35F484C8 作为核心芯片。以 FPGA 芯片为核心的嵌入式

脉象采集仪的结构组成如图 1 所示。从图 1 中可以看出,硬件主要由电源、显示、存储器、

脉象采集、FPGA、通信等 6 个模块组成。

2 主要外围电路设计

由于在 FPGA 内部采用 VGA 控制器 IP 核,选择模拟仪器公司的 10 位高速视频 DAC

芯片。

SRAM 采用 IDT 公司的 IDT71V416 器件,利用 2 片 IDT71V416 器件构成 32 位存储

器,以与 NiosⅡ 的 32 位 CPU 的总线匹配。对 SRAM 的控制,选用 Altera 公司提供 SRAM 控

制器核,其控制信号由 SoPC 自动生成。SDRAM 为系统中的数据及堆栈提供暂存空间。系

统启动后,程序代码调入 SDRAM 中运行,以提高系统的运行速度。系统中采用 HYNIX 公

司的 64 MB SDRAM,型号为 HY57V561620HT。它提供 LVTTL 接口,分为 4 个 BANK,每

个 BANK 容量为 4 M

times;16 b。由 BA0,BA1 的状态决定选定那个 BANK。FLASH 存储器的设计采用 AMD

公司的 AM29LV128M 器件。可以自由选择数据的位数为 16 b 或者 8 b,但是最高位是模式

位,采用 IP 核完成设计,具有比较优越的性能。

2.1 通信模块的设计

采用非常普遍的串行口通信。RS 232 串行总线具有结构简易,成本低廉,硬软件支

持丰富,安装方便等特点。虽然 RS 232 的速度稍微慢了点,但是对于频率小于 100 Hz 信号

的采集还是足能满足的。采用 MAXIM 公司的 max3232 作为串口转换芯片,其供电电压为 3

~5V,速度可以达到 1 Mb/s,具有良好的性能。

资源评论

oligaga

- 粉丝: 50

- 资源: 2万+

下载权益

C知道特权

VIP文章

课程特权

开通VIP

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功