没有合适的资源?快使用搜索试试~ 我知道了~

51,单片机,IO口,电路设计

需积分: 11 13 下载量 143 浏览量

2010-06-17

07:51:26

上传

评论

收藏 683KB DOC 举报

温馨提示

试读

9页

51单片机的IO口结构,了解51的IO口,对于单片机的外围电路设计是个很大的提高

资源推荐

资源详情

资源评论

一、P0 端口的结构及工作原理

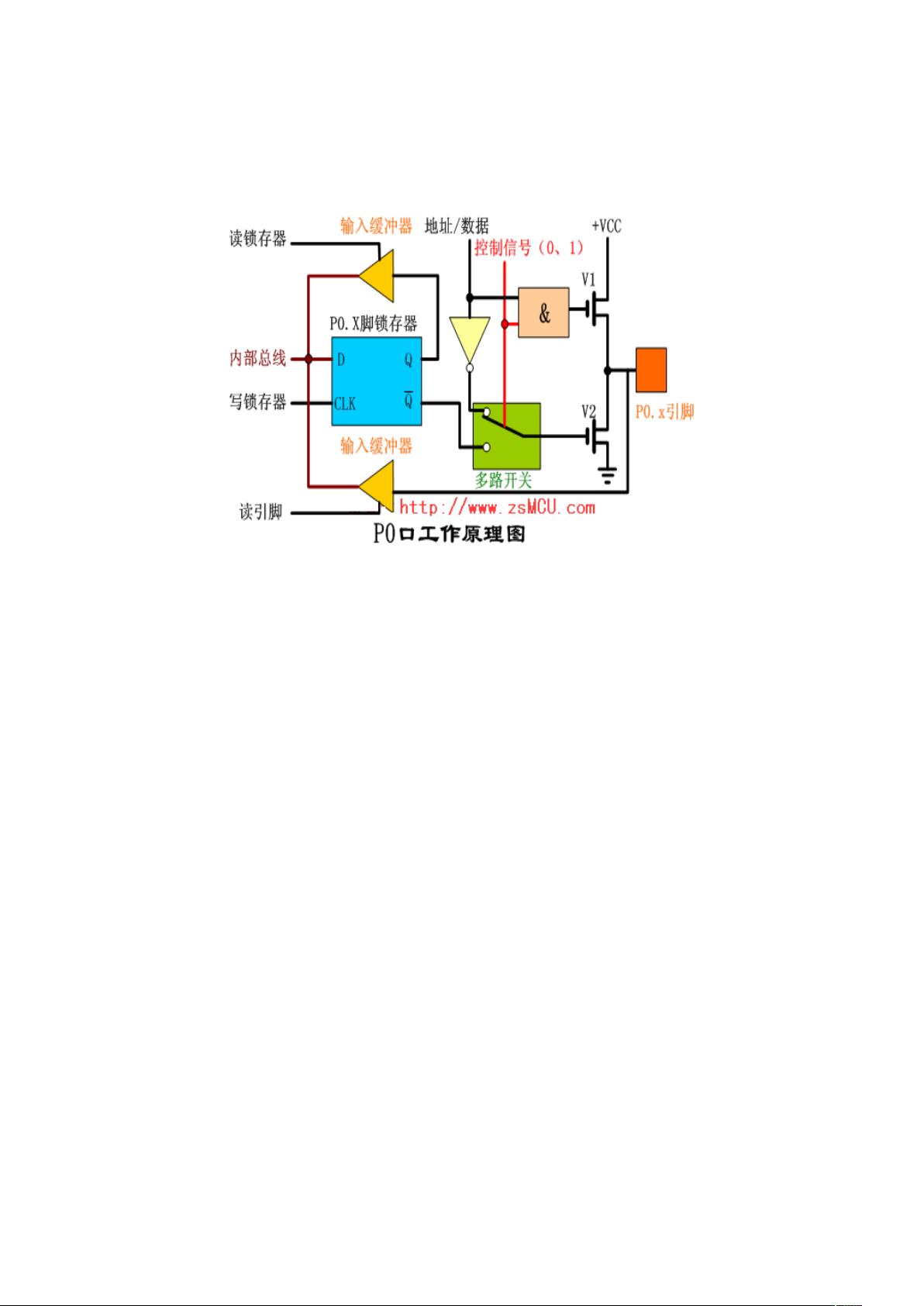

P0 端口 8 位中的一位结构图见下图:

由上图可见,P0 端口由锁存器、输入缓冲器、切换开关、一个与非门、一个与门及场效应管驱动电路

构成。再看图的右边,标号为 P0.X 引脚的图标,也就是说 P0.X 引脚可以是 P0.0 到 P0.7 的任何一位,即

在 P0 口有 8 个与上图相同的电路组成。

下面,我们先就组成 P0 口的每个单元部份跟大家介绍一下:

先看输入缓冲器:在 P0 口中,有两个三态的缓冲器,在学数字电路时,我们已知道,三态门有三个状

态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),大家看上

图,上面一个是读锁存器的缓冲器,也就是说,要读取 D 锁存器输出端 Q 的数据,那就得使读锁存器的这

个缓冲器的三态控制端(上图中标号为‘读锁存器’端)有效。下面一个是读引脚的缓冲器,要读取 P0.X 引

脚上的数据,也要使标号为‘读引脚’的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机

的内部数据总线上。

D 锁存器:构成一个锁存器,通常要用一个时序电路,时序的单元电路在学数字电路时我们已知道,一个

触发器可以保存一位的二进制数(即具有保持功能),在 51 单片机的 32 根 I/O 口线中都是用一个 D 触发

器来构成锁存器的。大家看上图中的 D 锁存器,D 端是数据输入端,CP 是控制端(也就是时序控制信号

输入端),Q 是输出端,Q 非是反向输出端。

对于 D 触发器来讲,当 D 输入端有一个输入信号,如果这时控制端 CP 没有信号(也就是时序脉冲没有到

来),这时输入端 D 的数据是无法传输到输出端 Q 及反向输出端 Q 非的。如果时序控制端 CP 的时序脉冲

一旦到了,这时 D 端输入的数据就会传输到 Q 及 Q 非端。数据传送过来后,当 CP 时序控制端的时序信号

消失了,这时,输出端还会保持着上次输入端 D 的数据(即把上次的数据锁存起来了)。如果下一个时序

控制脉冲信号来了,这时 D 端的数据才再次传送到 Q 端,从而改变 Q 端的状态。

多路开关:在 51 单片机中,当内部的存储器够用(也就是不需要外扩展存储器时,这里讲的存储器包括

数据存储器及程序存储器)时,P0 口可以作为通用的输入输出端口(即 I/O)使用,对于 8031(内部没有

ROM)的单片机或者编写的程序超过了单片机内部的存储器容量,需要外扩存储器时,P0 口就作为‘地址/

资源评论

okti123456

- 粉丝: 1

- 资源: 7

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功