5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

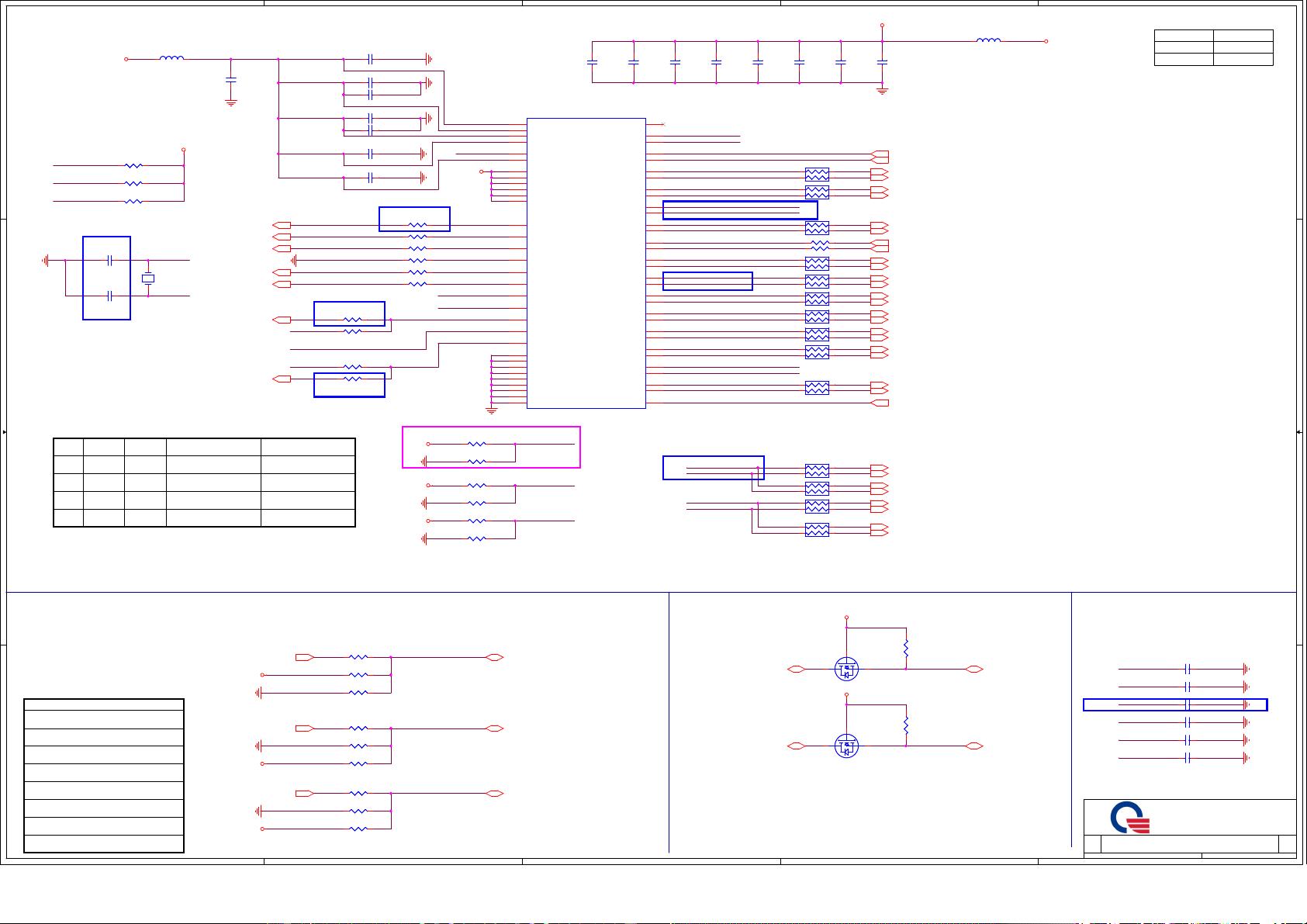

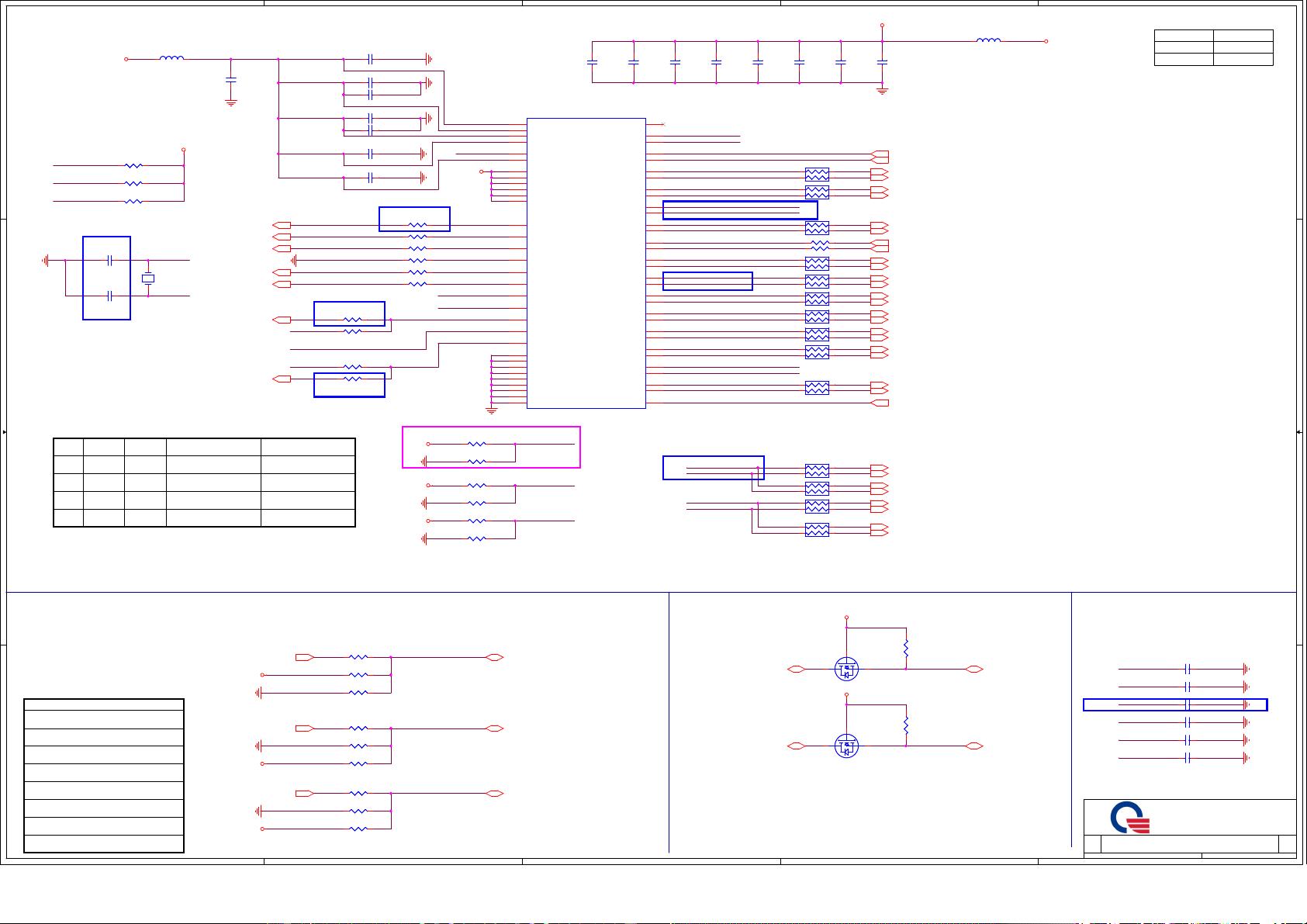

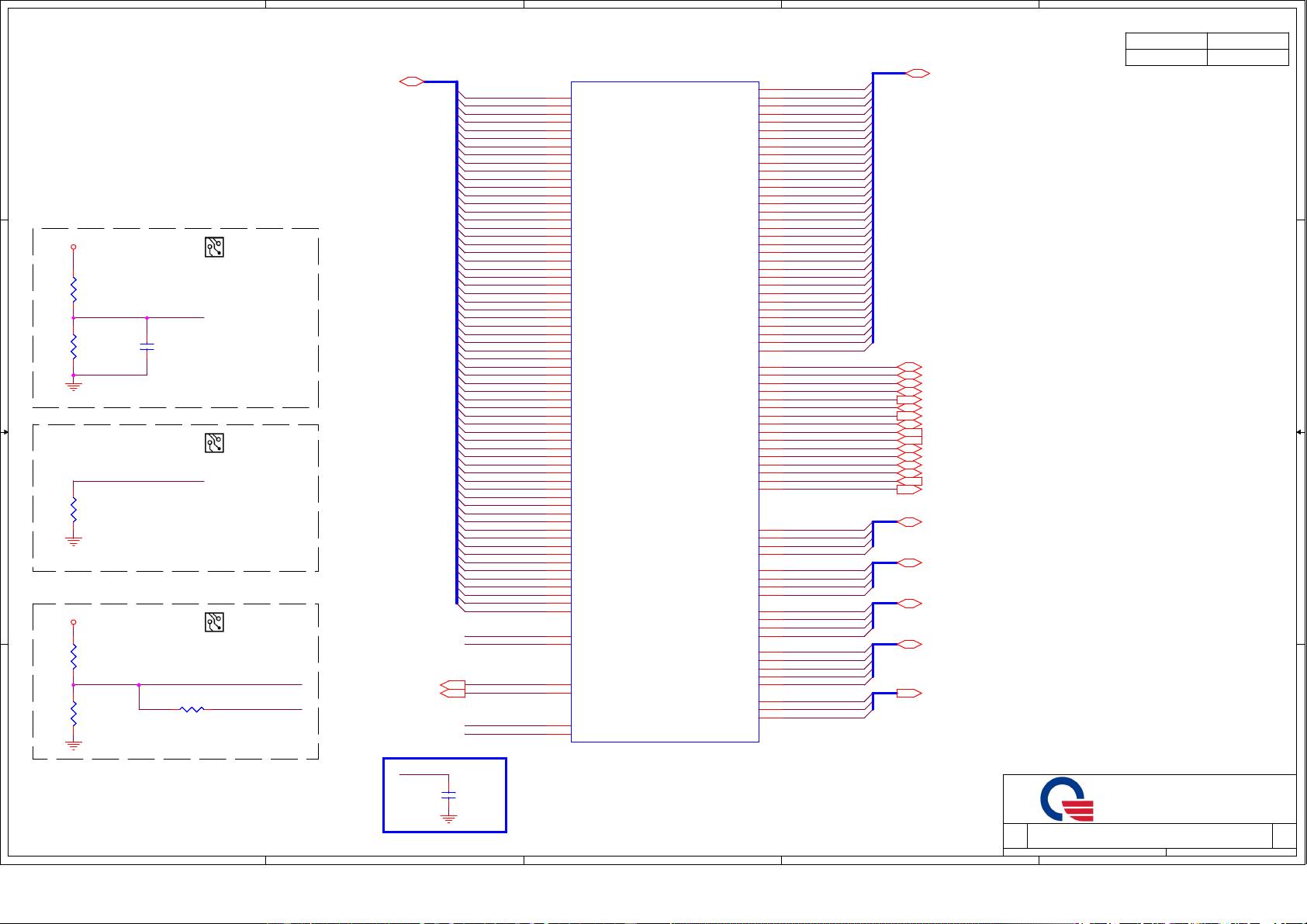

DREFSSCLK_R

DREFSSCLK#_R

CLK_CPU_BCLK#_R

CLK_PCIE_3GPLL#_R

CLK_PCIE_3GPLL_R

CLK_PCIE_SATA_R

CLK_PCIE_SATA#_R

CLK_MCH_BCLK_R

CLK_MCH_BCLK#_R

CLK_CPU_BCLK_R

CGCLK_SMB

CGDAT_SMB

PM_STPCPU#

PM_STPPCI#

DREFCLK#_R

DREFCLK_R

CG_XOUT

VDD_CK_VDD_PCI

VDD_CK_VDD_PCI

VDD_CK_VDD_CPU

FSA

CLK_BSEL0

CLK_BSEL1

CLK_BSEL0

PCLK_OZ129_R

PCLK_ICH_R

VDD_CK_VDD_REF

VDD_CK_VDD_48

PCLK_PCM_R

CLK_MCH_OE#_R

CG_XIN

VDD_CK_VDD_PCI

CLK_BSEL2

CGCLK_SMB

NEW_CLKREQ#_R

NEW_CLKREQ#_R

CLK_PCIE_NEW_R

CLK_PCIE_NEW_R#

CLK_PCIE_MINI3_R

CLK_PCIE_MINI3#_R

CLK_PCIE_MINI#_R

CLK_PCIE_MINI_R

CLK_PCIE_LAN_R

CLK_PCIE_LAN#_R

CLK_PCIE_ICH_R

CLK_PCIE_ICH#_R

DREFSSCLK_R

DREFSSCLK#_R

CLK_PCIE_MINI2&4_R

CLK_PCIE_MINI2&4#_R

CLK_PCIE_MINI2&4#_R

CLK_PCIE_MINI2&4_R

CGDAT_SMB

PCLK_ICH

PCLK_OZ129

CLK_BSEL2

FSC

CLK_BSEL1

FSB

CG_XOUT

CG_XIN PCI_CLK_SIO_R

PCLK_DEBUG_RPCLK_DEBUG

PCLK_591_RPCLK_591

PCLK_591

PCLK_OZ129

PCLK_ICH

PCLK_PCM

CLKUSB_48

PCLK_591

PCLK_ICH

PCLK_DEBUG

14M_ICH

PM_STPCPU#

PM_STPPCI#

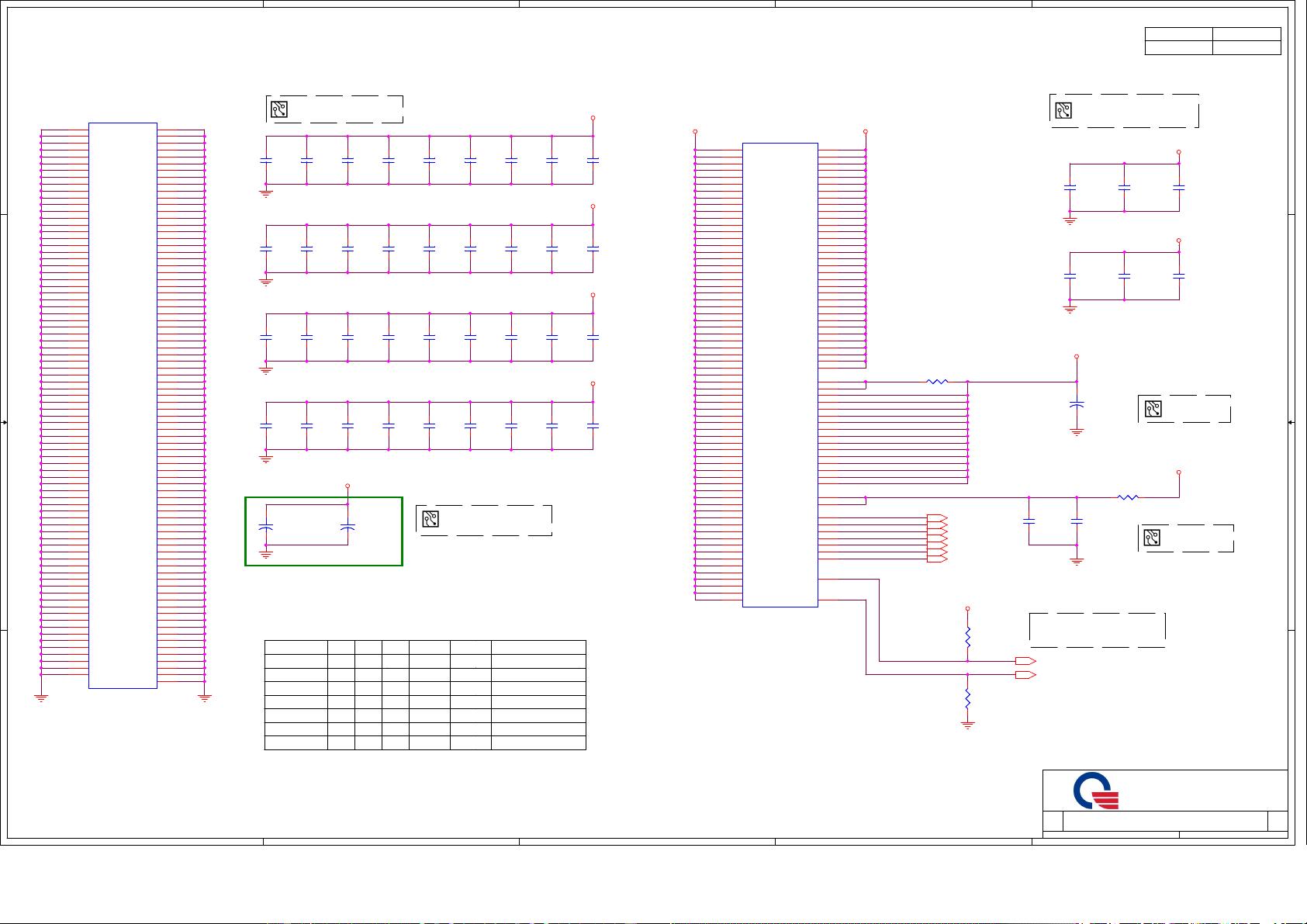

CLK_CPU_BCLK 3

CLK_CPU_BCLK# 3

CLK_MCH_BCLK 5

CLK_MCH_BCLK# 5

PCLK_PCM23

CLK_PCIE_SATA# 12

CLK_PCIE_SATA 12

PM_STPPCI# 14

PM_STPCPU# 14

DREFCLK 6

DREFCLK# 6

CLK_PCIE_3GPLL 6

CLK_PCIE_3GPLL# 6

CPU_BSEL03

CPU_BSEL13

CLKUSB_4814

CK_PWRGD 14

CLK_MCH_OE# 6

CPU_BSEL23

SCLK14,21,25,27

SDATA14,21,25,27

NEW_CLKREQ# 27

CLK_PCIE_NEW 27

CLK_PCIE_NEW# 27

CLK_PCIE_MINI3 25

CLK_PCIE_MINI3# 25

CLK_PCIE_MINI 25

CLK_PCIE_MINI# 25

CLK_PCIE_LAN 26

CLK_PCIE_LAN# 26

CLK_PCIE_ICH 13

CLK_PCIE_ICH# 13

CLK_MXM 18

CLK_MXM# 18

DREFSSCLK 6

DREFSSCLK# 6

CLK_PCIE_MINI2 25

CLK_PCIE_MINI2# 25

CLK_PCIE_MINI4 25

CLK_PCIE_MINI4# 25

CGDAT_SMB 17

CGCLK_SMB 17

MCH_BSEL0 6

MCH_BSEL1 6

MCH_BSEL2 6

PCLK_ICH13

PCLK_OZ12924

14M_ICH14

PCLK_DEBUG25

PCLK_59128

+3V

+1.05V_VDD

+1.05V

+1.05V

+1.05V

+3V

+3V

+1.05V_VDD

+1.05V

+3V

+3V

+3V

+3V

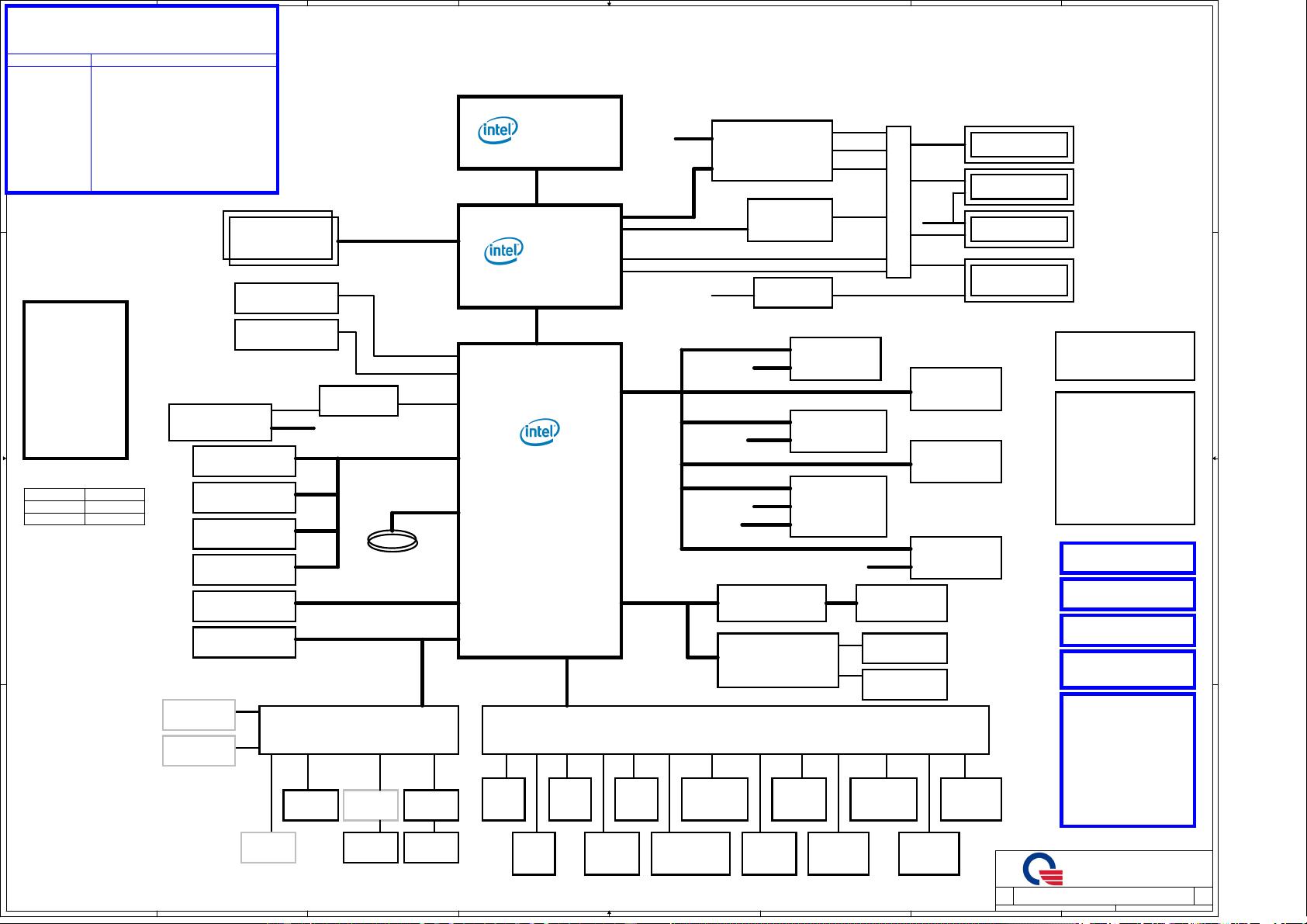

Size Document Number Rev

Date: Sheet of

Quanta Computer Inc.

PROJECT :

Clock Gen

E3D

2 40Monday, May 26, 2008

TE1M

Size Document Number Rev

Date: Sheet of

Quanta Computer Inc.

PROJECT :

Clock Gen

E3D

2 40Monday, May 26, 2008

TE1M

Size Document Number Rev

Date: Sheet of

Quanta Computer Inc.

PROJECT :

Clock Gen

E3D

2 40Monday, May 26, 2008

TE1M

To SB

To NB

To SB

To SB

To LAN

To MINI1

To MINI3

To New Card

To NB

To MINI2

To NB

To VGA Card

To NB

To CPU

To MINI4

BSEL Frequency Select Table

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

133Mhz

166Mhz

200Mhz

400Mhz

Reserved

100Mhz

333Mhz

FSC FSB FSA Frequency

266Mhz0

011

CL=20p

Pin 4

Pin 6

Pin 7

ICS9LPRS365

(ALPRS365K13)

RTM875T-606

(AL000875K06)

(default)

(default)

(default)

PCI2/TME

PCI-3

PCI2/TME

internal PD

PCI-4/27M_SEL

PCIF-5/ITP_EN

PULL HIGH PULL DOWN

NO OVERCLOCKING NORMAL RUN

PIN37/38 IS SRC5

PIN37/38 IS

PCI_STOP/CPU_STOP

PIN 17/18 IS 27MHz

PIN 17/18

IS SRC/DOT

PIN 46/47 IS CPUITP PIN 46/47 IS SRC8

PCI-3/SRC5_EN

internal PD

PCI-4/27M_SEL

internal PD

PCIF-5/ITP_EN

internal PD

(default)

Pin 5

HIGH 27MHz

LOW SRC

<MAIN>:ICS9LPRS365BGLFT QCI:ALPRS365K13

<SECOND>:SLG8SP512TTR: QCI:AL8SP512K05

Clock Generator

Clock Gen I2CFREQ. SEL TABLE

EXT VGAEV@

INT VGA

Reference

Description

BOM Option Table

IV@

B2A

B2A

B2A

B2A

B2A

B2A

B2A

B2A

C3B

C685

0.1u/10V_4

C685

0.1u/10V_4

R245

10K_4

R245

10K_4

2

4

1

3

RP514 EV@0X2RP514 EV@0X2

VDD_SRC_IO_2

36

VDD_48

9

VSS_SRC3

42

PCI0/CR#_A

1

PCI2/TME

4

IO_VOUT

48

XTAL_OUT

59

SCLK

64

SDA

63

REF0/FSC/TESTSEL

62

VDD_SRC_IO_3

45

VDD_CPU_IO

49

VSS_REF

58

SRC8#/ITP#

46

PCIF5/ITP_EN

7

PCI3

5

VSS_PLL3

19

VDD_96_IO

12

VSS_48

11

VSS_IO

15

SRC1/SE1

17

VSS_SRC1

23

VSS_PCI

8

SRC5#/CPU_STOP#

37

SRC10

34

SRC8/ITP

47

VDD_CPU

55

PCI1/CR#_B

3

FSB/TEST/MODE

57

PCI4/SRC5_EN

6

SRC2#/SATA#

22

SRC5/PCI_STOP#

38

VDD_SRC

39

VSS_CPU

52

SRC10#

35

XTAL_IN

60

USB_48/FSA

10

VDD_PLL3_IO

20

SRC2/SATA

21

SRC3/CR#_C

24

SRC4

27

SRC6

41

SRC7/CR#_F

44

SRC9

30

SRC11/CR#_H

33

SRC3#/CR#_D

25

SRC4#

28

SRC6#

40

SRC7#/CR#_E

43

SRC9#

31

SRC11#/CR#_G

32

CPU1#

50

CPU1

51

CPU0#

53

CPU0

54

VDD_PCI

2

VDD_SRC_IO_1

26

VDD_PLL3

16

VDD_REF

61

VSS_SRC2

29

SRC1#/SE2

18

SRC0/DOT96

13

SRC0#/DOT96#

14

CKPWRGD/PWRDWN#

56

CK505

U12

ICS9LPRS365BGLFT

CK505

U12

ICS9LPRS365BGLFT

R216 475/F_4R216 475/F_4

C706 10u/10V_8C706 10u/10V_8

R600 *56_4R600 *56_4

R225 1K_4R225 1K_4

21

Y3

14.318MHZ

Y3

14.318MHZ

2

4

1

3

RP48 0X2RP48 0X2

2

4

1

3

RP46 0X2RP46 0X2

2

4

1

3

RP44 0X2RP44 0X2

C643 0.1u/10V_4C643 0.1u/10V_4

R601 0_4R601 0_4

C211

0.1u/10V_4

C211

0.1u/10V_4

C695 0.1u/10V_4C695 0.1u/10V_4

R235 33_4R235 33_4

C694 0.1u/10V_4C694 0.1u/10V_4

C204

*10u/10V_8

C204

*10u/10V_8

L17PBY160808T-301Y-N_6 L17PBY160808T-301Y-N_6

2

4

1

3

RP53 IV@0X2RP53 IV@0X2

R241 10K_4R241 10K_4

R229 10K_4R229 10K_4

2

4

1

3

RP50 0X2RP50 0X2

R217 475/F_4R217 475/F_4

R244 10K_4R244 10K_4

C207

0.1u/10V_4

C207

0.1u/10V_4

R219 2.2K_4R219 2.2K_4

R593 1K_4R593 1K_4

C214 15p/50V_4C214 15p/50V_4

C215 *33p/50V_4C215 *33p/50V_4

R246 *10K_4R246 *10K_4

R218 2.2K_4R218 2.2K_4

R243 10K_4R243 10K_4

C225 *33p/50V_4C225 *33p/50V_4

R227 2.2K_4R227 2.2K_4

2

4

1

3

RP52 0X2RP52 0X2

C699 0.1u/10V_4C699 0.1u/10V_4

R232 *0_4R232 *0_4

C206

0.1u/10V_4

C206

0.1u/10V_4

R242 *10K_4R242 *10K_4

2

4

1

3

RP51 EV@0X2RP51 EV@0X2

3

2

1

Q509

RHU002N06

Q509

RHU002N06

R252 47_4R252 47_4

C216 *33p/50V_4C216 *33p/50V_4

R237 47_4R237 47_4

L518 PBY160808T-301Y-N_6L518 PBY160808T-301Y-N_6 C700 0.1u/10V_4C700 0.1u/10V_4 C208

0.1u/10V_4

C208

0.1u/10V_4

R248

10K_4

R248

10K_4

C205

10u/10V_8

C205

10u/10V_8

2

4

1

3

RP512 IV@0X2RP512 IV@0X2

R250 10K_4R250 10K_4

C219 *33p/50V_4C219 *33p/50V_4

R230 *10K_4R230 *10K_4

R215 10K_4R215 10K_4

C239 27p/50V_4C239 27p/50V_4

2

4

1

3

RP42 0X2RP42 0X2

R247 33_4R247 33_4

R602 1K_4R602 1K_4

R226 *0_4R226 *0_4

R238 33_4R238 33_4

C704

10u/10V_8

C704

10u/10V_8

R598 0_4R598 0_4

C226 27p/50V_4C226 27p/50V_4

2

4

1

3

RP43 0X2RP43 0X2

C677

0.1u/10V_4

C677

0.1u/10V_4

R249 33_4R249 33_4

C224 *33p/50V_4C224 *33p/50V_4

2

4

1

3

RP47 0X2RP47 0X2

R228 0_4R228 0_4

C676 0.1u/10V_4C676 0.1u/10V_4

R234 47_4R234 47_4

3

2

1

Q507

RHU002N06

Q507

RHU002N06

2

4

1

3

RP49 IV@0X2RP49 IV@0X2

2

4

1

3

RP45 0X2RP45 0X2

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功