www.tektronix.com/bertscope 3

Clock Recovery Primer, Part 1

Abstract

Clock recovery is a common part of many measure-ments,

whether as part of the test setup or part of the device under

test. We’re going to look at clock recovery from a practical

point of view, with emphasis on how it affects measurements.

This document closely mirrors the poster “The Anatomy of

Clock Recovery, Part 1.”

Why is Clock Recovery Used?

Most gigabit communication systems are synchronous; that is,

the data within them is timed against a common clock. High

speed systems (such as serial buses and optical) usually send

NRZ (Non-Return to Zero) data, coded to have the clock it is

timed against embedded within it. Whether traveling across

inches of circuit board, or across continents on optical fiber,

the relationship between data and the clock it is timed against

can become disturbed. Extracting clock directly from the data

ensures that data regeneration at the receiver can be achieved

correctly.

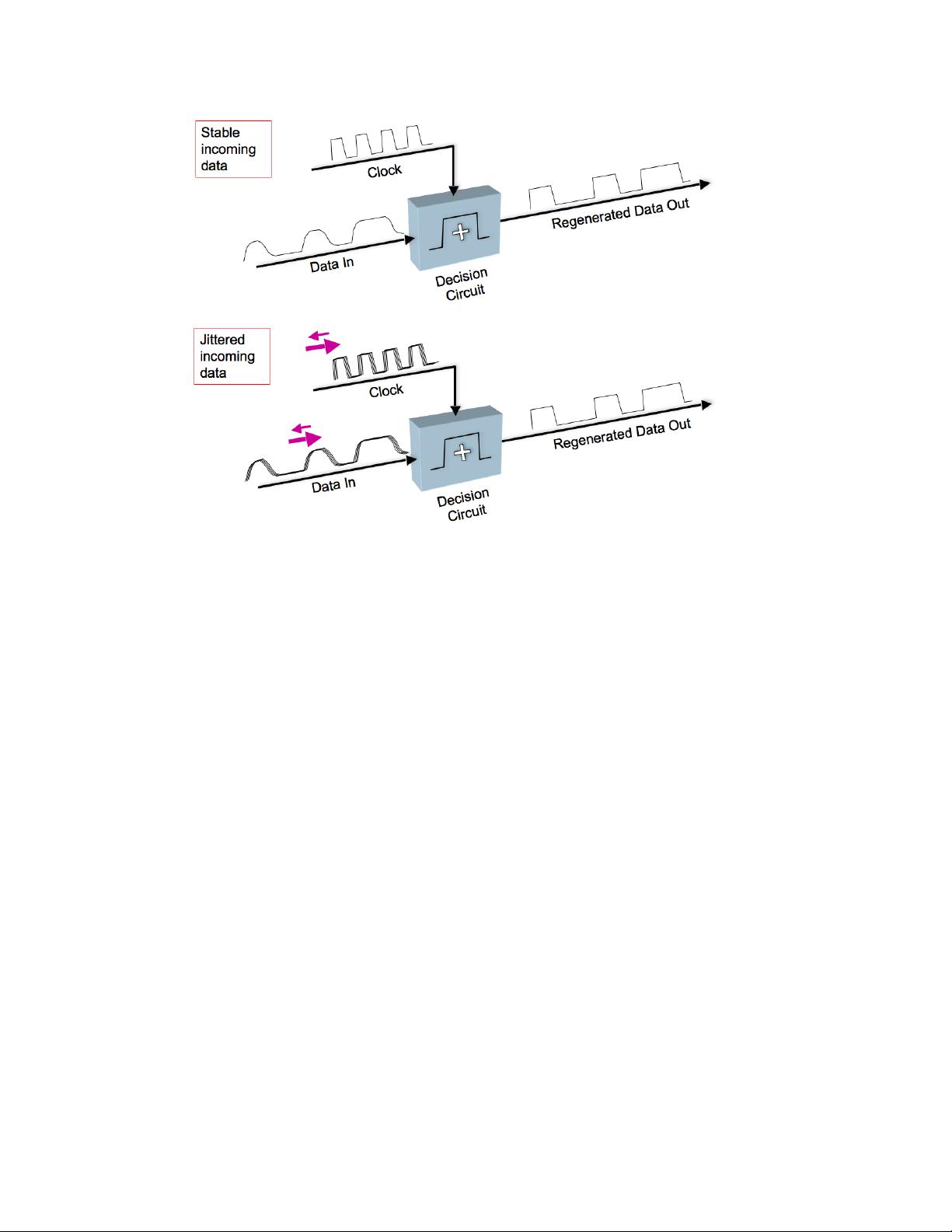

Receivers typically improve the incoming data before passing

it on. They do this by passing it through a decision circuit that

retimes the data and squares up the pulses. This process is

dependent upon a clock signal synchronous with the incoming

data, hence the use of clock recovery inside the receiver.

Timing variations such as jitter on the incoming data can be

reduced or removed if the clock used for retiming moves in the

same way at the same time.

As we will see, in practice the operation is more complex than

this, and the frequency of the incoming jitter is important.

How Does Clock Recovery Work?

There are many different architectures for clock recovery,

and a large amount of literature describing the advantages

and disadvantages of each. In measurement equipment, the

most common type is based on a phase locked loop (PLL).

We will look at this in more detail in a moment. Before we do,

it is worth noting that other architectures have been used in

measurement equipment in the past.

Older sampling scope clock recovery modules were often

feed-forward designs with fixed frequency filters switched in

for each rate. Suitable band pass filters are difficult to make

with narrow bands. They have also not been frequency agile,

and will not track data with moving center frequencies, such

as is found in spread spectrum clocking (SSC; see poster

“Anatomy of Clock Recovery, Part 2”).

Figure 1. If clock and data were to move in time by the same amount at the same time, a decision circuit could remove the effect of jitter.

评论0

最新资源