DS260 March 1, 2011 www.xilinx.com 1

Product Specification

© Copyright 2003 - 2011 Xilinx, Inc. XILINX, the Xilinx logo, Kintex, Virtex, Spartan, ISE and other designated brands included herein are trademarks of Xilinx in the

United States and other countries. MATLAB is a registered trademark of The MathWorks, Inc. All other trademarks are the property of their respective owners.

Introduction

The Xilinx LogiCORE™ IP Fast Fourier Transform

(FFT) implements the Cooley-Tukey FFT algorithm, a

computationally efficient method for calculating the

Discrete Fourier Transform (DFT).

Features

• Drop-in module for Kintex™-7, Virtex

®

-7, Virtex®-6,

Virtex-5, Virtex-4, Spartan®-6, Spartan-3/XA,

Spartan-3E/XA and Spartan-3A/XA/AN/3A DSP

FPGAs

• Forward and inverse complex FFT, run-time

configurable

• Transform sizes N = 2

m

, m = 3 – 16

• Data sample precision b

x

= 8 – 34

• Phase factor precision b

w

= 8 – 34

• Arithmetic types:

¨ Unscaled (full-precision) fixed-point

¨ Scaled fixed-point

¨ Block floating-point

• Fixed-point or floating-point interface

• Rounding or truncation after the butterfly

• Block RAM or Distributed RAM for data and

phase-factor storage

• Optional run-time configurable transform point

size

• Run-time configurable scaling schedule for scaled

fixed-point cores

• Bit/digit reversed or natural output order

• Optional cyclic prefix insertion for digital

communications systems

• Four architectures offer a trade-off between core

size and transform time

• Bit-accurate C model and MEX function for system

modeling available for download

• For use with Xilinx CORE Generator™ software

and Xilinx System Generator for DSP v13.1

LogiCORE IP

Fast Fourier Transform v7.1

DS260 March 1, 2011 Product Specification

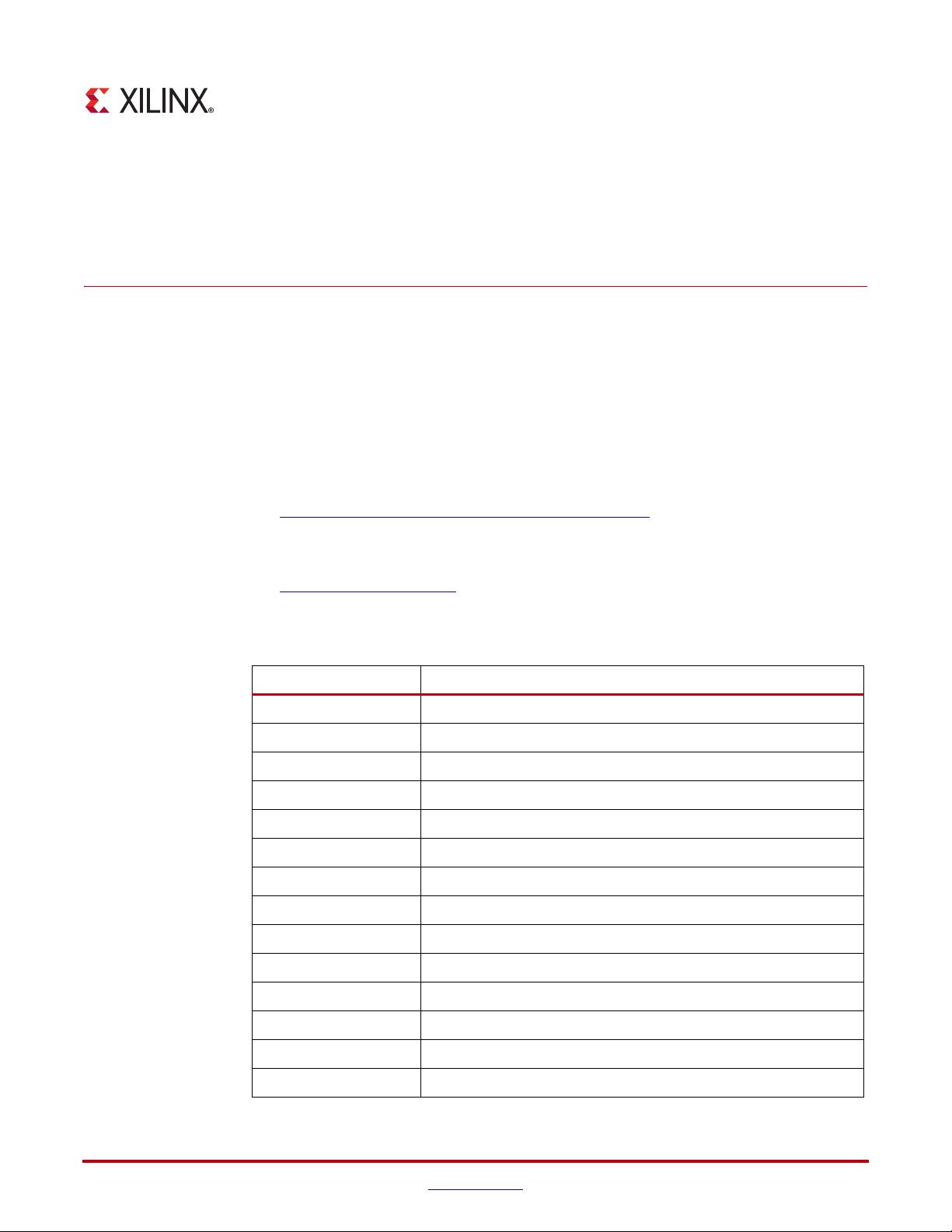

LogiCORE IP Facts Table

Core Specifics

Supported

Device Family

(1)

1. For a complete listing of supported devices, see the release notes

for this core.

Virtex-7 and Kintex-7,

Virtex-6, Virtex-5, Virtex-4,

Spartan-6, Spartan-3/XA, Spartan-3E/XA,

Spartan-3A/3AN/3A DSP/XA

Supported User

Interfaces

Not Applicable

Resources

(2)

2. Resources listed here are for Virtex-6 devices. For more complete

device performance numbers, see Table 7-Table 10.

Frequency

Configuration LUTs FFs

DSP

Slices

Block

RAMs

(3)

3. Based on 18K block RAMs.

Max.

Freq.

(4)

4. Performance numbers listed are for Virtex-6 FPGAs. For more

complete performance data, see Table 7-Table 10.

Radix-2,

2048-point,

variable point

size, 16-bit

data/phase

factors, scaled,

convergent

rounding

1092 1265 3 5 395 MHz

Provided with Core

Documentation

Product Specification

Design Files Netlist

Example Design Not Provided

Test Bench Not Provided

Constraints File Not Applicable

Simulation

Model

VHDL behavioral model in the xilinxcorelib library

VHDL UniSim structural model

Verilog UniSim structural model

Tested Design Tools

Design Entry

Tools

CORE Generator tool 13.1

System Generator for DSP 13.1

Simulation

Mentor Graphics ModelSim 6.6d

Cadence Incisive Enterprise Simulator (IES) 10.2

Synopsys VCS and VCS MX 2010.06

ISIM 13.1

Synthesis Tools N/A

Support

Provided by Xilinx, Inc.