没有合适的资源?快使用搜索试试~ 我知道了~

按照大纲的知识点整理----计算机组成原理

需积分: 10 12 下载量 162 浏览量

2011-04-09

13:54:12

上传

评论

收藏 412KB DOC 举报

温馨提示

试读

26页

按照大纲的知识点整理----计算机组成原理.doc按照大纲的知识点整理----计算机组成原理.doc

资源推荐

资源详情

资源评论

一、计算机系统概述

(一)计算机发展历程

(二)计算机系统层次结构

1.计算机硬件的基本组成

2.计算机软件的分类

3.计算机的工作过程

(三)计算机性能指标

1. 吞吐量对网络、设备、端口、虚电路或其他设施,单位时间内成功地传

送数据的数量(以比特、字节、分组等测量)。

2. 响应时间

3. CPU 时钟周期(Clock Cycle):又称节拍没冲或 T 周期,是处理操作

的最基本单位,是计算机中最基本的、最小的时间单位。主频的倒数

4. 主频: 即 CPU 内核工作的时钟频率(CPU Clock Speed)。 CPU 的主频

表示在 CPU 内数字脉冲信号震荡的速度,与 CPU 实际的运算能力并没

有直接关系。

5. CPI (Clock cycle Per Instruction)表示每条计算机指令执行所需的时钟

周期。

6. CPU 执行时间

7. MIPS(Million Instruction per second)每秒执行百万条指令

某机器每秒执行 300 万条指令,则记作 3 MIPS

8. MFLOPS (Million Floationg-point Operations per Second,每秒百万个浮点

操 作 ) 衡 量 计 算 机 系 统 的 主 要 技 术 指 标 之 一 。 对 于 一 给 定 的 程 序 ,

MFLOPS 的定义为:MFLOPS=操作浮点数/(执行时间*10E6)( 10E6

位 10 的 6 次方)。

1. 指令周期:执行一条指令所需要的时间,一般由若干个机器周期组成,

是从取指令、分析指令到执行完所需的全部时间。

2. 机器周期:(又称 cpu 周期)在计算机中,为了便于管理,常把一条指

令的执行过程划分为若干个阶段,每一阶段完成一项工作。例如,取指

令、存储器读、存储器写等,这每一项工作称为一个基本操作。完成一

个基本操作所需要的时间称为机器周期。通常用内存中读取一个指令字

的最短时间来规定因而又称总线周期

3. 在电子技术中,脉冲信号是一个按一定电压幅度,一定时间间隔连续发

出的脉冲信号。脉冲信号之间的时间间隔称为周期;而将在单位时间

(如 1 秒)内所产生的脉冲个数称为频率。频率是描述周期性循环信号

(包括脉冲信号)在单位时间内所出现的脉冲数量多少的计量名称;频

率的标准计量单位是 Hz(赫)。

二、数据的表示和运算

(一)数制与编码

1.进位计数制及其相互转换

2.真值和机器数

真值: 带”+””-”符号的数

机器数: 符号数字化的数

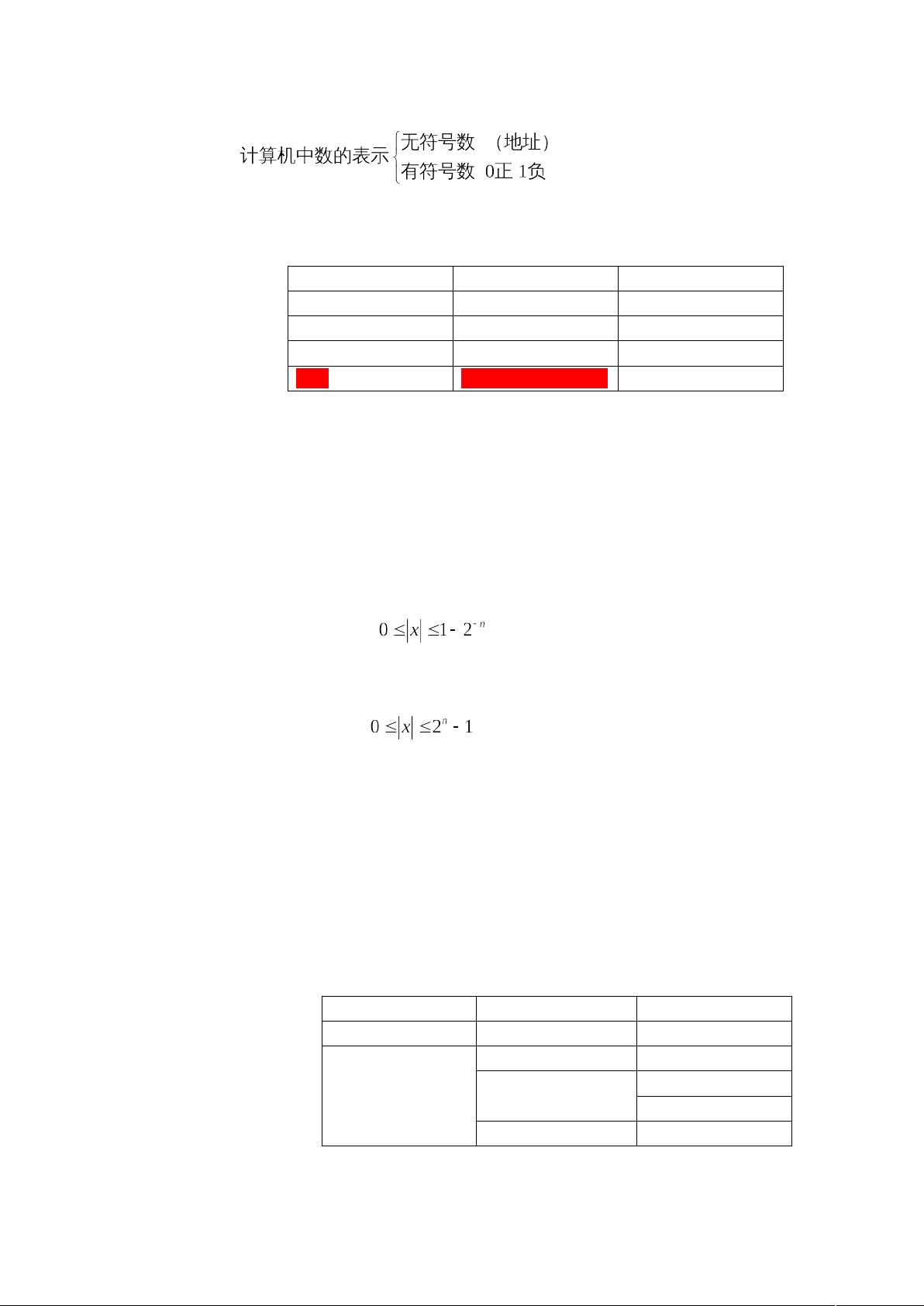

编码方式 正数表示 负数表示

原码 同原 同

补码 同原 逐位求反加一

反码 同 逐位求反

移码 根补码差一个符号位

补码比原码反码多表示一个负数

3.BCD 码

4.字符与字符串

5.校验码

(二)定点数的表示和运算

1.表示

(1) 定点数的表示

1) 定点小数

表示范围:

定点小数运算的过程中存在着上溢和下溢.

2) 定点整数

表示范围

定点整数运算的过程中存在着上溢而不存在下溢.

(2) 无符号数的表示

(3) 有符号数的表示

2.运算

(1) 定点数的位移运算

1) 无符号数的移位—逻辑移位

左移:高位移出,低位填零

右移:低位移出高位填零

2) 有符号数的移位—算术移位

码制 填补代码

正数 原码、补码、反码

0

负数

原码

0

补码

左移添 0

右移填 1

反码 都填 1

(2) 加减乘除运算

1) 原码定点数的加/减运算

2) 补码定点数的加/减运算

3) 定点数的乘/除运算

a) 原码定点数的乘法运算

b) 补码定点数的乘法运算

每次根据乘数最后两位的差值来判断如何运算

c) 原码定点数的除法运算

商符另计算

1) 恢复余数法

第一次进行减除数操作

如果余数小于 0,则商上 0,加除数(恢复余数)进行左移一位.

如果余数大于 0,则商上 1,并尾数直接进行左移.下次减

除数.

最后根据计算中的左移位数,判断出余数的右移位数.

2) 不恢复余数法(加减交替法)

d) 补码定点数的除法运算

加减交替法(符号位和数值部分一起参加运算)

4) 溢出概念和判别方法

(三)浮点数的表示和运算

1.浮点数的表示;浮点数的表示范围;IEEE754 标准

float 大小为 4 字节,即 32 位,内存中的存储方式如下:

符号位(1 bit)

指数(8 bit)

尾数(23 bit)

float 有效数字是 6--7 位

取值范围 -3.4*10(-38)~3.4*10(38)

double 大小为 8 字节,即 64 位,内存布局如下:

符号位(1 bit)

指数(11 bit)

尾数(52 bit)

double 有效数字是 15--16 位

取值范围 -1.7*10(-308)~1.7*10(308)

2.浮点数的加/减运算

有关概念:

/*s>0 时补码规格化形式为[s]

补

=00.1ХХ…Х。*/

/*s<0 时补码规格化形式为[s]

补

=11.0ХХ…Х。*/

/*s>0 为补码且 s=-0.5 时规定-0.5 不是规格化数*/

补码的规格化数 是首位非符号位与符号位 相异 则为规格化数。

因为补码负数,0 为有效位,1 为无效位,而原码负数,1 为有效位,0 为无

效位,故补码负数跟原码负数规格化形式不同。

注:有效位即为代表数值的位。

左右规

/*左规:当尾数出现 00.0ХХ…Х 或 11.1ХХ…Х 时,需要左规,左规一位,

阶码减一*/

/*右规:当尾数出现 01.ХХ…Х 或 10.ХХ…Х 时,表示尾数溢出,可通过右规

处理,右移一位,阶码加一*/

定点运算中溢出不允许

但浮点运算中溢出允许。可通过右规处理,只是影响精度

左右规移位与算数移位不一样

浮点数阶码真值加 127 不加 128 的原因

因为当阶码 e 为全 0 且尾数 M 也为全 0 时,表示的真值 x 为零,结合符号位

S 为 0 或 1,有正零和负零之分。当阶码 e 为全 1 且尾数 M 为全 0 时,表示的真值

x 为无穷大,结合符号位 S 为 0 或 1,也有正无穷和负无穷之分。这样的 32 位浮

点数表示中,要除去 e 用全 0 和全 1(255)表示零和无穷大的特殊情况,指数的

偏移值不选 128(10000000),而选 127(01111111)。对于规格化浮点数, e

的范围变为 1 到 254,真正的指数值 E 则为-126 到+127。

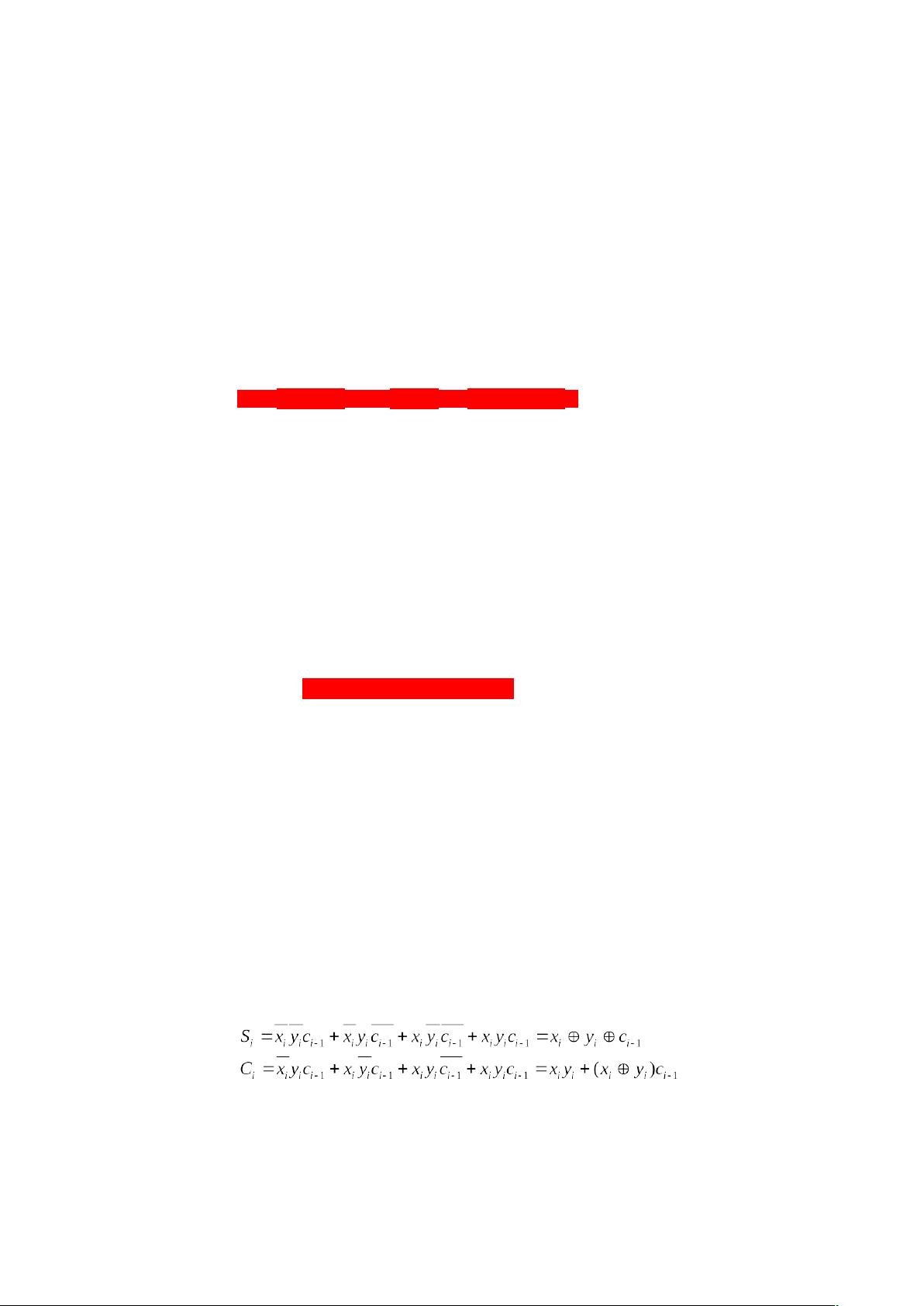

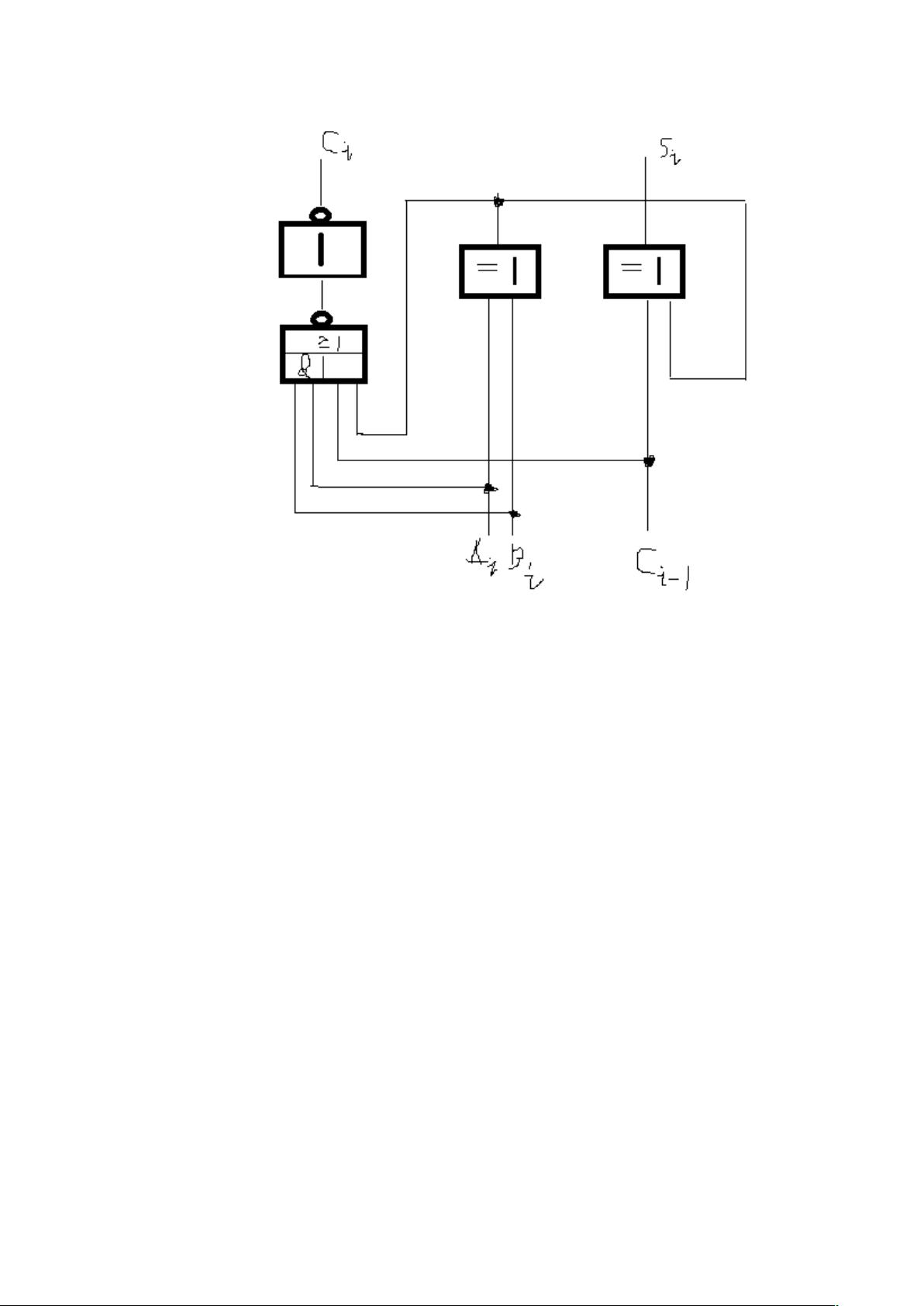

(四)算术逻辑单元 ALU

硬件结构:

一位全加器:

x

i

y

i

为相加数第 i 位。C

i-1

表示低位进位信号

S

i

第 i 位的和。C

i

为 i 位产生的进位。

1.串行加法器和并行加法器

(1) 串行加法器

只用一位全加器来实现两个数的相加运算。从低位到高位逐位运算

优点:成本低

缺点:速度慢

(2) 并行加法器

1) 串行进位、并行加法

原理:

2) 并行进位、并行加法(组内并行、组间串行)

3) 双重分组快速进位链:(组内与组间并行,大组间串行)

2.算术逻辑单元 ALU 的功能和机构

三、存储器层次机构

(一)存储器的分类

(1) 按存储介质分

1) 半导体存储器 (双极型: 耗电量大,低集成

Mos…)

优点: 体积小、功能低、存取时间短

缺点: 电源消失时所存储信息也丢失

剩余25页未读,继续阅读

资源评论

nara198803028

- 粉丝: 0

- 资源: 8

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功