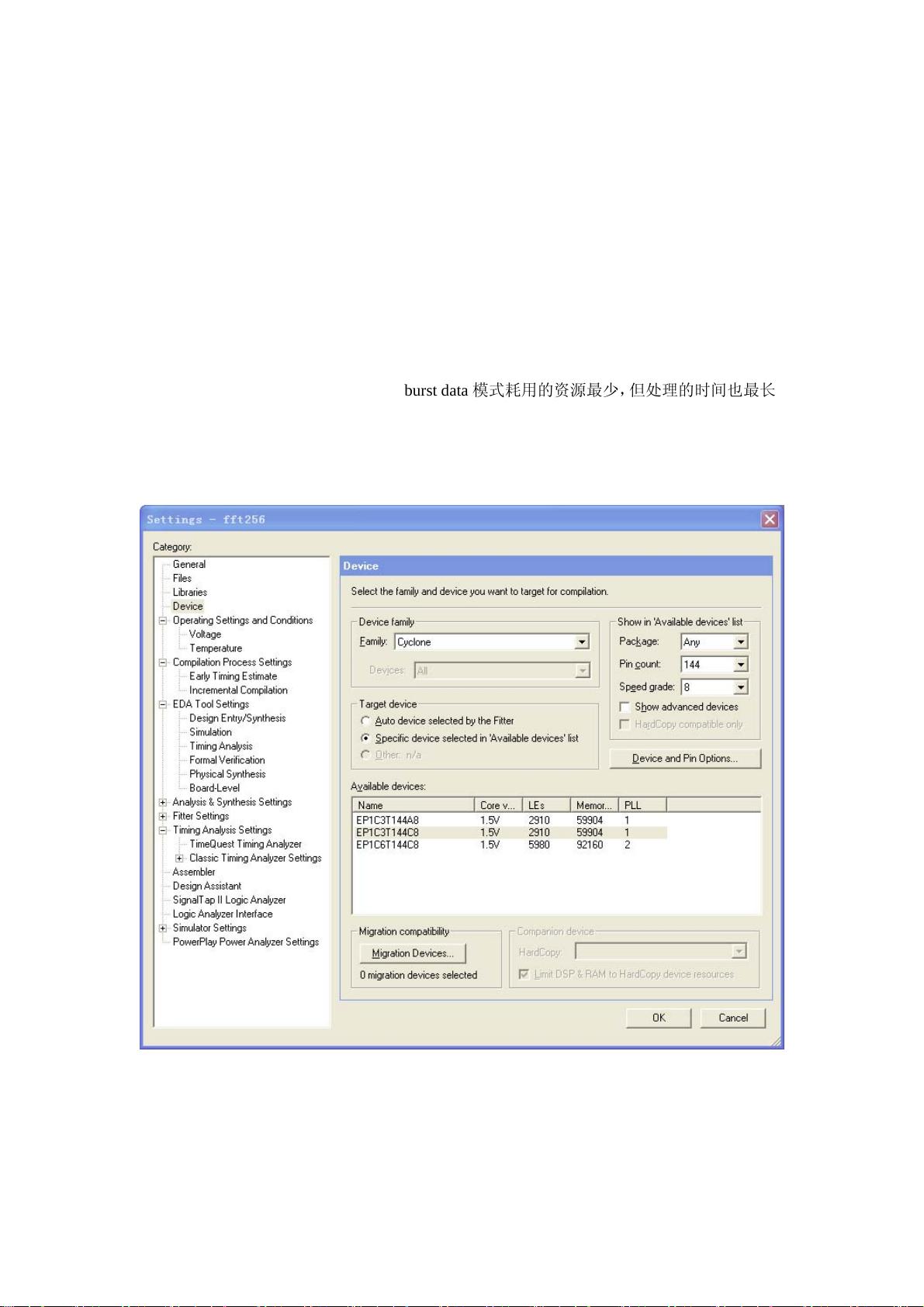

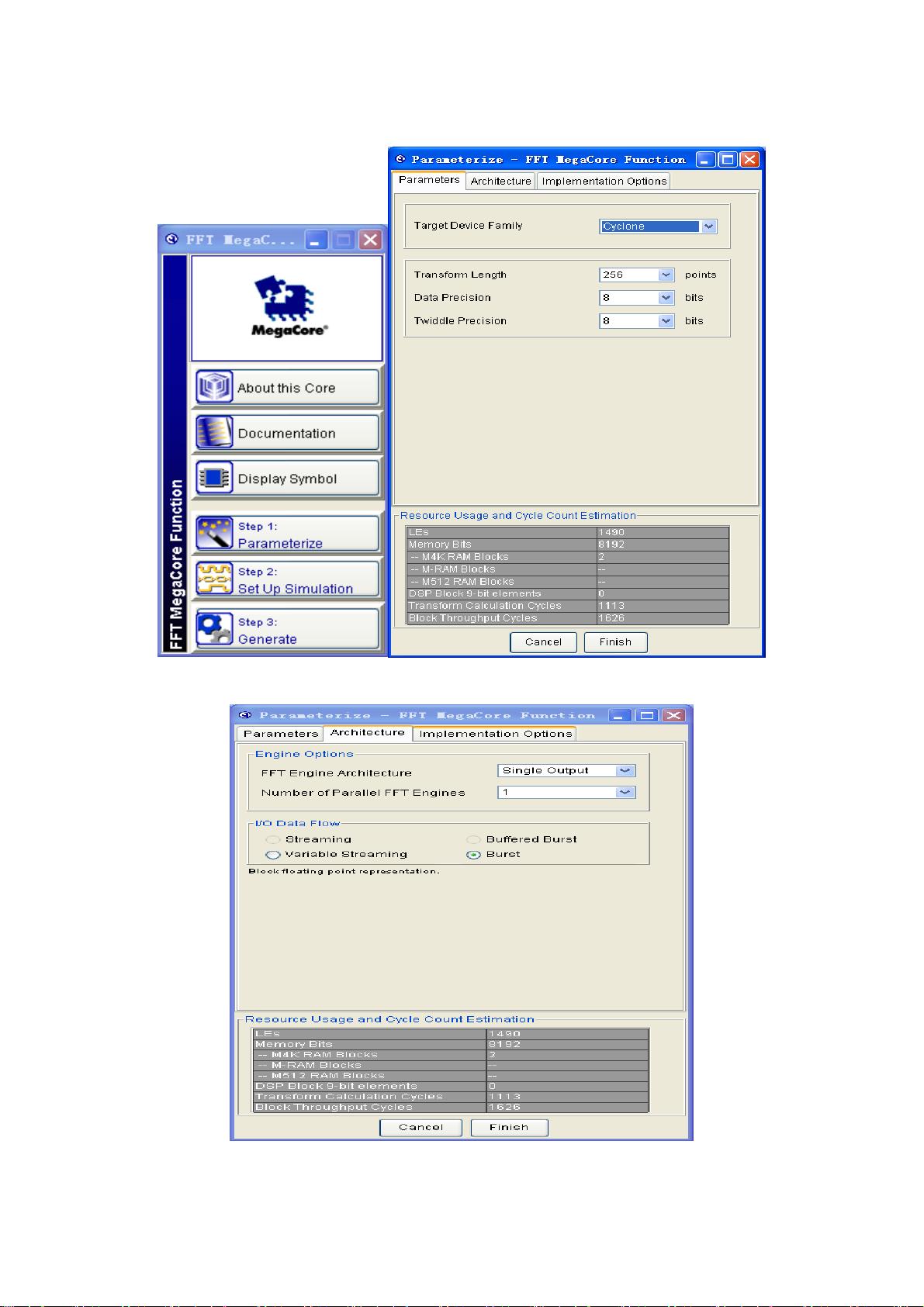

### Quartus中FFT IP Core的使用详解 #### 一、引言 在数字信号处理领域,快速傅里叶变换(FFT)是一种非常重要的算法,广泛应用于频谱分析、信号处理等多个方面。Altera公司(现已被Intel收购)的Quartus II软件提供了强大的IP核支持,其中包括FFT IP Core。本文将详细介绍如何在Quartus II中使用FFT IP Core,并通过具体的实例讲解如何设置参数以及编写控制逻辑。 #### 二、FFT IP Core简介 FFT IP Core是Quartus II提供的内置模块之一,用于实现快速傅里叶变换。该IP Core支持多种工作模式,可以根据具体需求选择不同的配置,从而满足不同的性能和资源消耗要求。其中,“burst data”模式是一个较为常见的工作模式,它能够有效地平衡资源占用与处理时间。 #### 三、FFT IP Core的控制信号 为了正确地使用FFT IP Core,需要理解并正确设置其控制信号。主要包括以下几个信号: 1. **sink_sop**:表示每帧输入数据的起始数据。当此信号为高电平时,表示接下来的数据是当前帧数据的起始位置。 2. **sink_eop**:表示每帧输入数据的结束数据。当此信号为高电平时,表示接下来的数据是当前帧数据的结束位置。 3. **sink_valid**:表示输入数据的有效性。当此信号为高电平时,表示当前输入的数据是有效的。 #### 四、使用实例:256点FFT运算 本节将详细介绍如何使用FFT IP Core来完成256点的FFT运算。这里假设使用的开发环境为Quartus II 8.0 SP1版,仿真工具为ModelSim SE Plus 6.4。 ##### 1. 新建工程 - 工程名称为`fft256`。 - 器件选择Cyclone系列的EP1C3T144C8。 ##### 2. 设置FFT IP Core 使用“Merge Wizard Plug-in Manager...”进行参数设置、仿真设置及生成操作。 - **参数选择**: - 变换长度选择256。 - FFT Engine Architecture选择Single Output。 - Number选择1。 - I/O Data Flow选择Burst Mode。 - **仿真设置**:如果使用的是非正式许可,则可能不会生成网表。 - **生成IP Core**:完成上述设置后,即可生成FFT IP Core。 ##### 3. 控制逻辑设计 接下来需要编写状态机来控制上述的sink_sop、sink_eop和sink_valid等信号。 ```vhdl library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity ctrl_fft is Port ( reset_n : in STD_LOGIC; clk : in STD_LOGIC; sink_ready : in STD_LOGIC; sink_sop : out STD_LOGIC; sink_eop : out STD_LOGIC; sink_valid : out STD_LOGIC); end ctrl_fft; architecture one of ctrl_fft is constant frame : integer := 256; -- FFT点数 type state is (idle, go, assert_eop, wait_state); signal current_state, next_state : state; signal count, next_count : integer range 0 to frame-1; signal sink_sop_d, sink_eop_d, sink_valid_d : STD_LOGIC; begin process (current_state, sink_ready, count) begin case current_state is when idle => next_count <= 0; if (sink_ready = '1') then next_state <= go; else next_state <= idle; end if; when go => if (count < frame-2) then next_state <= go; next_count <= count + 1; else next_state <= assert_eop; next_count <= count + 1; end if; when assert_eop => next_count <= 0; next_state <= wait_state; when wait_state => if (sink_ready = '1') then next_count <= 0; next_state <= go; else next_count <= count; next_state <= wait_state; end if; end case; end process; sink_sop_d <= '1' when ((next_state = go) and (next_count = 0)) else '0'; sink_eop_d <= '1' when (next_state = assert_eop) else '0'; sink_valid_d <= '1' when (next_state = go or next_state = assert_eop) else '0'; process (clk, reset_n) begin if (reset_n = '0') then current_state <= idle; count <= 0; sink_sop <= '0'; sink_eop <= '0'; sink_valid <= '0'; elsif rising_edge(clk) then current_state <= next_state; count <= next_count; sink_sop <= sink_sop_d; sink_eop <= sink_eop_d; sink_valid <= sink_valid_d; end if; end process; end one; ``` 这段VHDL代码实现了一个简单的状态机,用于生成上述三个控制信号。 #### 五、结论 通过本文的介绍,我们了解到在Quartus II中使用FFT IP Core的基本步骤和注意事项。正确配置FFT IP Core及其控制逻辑是实现高效、准确的FFT计算的关键。希望本文能够帮助读者更好地理解和应用FFT IP Core。

剩余10页未读,继续阅读

cyruscyx2011-10-26就是简单介绍了,希望详细点的好

cyruscyx2011-10-26就是简单介绍了,希望详细点的好

- 粉丝: 55

- 资源: 22

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功