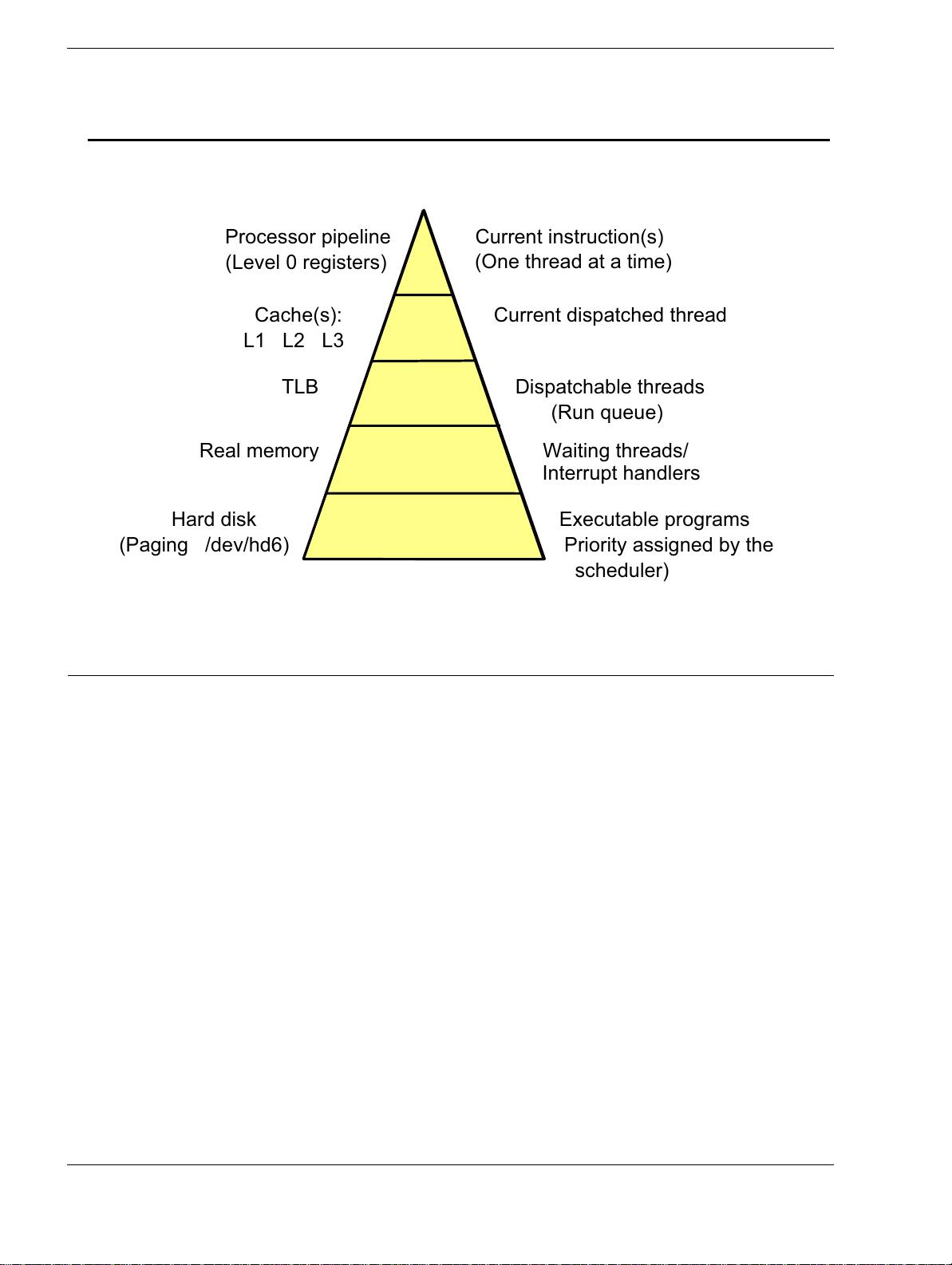

本文档主要围绕AIX系统调校和性能优化的知识点进行介绍,AIX是IBM开发的一套Unix操作系统,它广泛用于中高端服务器领域。在讨论AIX系统调校时,通常会涉及到性能调优的方方面面,包括硬件资源的管理、操作系统内核的设置、处理器流水线的调整、内存管理、以及系统整体性能的优化等。 文中提到了程序执行的层次结构,从程序存储在磁盘上到处理器运行程序指令,涉及了从硬件到操作系统的多个层级。理解这一层次结构对于进行系统调优至关重要。在硬件层次,包括CPU流水线、各级缓存(L1/L2/L3)、TLB(翻译后援缓冲区)、物理内存和硬盘。操作系统层次则包括当前正在执行的指令、可调度线程(运行队列)、等待线程/中断处理程序以及可执行程序(按调度器分配的优先级)。 在硬件层次的每一级,资源都比下一级更加稀缺且昂贵。程序之间存在资源争用,并且在各级之间转移时会花费时间。通常,从一个硬件层级移动到另一个层级所需的时间主要是由下一级别的延迟决定的,即从发起请求到收到第一个数据的时间。程序运行时,它必须沿着硬件和操作系统的层次结构向上移动,大致是并行的。每个层次之间的资源争用和转移时间对于整体性能的影响不容忽视。 文档中还提及,磁盘操作是所有操作中最慢的,程序从磁盘获取代码或数据的等待时间是漫长且消耗时间的,因此在调优时,通常需要寻找不必要的磁盘输入输出(I/O)操作,或寻找磁盘瓶颈。 随机存取存储器(RAM)的访问速度比磁盘快很多,但每个字节的成本更高。操作系统会尽可能地将正在使用的程序代码和数据保留在RAM中。当操作系统开始耗尽可用的RAM时,它需要做出决策来管理内存。 从上述内容可以提炼出以下知识点: 1. 程序执行层次结构:了解程序从磁盘存储到处理器执行的整个层级过程,包括硬件和操作系统中涉及的各个组件和过程。 2. 硬件资源管理:理解CPU流水线、缓存、TLB、物理内存和硬盘在程序执行过程中的作用和资源限制。 3. 系统性能调优:在进行系统调优时,重点关注磁盘I/O操作,优化页面调度减少页面交换,以及合理分配和管理物理内存,减少不必要的内存交换。 4. 内存管理策略:在内存紧张时,操作系统如何做出决策来决定哪些数据留在物理内存中,哪些被换出到硬盘上的交换空间(例如/dev/hd6)。 整体而言,AIX系统调校是一个复杂的过程,它要求系统管理员具备深厚的系统知识、对系统性能瓶颈有敏锐的洞察力,以及丰富的实践经验来调整系统参数,达到提升系统性能的目标。而本文档通过具体的程序执行层次结构和硬件资源管理的介绍,为AIX系统调校和性能优化提供了理论基础和实操指南。

剩余90页未读,继续阅读

- 粉丝: 0

- 资源: 37

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功