February 2021 RM0090 Rev 19 1/1751

1

RM0090

Reference manual

STM32F405/415, STM32F407/417, STM32F427/437 and

STM32F429/439 advanced Arm

®

-based 32-bit MCUs

Introduction

This reference manual targets application developers. It provides complete information on

how to use the STM32F405xx/07xx, STM32F415xx/17xx, STM32F42xxx and

STM32F43xxx microcontroller memory and peripherals.

The STM32F405xx/07xx, STM32F415xx/17xx, STM32F42xxx and STM32F43xxx constitute

a family of microcontrollers with different memory sizes, packages and peripherals.

For ordering information, mechanical and electrical device characteristics please refer to the

datasheets.

For information on the Arm

®

Cortex

®

-M4 with FPU core, please refer to the Cortex

®

-M4 with

FPU Technical Reference Manual.

Related documents

Available from STMicroelectronics web site (http://www.st.com):

• STM32F40x and STM32F41x datasheets

• STM32F42x and STM32F43x datasheets

• For information on the Arm

®

Cortex

®

-M4 with FPU, refer to the STM32F3xx/F4xxx

Cortex

®

-M4 with FPU programming manual (PM0214).

www.st.com

Contents RM0090

2/1751 RM0090 Rev 19

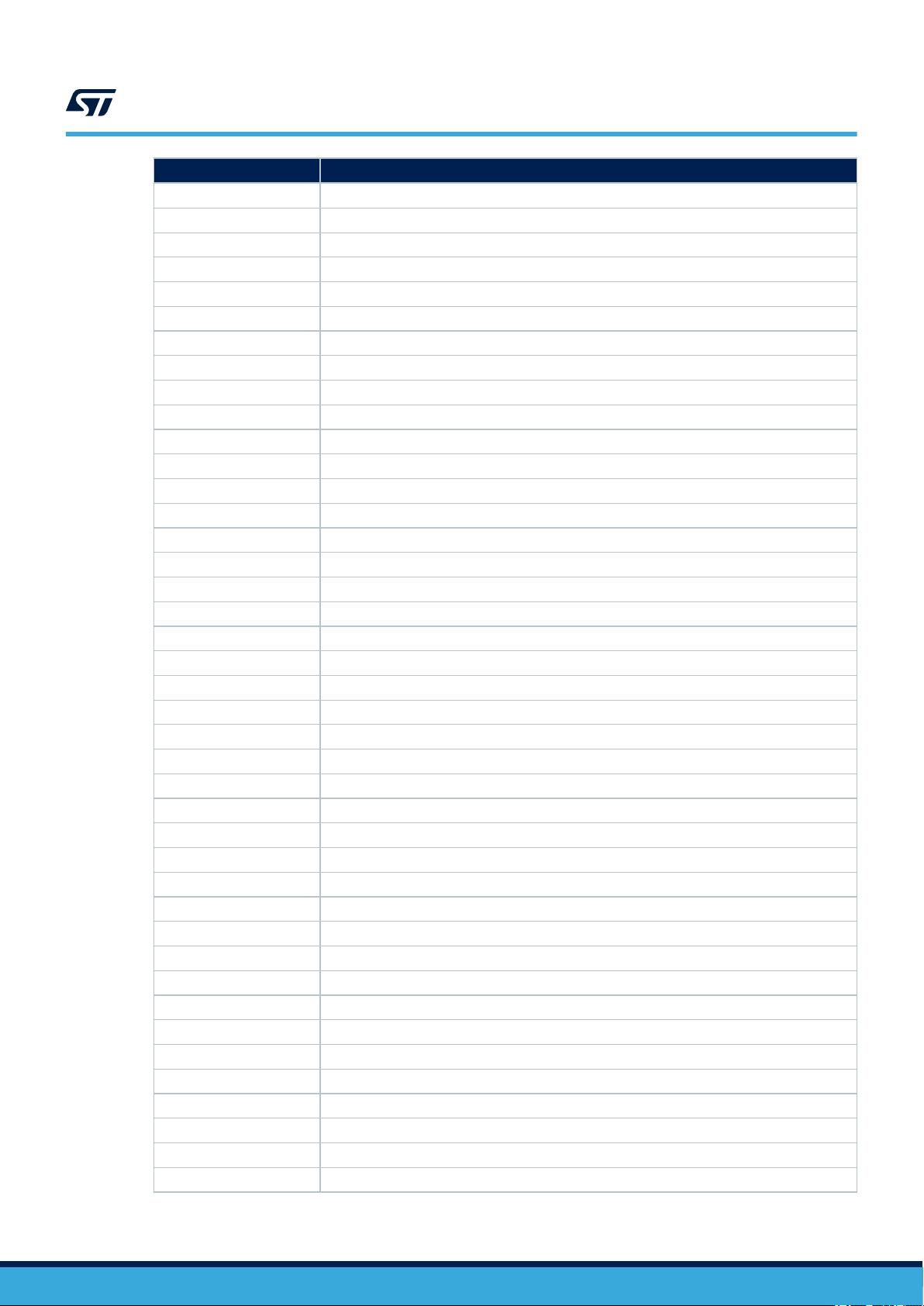

Contents

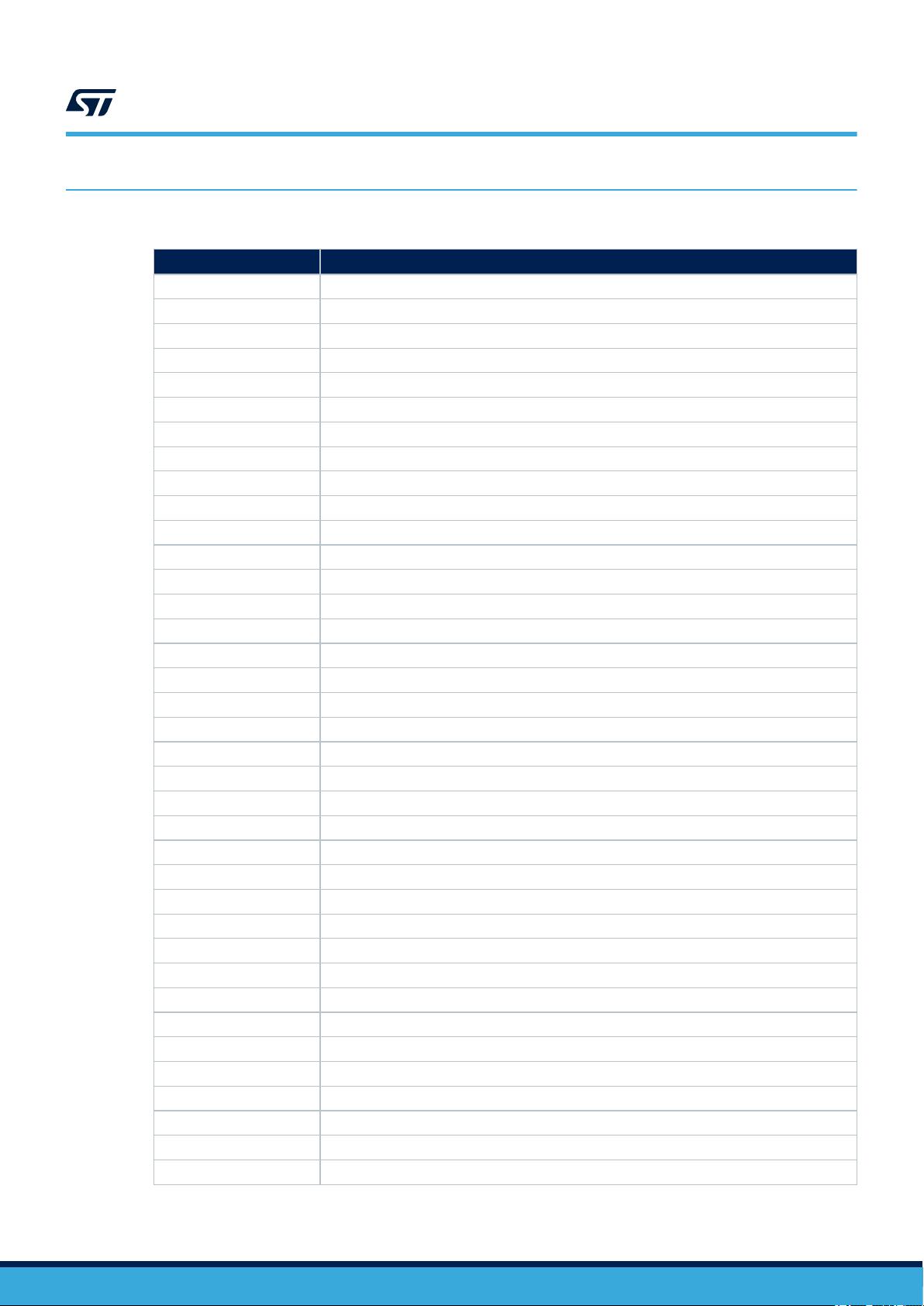

1 Documentation conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

1.1 List of abbreviations for registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

1.2 Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

1.3 Peripheral availability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

2 Memory and bus architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

2.1 System architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

2.1.1 I-bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

2.1.2 D-bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

2.1.3 S-bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

2.1.4 DMA memory bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

2.1.5 DMA peripheral bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

2.1.6 Ethernet DMA bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

2.1.7 USB OTG HS DMA bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

2.1.8 LCD-TFT controller DMA bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

2.1.9 DMA2D bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

2.1.10 BusMatrix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

2.1.11 AHB/APB bridges (APB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

2.2 Memory organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

2.3 Memory map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

2.3.1 Embedded SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

2.3.2 Flash memory overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

2.3.3 Bit banding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

2.4 Boot configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

3 Embedded Flash memory interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

3.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

3.2 Main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

3.3 Embedded Flash memory in

STM32F405xx/07xx and STM32F415xx/17xx . . . . . . . . . . . . . . . . . . . . . 74

3.4 Embedded Flash memory in STM32F42xxx and STM32F43xxx . . . . . . . 76

3.5 Read interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

3.5.1 Relation between CPU clock frequency and Flash memory read time . 80

RM0090 Rev 19 3/1751

RM0090 Contents

39

3.5.2 Adaptive real-time memory accelerator (ART Accelerator™) . . . . . . . . 82

3.6 Erase and program operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

3.6.1 Unlocking the Flash control register . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

3.6.2 Program/erase parallelism . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

3.6.3 Erase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

3.6.4 Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

3.6.5 Read-while-write (RWW) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

3.6.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

3.7 Option bytes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

3.7.1 Description of user option bytes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

3.7.2 Programming user option bytes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

3.7.3 Read protection (RDP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

3.7.4 Write protections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

3.7.5 Proprietary code readout protection (PCROP) . . . . . . . . . . . . . . . . . . . 95

3.8 One-time programmable bytes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

3.9 Flash interface registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

3.9.1 Flash access control register (FLASH_ACR)

for STM32F405xx/07xx and STM32F415xx/17xx . . . . . . . . . . . . . . . . . 98

3.9.2 Flash access control register (FLASH_ACR)

for STM32F42xxx and STM32F43xxx . . . . . . . . . . . . . . . . . . . . . . . . . . 99

3.9.3 Flash key register (FLASH_KEYR) . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

3.9.4 Flash option key register (FLASH_OPTKEYR) . . . . . . . . . . . . . . . . . . 100

3.9.5 Flash status register (FLASH_SR) for

STM32F405xx/07xx and STM32F415xx/17xx . . . . . . . . . . . . . . . . . . . 101

3.9.6 Flash status register (FLASH_SR) for

STM32F42xxx and STM32F43xxx . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

3.9.7 Flash control register (FLASH_CR) for

STM32F405xx/07xx and STM32F415xx/17xx . . . . . . . . . . . . . . . . . . . 103

3.9.8 Flash control register (FLASH_CR) for

STM32F42xxx and STM32F43xxx . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

3.9.9 Flash option control register (FLASH_OPTCR) for

STM32F405xx/07xx and STM32F415xx/17xx . . . . . . . . . . . . . . . . . . . 106

3.9.10 Flash option control register (FLASH_OPTCR)

for STM32F42xxx and STM32F43xxx . . . . . . . . . . . . . . . . . . . . . . . . . 108

3.9.11 Flash option control register (FLASH_OPTCR1)

for STM32F42xxx and STM32F43xxx . . . . . . . . . . . . . . . . . . . . . . . . . 110

3.9.12 Flash interface register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

4 CRC calculation unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Contents RM0090

4/1751 RM0090 Rev 19

4.1 CRC introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113

4.2 CRC main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113

4.3 CRC functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .114

4.4 CRC registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .114

4.4.1 Data register (CRC_DR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

4.4.2 Independent data register (CRC_IDR) . . . . . . . . . . . . . . . . . . . . . . . . 114

4.4.3 Control register (CRC_CR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

4.4.4 CRC register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

5 Power controller (PWR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

5.1 Power supplies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .116

5.1.1 Independent A/D converter supply and reference voltage . . . . . . . . . . 117

5.1.2 Battery backup domain . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

5.1.3 Voltage regulator for STM32F405xx/07xx and STM32F415xx/17xx . . 120

5.1.4 Voltage regulator for STM32F42xxx and STM32F43xxx . . . . . . . . . . . 121

5.2 Power supply supervisor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

5.2.1 Power-on reset (POR)/power-down reset (PDR) . . . . . . . . . . . . . . . . . 124

5.2.2 Brownout reset (BOR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

5.2.3 Programmable voltage detector (PVD) . . . . . . . . . . . . . . . . . . . . . . . . 125

5.3 Low-power modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

5.3.1 Slowing down system clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

5.3.2 Peripheral clock gating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

5.3.3 Sleep mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

5.3.4 Stop mode (STM32F405xx/07xx and STM32F415xx/17xx) . . . . . . . . 130

5.3.5 Stop mode (STM32F42xxx and STM32F43xxx) . . . . . . . . . . . . . . . . . 133

5.3.6 Standby mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

5.3.7 Programming the RTC alternate functions to wake up the device from

the Stop and Standby modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

5.4 Power control registers (STM32F405xx/07xx and STM32F415xx/17xx) 141

5.4.1 PWR power control register (PWR_CR)

for STM32F405xx/07xx and STM32F415xx/17xx . . . . . . . . . . . . . . . . 141

5.4.2 PWR power control/status register (PWR_CSR)

for STM32F405xx/07xx and STM32F415xx/17xx . . . . . . . . . . . . . . . . 142

5.5 Power control registers (STM32F42xxx and STM32F43xxx) . . . . . . . . . 144

5.5.1 PWR power control register (PWR_CR)

for STM32F42xxx and STM32F43xxx . . . . . . . . . . . . . . . . . . . . . . . . . 144

5.5.2 PWR power control/status register (PWR_CSR)

for STM32F42xxx and STM32F43xxx . . . . . . . . . . . . . . . . . . . . . . . . . 147

RM0090 Rev 19 5/1751

RM0090 Contents

39

5.6 PWR register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

6 Reset and clock control for

STM32F42xxx and STM32F43xxx (RCC) . . . . . . . . . . . . . . . . . . . . . . . 150

6.1 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

6.1.1 System reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

6.1.2 Power reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

6.1.3 Backup domain reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

6.2 Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

6.2.1 HSE clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

6.2.2 HSI clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

6.2.3 PLL configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

6.2.4 LSE clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

6.2.5 LSI clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

6.2.6 System clock (SYSCLK) selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

6.2.7 Clock security system (CSS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

6.2.8 RTC/AWU clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

6.2.9 Watchdog clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

6.2.10 Clock-out capability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

6.2.11 Internal/external clock measurement using TIM5/TIM11 . . . . . . . . . . . 158

6.3 RCC registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

6.3.1 RCC clock control register (RCC_CR) . . . . . . . . . . . . . . . . . . . . . . . . . 161

6.3.2 RCC PLL configuration register (RCC_PLLCFGR) . . . . . . . . . . . . . . . 163

6.3.3 RCC clock configuration register (RCC_CFGR) . . . . . . . . . . . . . . . . . 165

6.3.4 RCC clock interrupt register (RCC_CIR) . . . . . . . . . . . . . . . . . . . . . . . 167

6.3.5 RCC AHB1 peripheral reset register (RCC_AHB1RSTR) . . . . . . . . . . 170

6.3.6 RCC AHB2 peripheral reset register (RCC_AHB2RSTR) . . . . . . . . . . 173

6.3.7 RCC AHB3 peripheral reset register (RCC_AHB3RSTR) . . . . . . . . . . 174

6.3.8 RCC APB1 peripheral reset register (RCC_APB1RSTR) . . . . . . . . . . 174

6.3.9 RCC APB2 peripheral reset register (RCC_APB2RSTR) . . . . . . . . . . 178

6.3.10 RCC AHB1 peripheral clock register (RCC_AHB1ENR) . . . . . . . . . . . 180

6.3.11 RCC AHB2 peripheral clock enable register (RCC_AHB2ENR) . . . . . 182

6.3.12 RCC AHB3 peripheral clock enable register (RCC_AHB3ENR) . . . . . 183

6.3.13 RCC APB1 peripheral clock enable register (RCC_APB1ENR) . . . . . 183

6.3.14 RCC APB2 peripheral clock enable register (RCC_APB2ENR) . . . . . 187

6.3.15 RCC AHB1 peripheral clock enable in low power mode register

(RCC_AHB1LPENR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

评论6