没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

PowerPC CPU Primer

Mingkai Hu

Agenda

About CPU

About U-Boot/Linux and Opensource

About board bringup

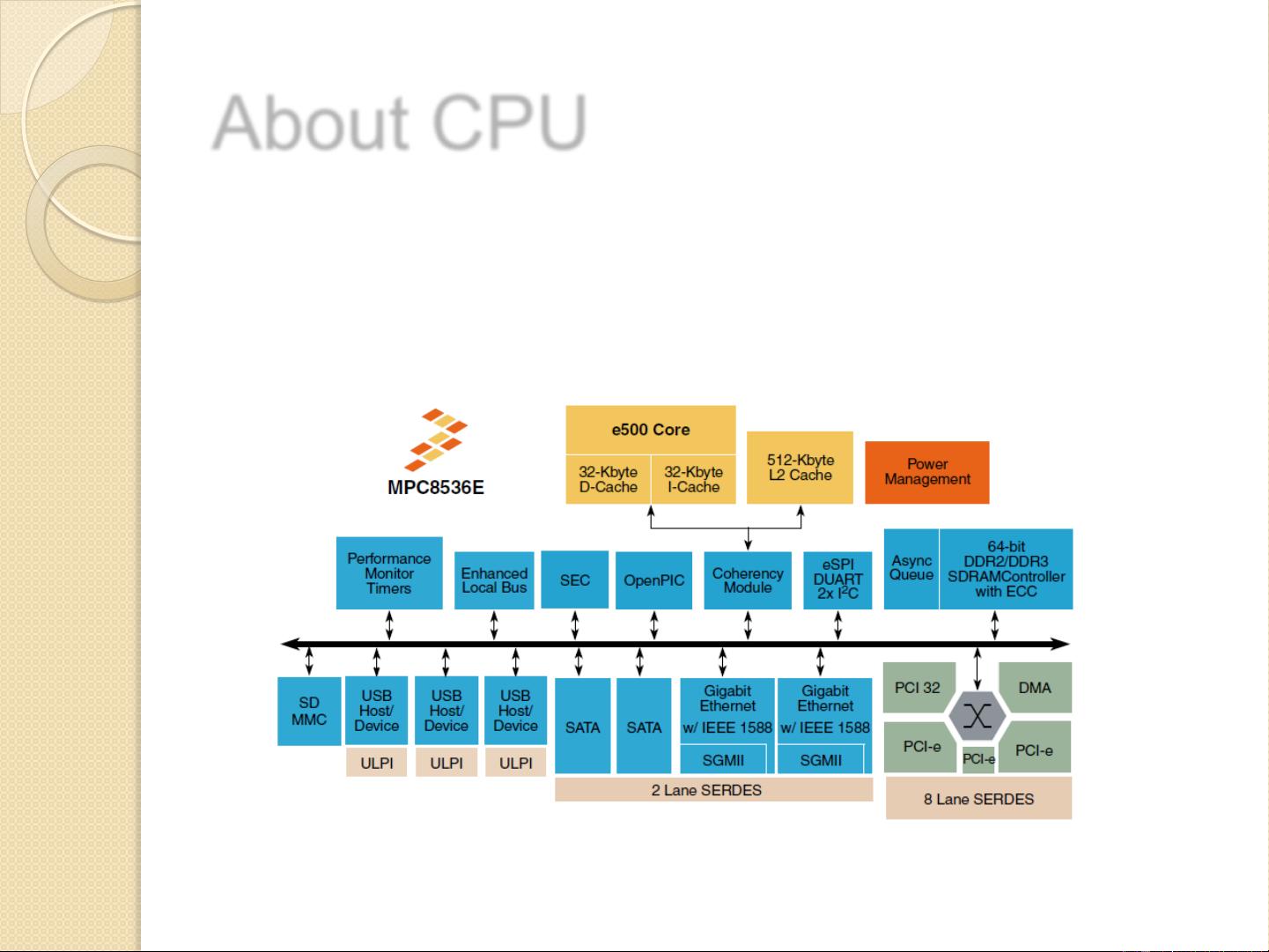

About CPU

SOC (system on chip)

◦ Include core(s) and peripheral IP blocks, such as DDR controller, Interrupt

controller, DMA, PCIe, USB, eLBC, eSPI etc.

About CPU

Where does the CPU core run when it starts up?

◦ 0xFFFFFFFC

◦ -> what’s the content of the address 0xFFFFFFFC?

How does the CPU core access the different IP blocks?

◦ LAW (Local Access Window): associate a range of 36-bit address space with a

particular target interface.

0x0000_0000 0x7fff_ffff DDR 2G Cacheable

0x8000_0000 0xbfff_ffff PCI Express Mem 1G non-cacheable

◦ CCSRBAR – define a window used to access all memory-mapped CCSR

0xffe0_0000 0xffef_ffff CCSR 1M non-cacheable

◦ SRAM window – define a window used to access the SRAM configured by L2 Cache

Must disable the Multiple-bit/Single-bit ECC error

Does the core use physical address or effective address to access the

IP blocks?

◦ Physical address

How does the effective address translate to physical address?

◦ TLB (Translation Lookaside buffer)

◦ TLB 0 and TLB1

What’s the difference?

How does the Linux kernel or U-Boot use them?

What’s the relationship between TLB and Linux kernel page table?

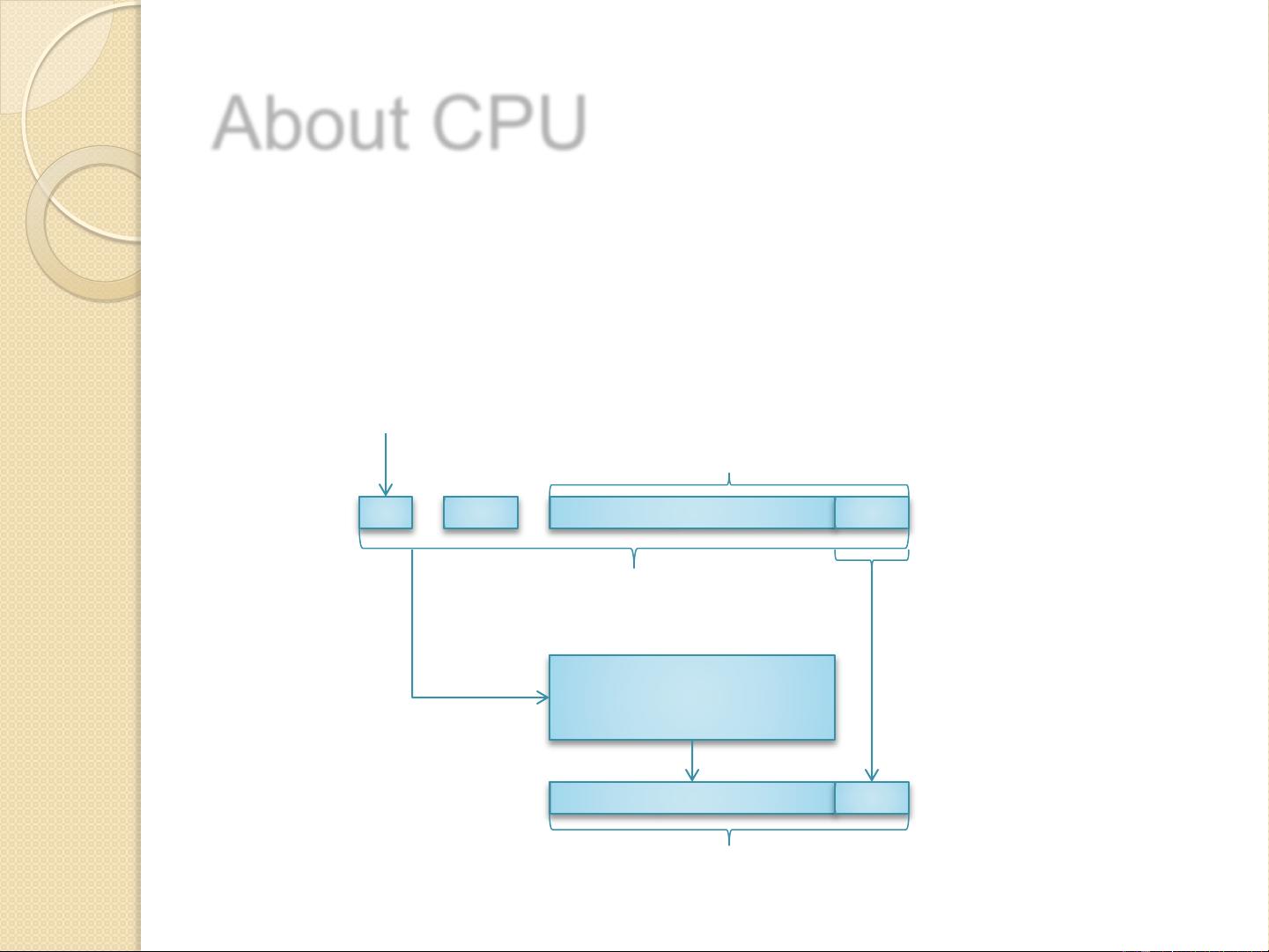

About CPU

Type of address in e500v1/v2/mc

◦ Effective address (EA)

◦ Virtual address (VA)

◦ Physical address (PA)

AS PID Effective Page Number (EPN) offset

41 bit Virtual Address (VAs)

32-bit Effective Address

Real Page Number (RPN) offset

V1: 32-bit Physical Address

V2/mc: 36-bit Physical Address

MSR[DS] for data access

MSR[IS] for instruction access

TLB

剩余24页未读,继续阅读

mingkai_hu

- 粉丝: 12

- 资源: 3

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

- 1

- 2

前往页