TMS320C64x 学习笔记(2) http://www.eXtremeDSP.com

TMS320C64x

学习笔记(2)

作者:DSP 探路者

Email:franklejins@tom.com

http://www.eXtremeDSP.com

DSP 探路者 第 1 页 2007-7-20

TMS320C64x 学习笔记(2) http://www.eXtremeDSP.com

1. TMS320C64x 的主要外设

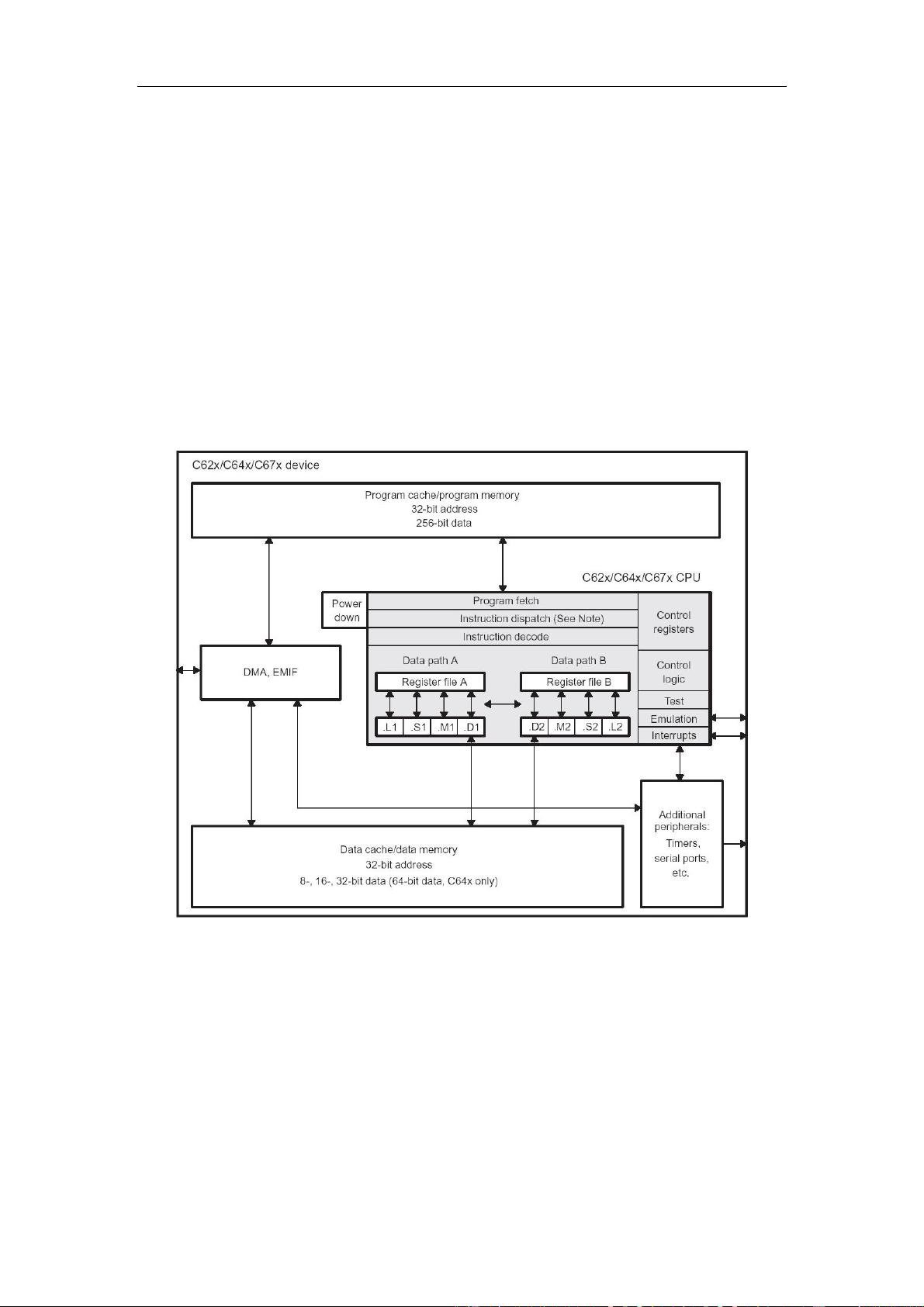

C6000 系列 DSPs 不仅运算速度快,而且片内集成了很多外围设备,支持多种工业标

准的接口协议,能够提供高带宽的数据 I/O 能力。这些特点使 C6000 系列 DSPs 获得了很

高的综合性能。图 3.1 是 C6418 芯片的结构框图。

下面对 C64x 的片内集成外设,结合实际的使用情况,作一简单介绍,详细的说明参见

文档:《TMS320C6000 DSP Peripherals Overview Reference Guide》,TI 文档编号

SPRU190D。

图 3.1 C6418 芯片的结构框图

1.1. 扩展/外部存储器接口(EMIF 和 EMIFA)

DSPs 访问片外存储器时必须通过外部存储器接口,C6000 系列 DSPs 的 EMIF 具有很

强的接口能力,不仅具有很高的数据吞吐率,而且可以与目前几乎所有类型的存储器直接接

口。这些存储器包括:

z 流水结构的同步突发静态 RAM(SBSRAM)

z 同步动态 RAM(SDRAM)

z 异步器件,包括 SRAM、ROM 和 FIFO 等

DSP 探路者 第 2 页 2007-7-20

TMS320C64x 学习笔记(2) http://www.eXtremeDSP.com

z 外部共享存储空间的设备

C64x 具有两个独立的 EMIF:EMIFA 和 EMIFB。EMIFA 提供 64bit 宽度的外总线数据

接口,EMIFB 提供 16bit 宽度的外总线数据接口。C64x 增强了原有的 SBSRAM 接口,提

供可编程的同步接口模式。图 3.2 给出了 C64x 的 EMIF 接口信号。

图 3.2 C64x 的 EMIF 接口信号

虽然 C64x提供 32bit的地址寻址能力,但是经过 EMIF直接输出的地址信号只有 EA[21:

3]。一般情况下 EA2 信号对应于逻辑地址 A2,但这并不意味着 C64 处理器只能进行 32bit

或者 64bit,实际上内部 32bit 地址的最低两位经过译码后由 BEx 输出,是能够控制字节访

问的。某些情况下,EA2 还可能对应最低位逻辑地址 A0,甚至对应逻辑地址 A11。更高位

的逻辑地址经过译码后输出 EA[3:0]。

C64x 的 EMIFA 支持 8/16/32/64bit 的数据访问,EMIFB 支持 8/16bit 的数据访问,同

样支持 little-endian 和 big-endian 模式。表 3.1 总结了 C64x 的寻址能力。

表 3.1 C64x 的寻址能力

存储器类型

存储器宽度

每个

CE

空间最大

可寻址范围

EA[21:2](EMIFA)

EA[20:1](EMIFB)

输出的逻辑地址

含义

X8 1MB A[19:0]

字节地址

X16 2MB A[20:1]

半字地址

X32 4MB A[21:2]

字地址

ASRAM

X64 8MB A[22:3]

双字地址

X8 1MB A[19:0]

字节地址

X16 2MB A[20:1]

半字地址

可编程同步

存储器

X32 4MB A[21:2]

字地址

DSP 探路者 第 3 页 2007-7-20

TMS320C64x 学习笔记(2) http://www.eXtremeDSP.com

X64 8MB A[22:3]

双字地址

EMIF 接口有一组存储器映射的寄存器进行维护与控制,包括配置各个空间的存储器类

型和设置读写时序等,如表 3.2 所示

表 3.2 EMIF 控制寄存器

前面曾经提到,C64x 的 EMIF 接口可以与多种外部存储器接口。考虑到目前实际仅仅

与 FPGA 相连接,映射为 C64x 的存储器,所以这里只讨论 EMIF 的异步接口。

EMIF 的异步接口提供 4 个控制信号(见表 3.3),这 4 个控制信号可以通过不同的组合

实现与不同类型的异步器件的无缝接口。EMIF 的 CExCTL 寄存器负责设置异步读写操作的

接口时序,以满足对不同速度的异步器件的存取。

表 3.3 异步接口信号

EMIF 异步接口信号 功能

/AOE

输出允许,在整个读周期中有效

/AWE

写允许,在写周期中触发阶段保持有效

/ARE

读允许,在读周期中触发阶段保持有效

ARDY

Ready 信号,插入等待

图 3.3 是 EMIF 与 32bit 异步 SRAM 的接口示意图。由图可以看出,这里只使用了/AOE

和/AWE 信号,没有使用/ARE 和 ARDY 信号。

DSP 探路者 第 4 页 2007-7-20

TMS320C64x 学习笔记(2) http://www.eXtremeDSP.com

图 3.3EMIF 与 32bit 的 ASRAM 的接口

EMIF 的异步接口的可编程性好,每个读/写周期由 3 个阶段构成:建立时间(Setup)、

触发时间(Strobe)和保持时间(Hold)。各自定义如下:

z 建立时间 从存储器访问周期开始到读/写选通信号有效之前

z 触发时间 读/写选通信号从有效到无效

z 保持时间 从读/写选通信号无效到访问周期结束

图 3.4 和图 3.5 分别给出了 EMIF 接口异步读/写的时序的例子。

图 3.4 EMIF 的异步读时序

DSP 探路者 第 5 页 2007-7-20

评论0