www.Micrium.com

µC/OS-II for ARM Processors

(Supplement to AN-1014)

ARM and Thumb Mode

µC/OS-II for ARM Processors

(Supplement to AN-1014)

ARM and Thumb Mode

© 2005, Micriµm, Inc., All Rights Reserved

© 2005, Micriµm, Inc., All Rights Reserved

µC/OS-II Port for ARM Processors

µC/OS-II Port for ARM Processors

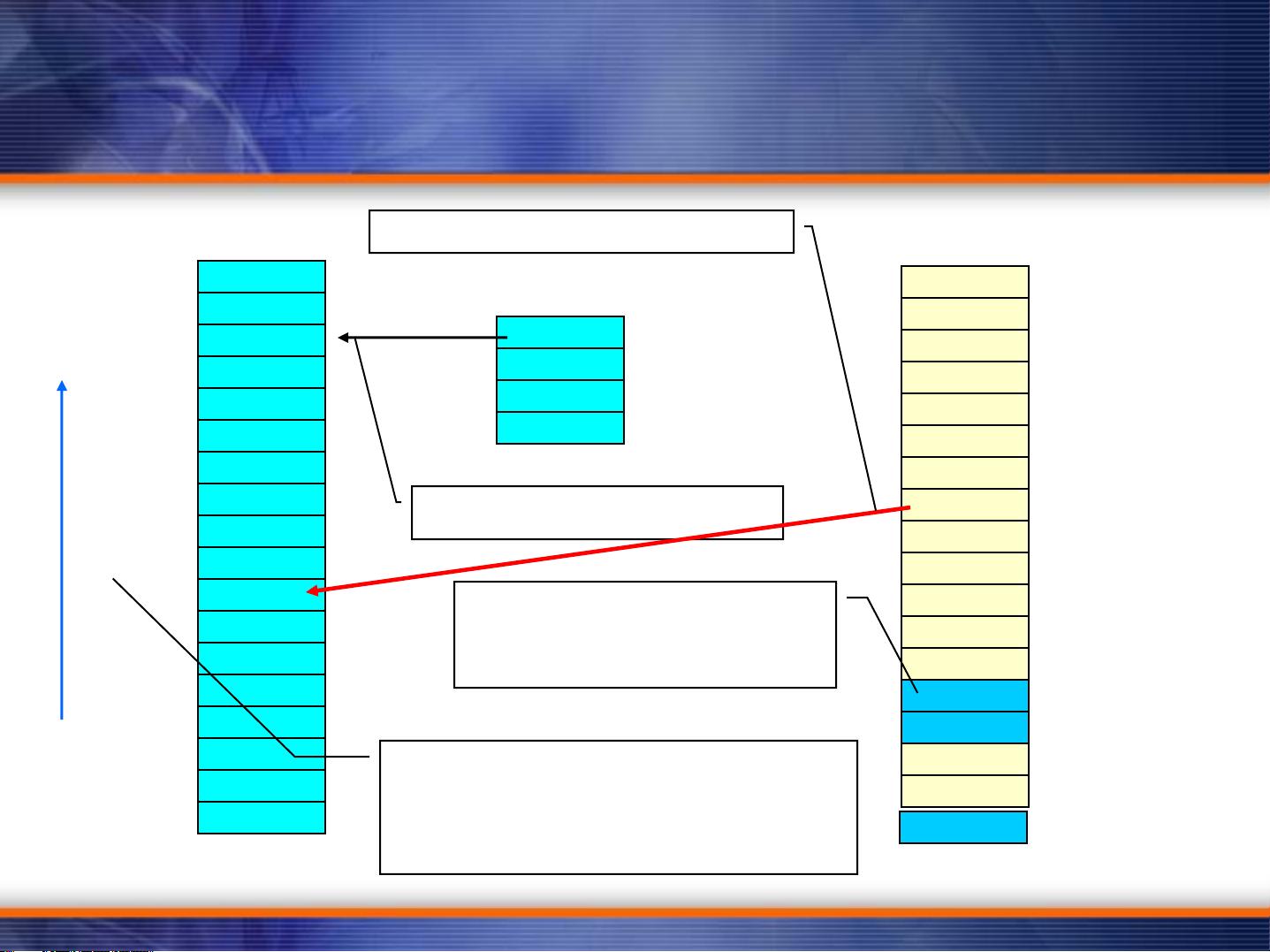

Legend

Legend

Task Stack

R14_svc (LR)

R12

R11

R10

R9

R8

R7

R6

R5

R3

R2

R1

R0

R4

CPSR

OSTCBStkPtr

Task’s

OS_TCB

R13_svc (SP)

R14_svc (LR)

R12

R11

R10

R9

R8

R7

R6

R5

R3

R2

R1

R0

R4

CPSR

R15 (PC)

CPU Registers

SVC Mode

As a convention, we will show stack

growth going from the bottom of the

page up to show that items are stacked

one on top of the other.

A black line indicates a pointer.

PC

Registers in beige are common

registers. Registers in blue are

mode specific registers.

A red line shows data being copied.

SPSR_svc

LOW

Memory

Stack

Growth

HIGH

Memory

© 2005, Micriµm, Inc., All Rights Reserved

© 2005, Micriµm, Inc., All Rights Reserved

µC/OS-II Port for ARM Processors

µC/OS-II Port for ARM Processors

Table of Contents

Table of Contents

Task Level Context Switch – OSCtxSw()

Servicing Interrupts – IRQ

Servicing Interrupts - FIQ

Interrupt Level Context Switch - OS_IntCtxSw()

© 2005, Micriµm, Inc., All Rights Reserved

© 2005, Micriµm, Inc., All Rights Reserved

µC/OS-II Port for ARM Processors

µC/OS-II Port for ARM Processors

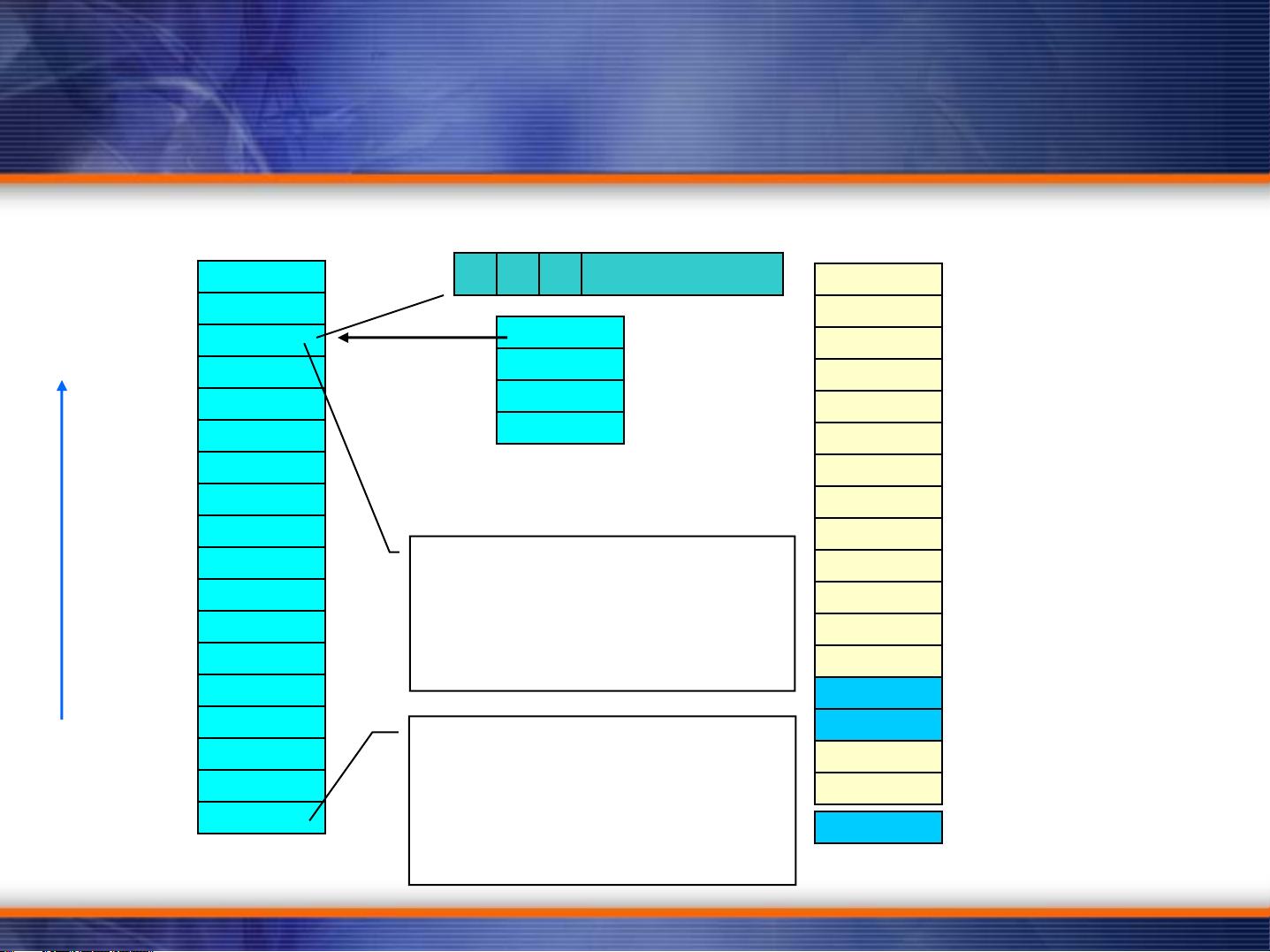

Task Level Context Switch

Task Stack Frame (when task is created)

Task Level Context Switch

Task Stack Frame (when task is created)

IFT MODE

Task Stack

R14_svc (LR)

R12

R11

R10

R9

R8

R7

R6

R5

R3

R2

R1

R0

R4

CPSR

OSTCBStkPtr

Task’s

OS_TCB

When the task is created, this

contains the starting address of

the task. This entry contains the

address of the task to resume if

the task is preempted.

The CPSR of the task have

interrupts enabled and the T-bit

set to 0 indicating that task runs

in ARM mode or 1 for Thumb

mode.

PC

LOW

Memory

CPSR: 00

0/1 0x13

R13_svc (SP)

R14_svc (LR)

R12

R11

R10

R9

R8

R7

R6

R5

R3

R2

R1

R0

R4

CPSR

R15 (PC)

CPU Registers

SVC Mode

Stack

Growth

HIGH

Memory

SPSR_svc

© 2005, Micriµm, Inc., All Rights Reserved

© 2005, Micriµm, Inc., All Rights Reserved

µC/OS-II Port for ARM Processors

µC/OS-II Port for ARM Processors

Task Level Context Switch

Task running

Task Level Context Switch

Task running

A task is assumed to run (ARM or Thumb mode),

uses the SVC registers (Mode = 0x13).

The processor’s SP (R13) points to a location

into the current task’s stack.

If a context switch needs to take place, µC/OS-

II will call OS_Sched() which in turn calls

OS_TASK_SW() as shown in the call tree below:

OSTimeDly(1) // Delay task for 1 tick

OS_Sched();

OS_TASK_SW(); // Macro that invokes …

OSCtxSw(); // … this function.

R13_svc (SP)

R14_svc (LR)

R12

R11

R10

R9

R8

R7

R6

R5

R3

R2

R1

R0

R4

CPSR

R15 (PC)

IFT MODE

Notes:

Interrupts are DISABLED during a task-level

context switch. Interrupts are disabled at

the beginning of OS_Sched() and thus the I-

bit and F-bit are both set to 1.

CPSR: 11

0/1 0x13

SPSR_svc

Current Task

Stack

SVC

Mode

评论2