FPGA 设计流程指南

前言

本部门所承担的 FPGA 设计任务主要是两方面的作用:系统的原型实现和 ASIC 的原

型验证。编写本流程的目的是:

在于规范整个设计流程,实现开发的合理性、一致性、高效性。

形成风格良好和完整的文档。

实现在 FPGA 不同厂家之间以及从 FPGA 到 ASIC 的顺利移植。

便于新员工快速掌握本部门 FPGA 的设计流程。

由于目前所用到的 FPGA 器件以 Altera 的为主,所以下面的例子也以 Altera 为例,工

具组合为 modelsim + LeonardoSpectrum/FPGACompilerII + Quartus,但原则和方法对于其他

厂家和工具也是基本适用的。

目 录

前言.....................................................................................................................................................1

目 录............................................................................................................................................2

1. 基于 HDL 的 FPGA 设计流程概述...............................................................................................1

1.1 设计流程图...........................................................................................................................1

1.2 关键步骤的实现...................................................................................................................2

1.2.1 功能仿真....................................................................................................................2

1.2.2 逻辑综合....................................................................................................................2

1.2.3 前仿真........................................................................................................................3

1.2.4 布局布线....................................................................................................................3

1.2.5 后仿真(时序仿真)................................................................................................4

2. Verilog HDL 设计...........................................................................................................................4

2.1 编程风格(Coding Style)要求..........................................................................................4

2.1.1 文件............................................................................................................................4

2.1.2 大小写........................................................................................................................5

2.1.3 标识符........................................................................................................................5

2.1.4 参数化设计................................................................................................................5

2.1.5 空行和空格................................................................................................................5

2.1.6 对齐和缩进................................................................................................................5

2.1.7 注释............................................................................................................................6

2.1.8 参考 C 语言的资料...................................................................................................6

2.1.9 可视化设计方法........................................................................................................6

2.2 可综合设计...........................................................................................................................6

2.3 设计目录...............................................................................................................................6

3. 逻辑仿真.........................................................................................................................................7

3.1 测试程序(test bench).......................................................................................................7

3.2 使用预编译库.......................................................................................................................7

4. 逻辑综合.........................................................................................................................................8

4.1 逻辑综合的一些原则...........................................................................................................8

4.1.1 关于 LeonardoSpectrum............................................................................................8

4.1.1 大规模设计的综合....................................................................................................9

4.1.3 必须重视工具产生的警告信息...............................................................................9

4.2 调用模块的黑盒子(Black box)方法..............................................................................9

参考...................................................................................................................................................10

修订纪录...........................................................................................................................................11

1. 基于 HDL 的 FPGA 设计流程概述

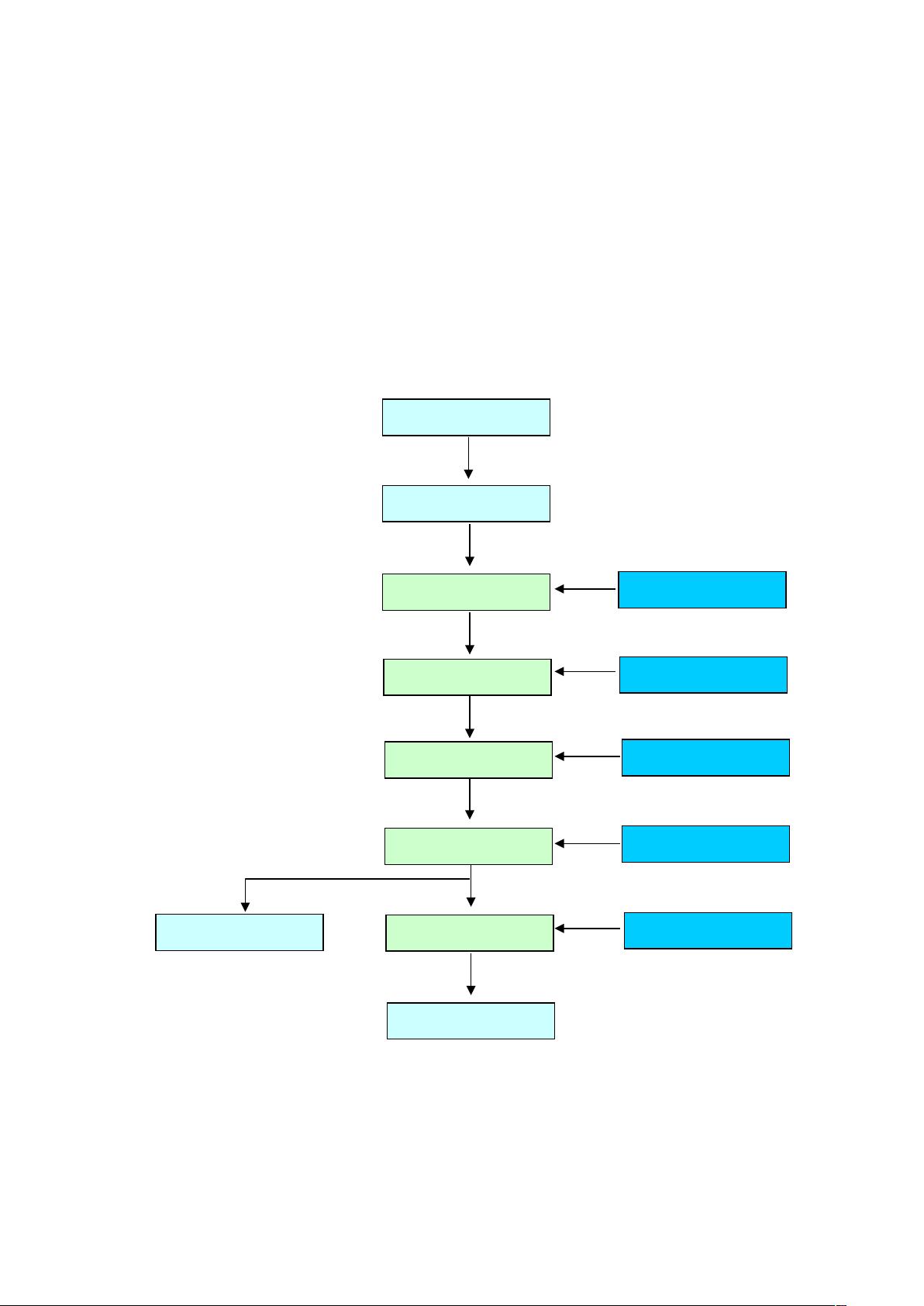

1.1 设计流程图

说明:

逻辑仿真器主要指 modelsim,Verilog-XL 等。

1

( 1 )设计定义

( 2 ) HDL 实现

( 3 )功能仿真

( 4 )逻辑综合

( 5 )前仿真

( 6 )布局布线

( 7 )后仿真

( 9 )在系统测试

逻辑仿真器

逻辑综合器

FPGA 厂家工具

逻辑仿真器

逻辑仿真器

( 8 )静态时序分

析

逻辑综合器主要指 LeonardoSpectrum、Synplify、FPGA Express/FPGA Compiler 等。

FPGA 厂 家 工 具 指 的 是 如 Altera 的 Max+PlusII 、 QuartusII , Xilinx 的

Foundation、Alliance、ISE4.1 等。

1.2 关键步骤的实现

1.2.1 功能仿真

说明:

“调用模块的行为仿真模型”指的是 RTL 代码中引用的由厂家提供的宏模块/IP,如

Altera 提供的 LPM 库中的乘法器、存储器等部件的行为模型。

1.2.2 逻辑综合

2

RTL 代码

逻辑仿真器

RTL 代码

逻辑综合器

调用模块的

行为仿真模型

测试数据

调用模块的

黑盒子接口

设置综合目

标和约束条

件

EDIF 网表

( netlist

)

HDL 网表

( netlist

)

测试程序

( test

bench )