Chapter 1. Introduction

The document describes the flow of setting up analog mixed signal simulation TB and

test case for CPS mixed signal chip. Generally, content is based on cadence spectre AMS

designer flow, may related to both graphic user interface and command line user interface

usage for the convenience needed.

Spectre AMS designer is a single executable, mixed signal solution for the design and

verification of mixed signal chip. It contains the spectre AMS connector, which invokes analog

engines, like Spectre/SpectreAPS/SpectreX for analog content, and digital engine Xcelium for

digital content, and as a single process, the analog engine and digital engine share the same

memory accessed, where much benefit is gained as no inter process communication is

needed.

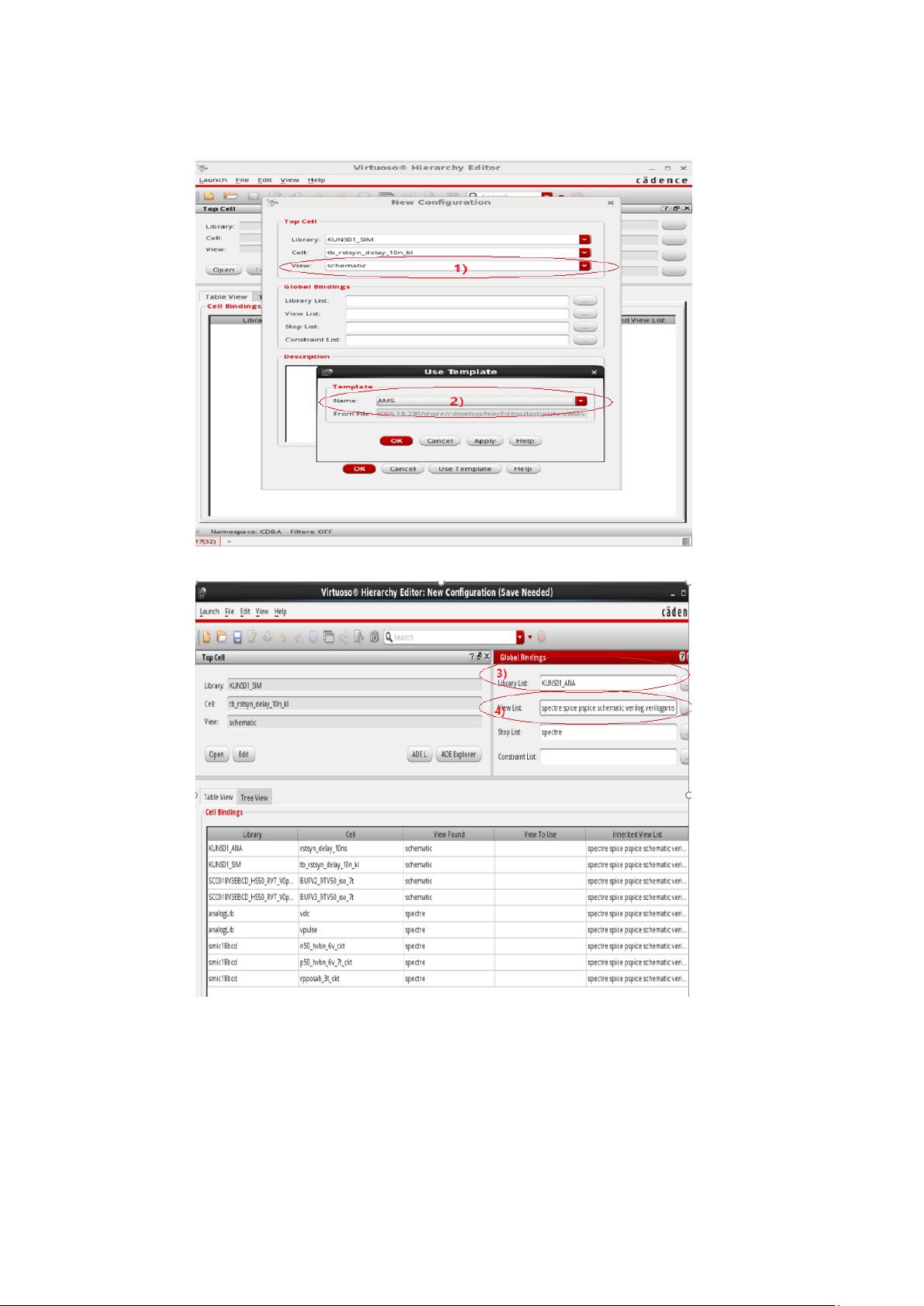

There are two usage model for Spectre AMS designer, one is in graphic user interface,

generally name AVUM(AMS Virtuoso Use Model),shown as Figure1, it starts from analog

schematic input, building config view in hierarchy editor, netlisting(UNL) and running

simulation in ADE/ADEXL/ADE Explorer/Assembler, which is quite friendly for analog designer

and generally suitable for analog block level simulation or analog-centric(analog on top)

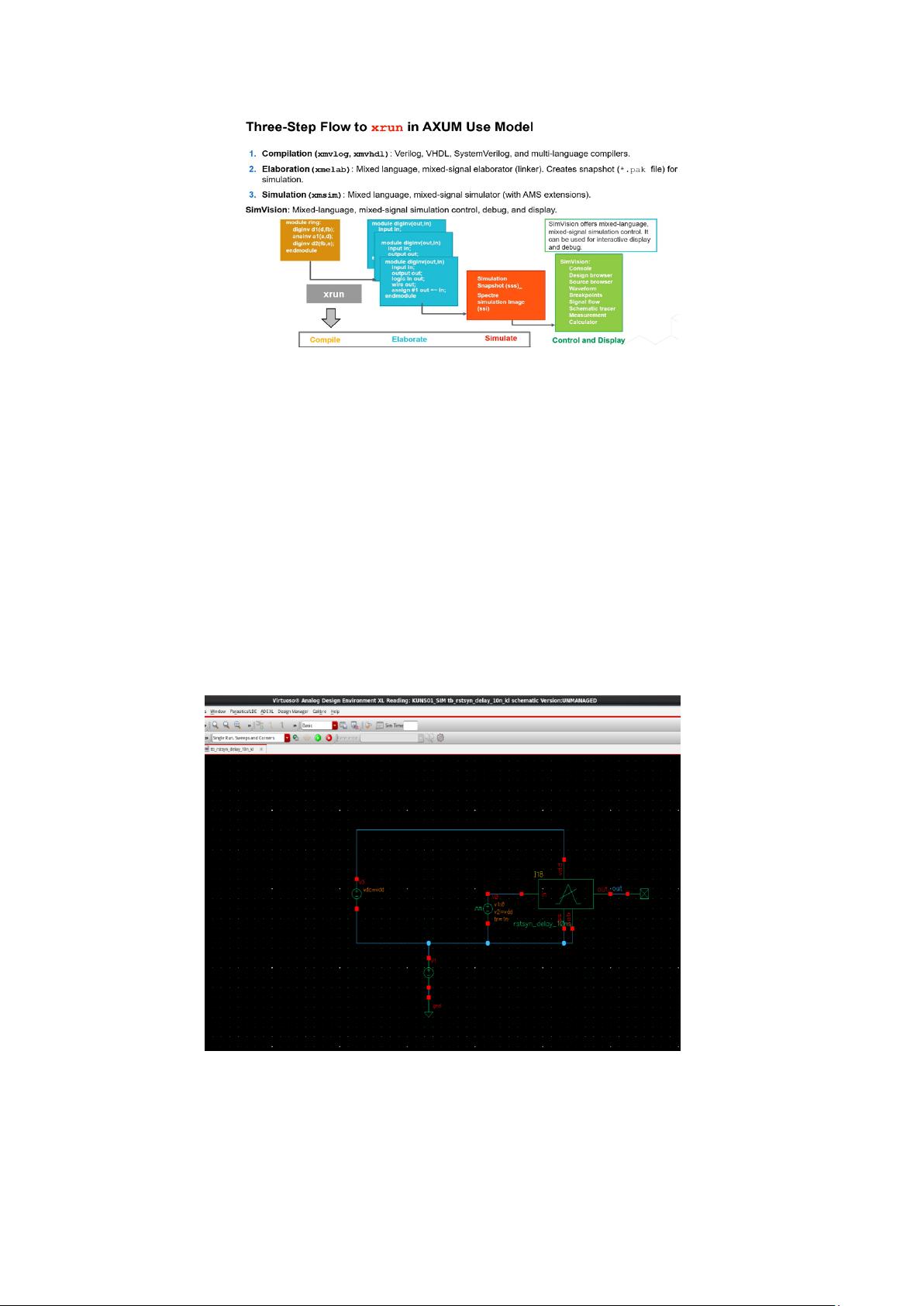

design; another usage model is AXUM(AMS Xcelium Use Model), Figure 2, it is text based flow

and almost all running in command line(except config view is generally created in virtuoso),

similar to digital design verification procedure, so quite good for digital centric(digital on top)

design including small portion of analog.

Figure 1