没有合适的资源?快使用搜索试试~ 我知道了~

计算机组成原理实验报告-八位补码加减法器的设计与实现.docx

0 下载量 173 浏览量

2022-11-30

07:50:17

上传

评论

收藏 334KB DOCX 举报

温馨提示

试读

20页

计算机组成原理实验报告-八位补码加减法器的设计与实现.docx

资源推荐

资源详情

资源评论

.

.

. .jz.

计算机科学与技术学院

计算机组成原理

实验报告书

实验 1 八位补码加/减法器的设计与实现

一、实验目的

1.掌握算术逻辑运算单元(ALU)的工作原理。

2.熟悉简单运算器的数据传送通路。

3.掌握 8 位补码加/减法运算器的设计方法。

4.掌握运算器电路的仿真测试方法

二、实验任务

实验名称

八位补码加/减法器的设计与实现

班级

学号

XX

指导教师

日期

成绩

.

.

. .jz.

1.设计一个 8 位补码加/减法运算器

(1)参考图 1,在 QUARTUS II 里输入原理图,设计一个 8 位补码加/减

法运算器。

(2)创建波形文件,对该 8 位补码加/减法运算器进行功能仿真测试。

(3)测试通过后,封装成一个芯片。

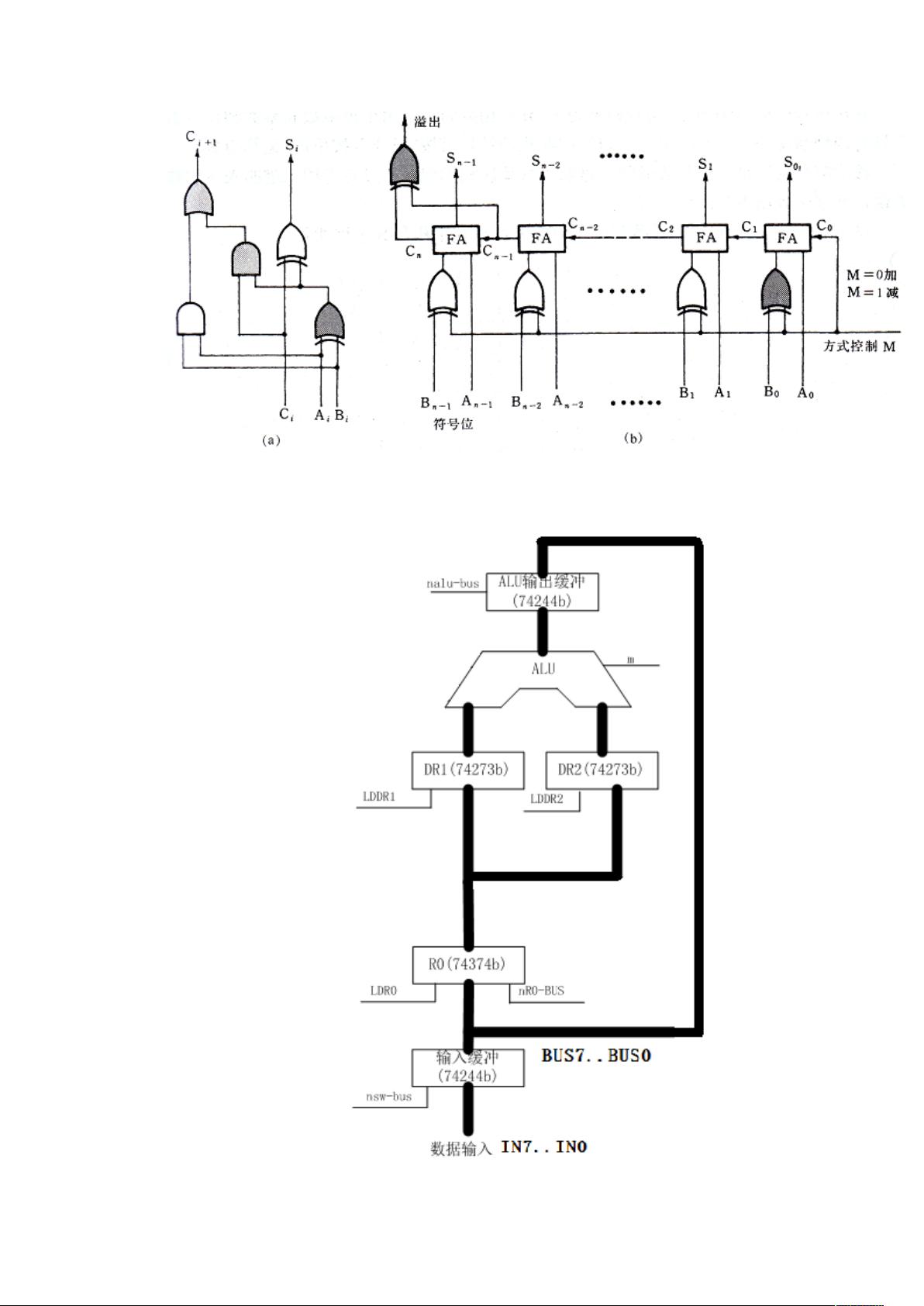

2.设计 8 位运算器通路电路

参考下图,利用实验任务 1 设计的 8 位补码加/减法运算器芯片建

立运算器通路。

3.利用仿真波形,测试数据通路的正确性。

设定各控制信号的状态,完成下列操作,要求记录各控制信号的值及

时序关系。

(1)在输入数据 IN7~IN0 上输入数据后,开启输入缓冲三态门,检查总线

BUS7~BUS0 上的值与 IN0~IN7 端输入的数据是否一致。

(2)给 DR1 存入 55H,检查数据是否存入,请说明检查方法。

(3)给 DR2 存入 AAH,检查数据是否存入,请说明检查方法。

(4)完成加法运算,求 55H+AAH,检查运算结果是否正确,请说明检查方

法。

(5)完成减法运算,分别求 55H-AAH 和 AAH-55H,检查运算结果是否正确,

请说明检查方法。

(6)求 12H+34H-56H,将结果存入寄存器 R0,检查运算结果是否正确,

同时检查数据是否存入,请说明检查方法。

三、实验要求

(1) 做好实验预习,掌握运算器的数据传送通路和 ALU 的功能特性。

(2) 实验完毕,写出实验报告,内容如下:

① 实验目的。

② 实验电路图。

③ 按实验任务 3 的要求,填写下表,以记录各控制信号的值及时序关系。

表中的序号表示各控制信号之间的时序关系。要求一个控制任务填一 X 表,

并

可用文字对有关内容进行说明。

序

nsw

-bu

nR0-

BUS

LD

R0

LD

R1

LD

R2

m

nal

u-b

IN7~

IN0

BUS7~

BUS0

.

.

. .jz.

号

s

us

④仿真波形及仿真结果的分析方法、分析过程和分析结果。

⑤实验体会与小结。

四、实验预习内容

1.实验电路设计原理及思路说明

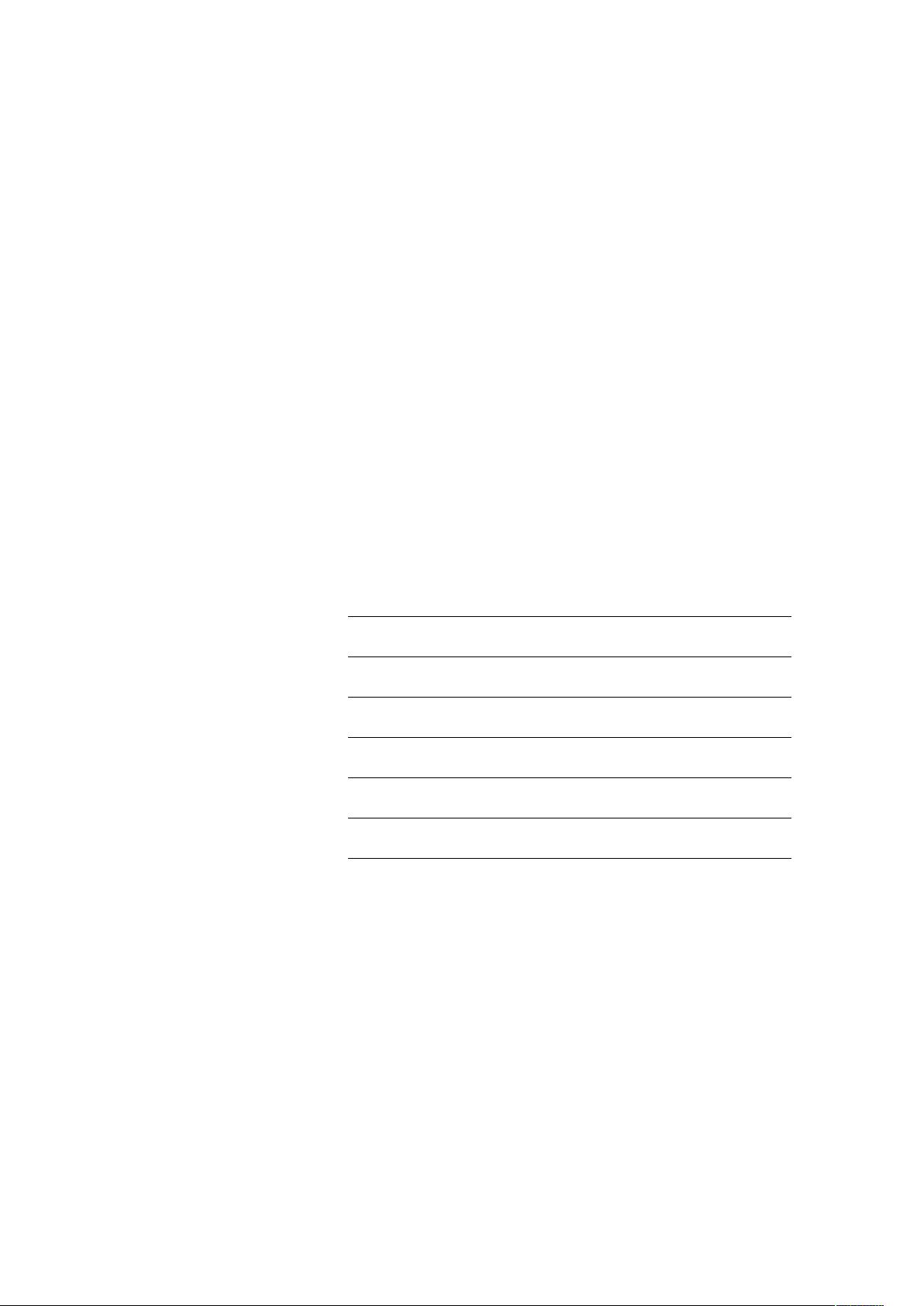

本实验利用基本逻辑门电路设计一位全加器(FA),如表 1:

表 1-一位全加器(FA)电路的输入输出信号说明

信号名称

说明

Ai

加数

Bi

加数

输入信号

Ci

低位输入的进位

Si

和

输出信号

Cj

运算产生的进位

然后以此基础上实现八位补码加/减法器的设计,考虑到实现所需既可以实现

加法又可以实现减法,所以使用了一个 M 输入来进行方式控制加减。

2. 实验电路原理图

实验参考电路如下图所示,下图(a)是 1 位全加器的电路原理图,图(b)

是由 1 位全加器采用行波进位方法设计的多位补码加/减法运算器。

.

.

. .jz.

图 1-多位补码加/减法运算器原理图

剩余19页未读,继续阅读

资源评论

黑色的迷迭香

- 粉丝: 705

- 资源: 4万+

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功