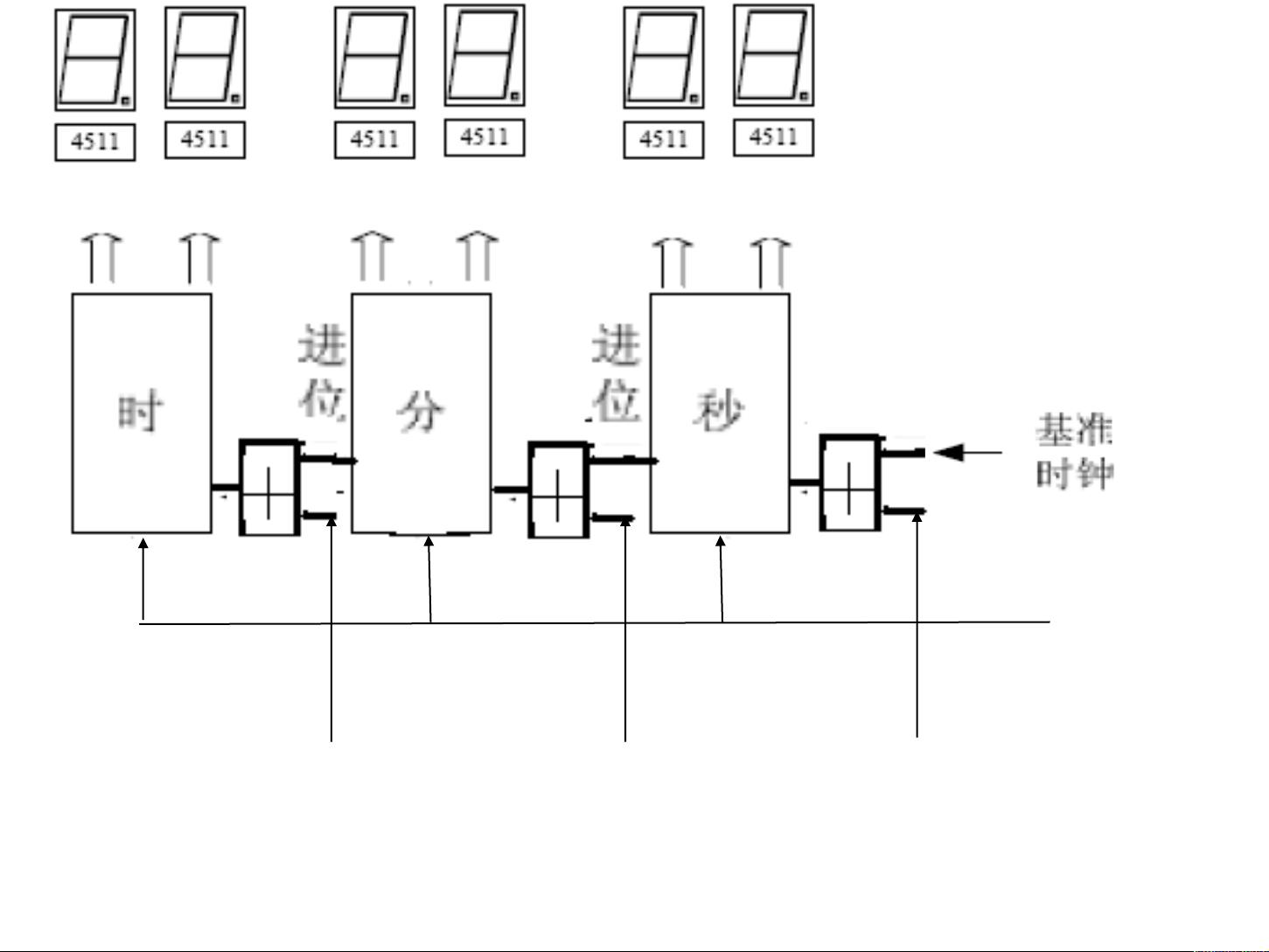

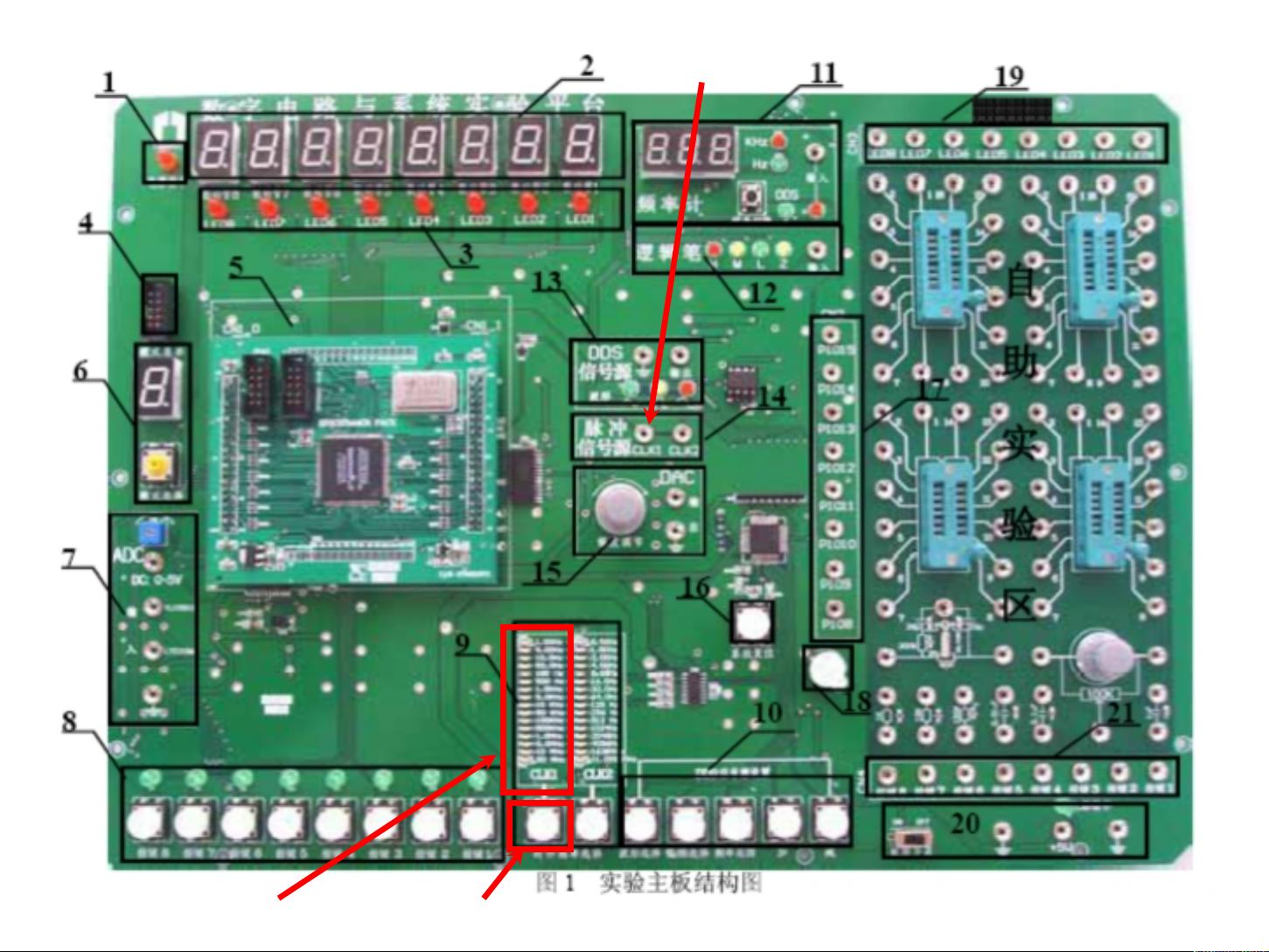

本文将深入探讨可编程逻辑器件(PLD),特别是其在多功能数字钟设计中的应用以及PLD的基础结构、类型和编程技术。在实验十一中,我们将设计一个具备计数显示、清零和校时功能的多功能数字钟。这个数字钟采用二位数码管显示,分、秒以60进制,时以24进制表示,并通过不同的按键进行校准和复位。 让我们了解PLD的基本结构。PLD分为两种主要结构:“与-或”阵列结构和查找表结构。在“与-或”阵列结构中,输入电路与“与阵列”和“或阵列”相结合,通过编程连接或断开线路来实现所需的逻辑功能。例如,全加器的逻辑映象图可以直观地展示这种结构。输出电路可以是直接输出、三态输出或寄存输出,根据设计需求选择合适的输出方式。 接着,查找表结构利用RAM存储器存储逻辑函数的真值表,通过逻辑输入地址获取逻辑输出。这种方法允许通过存储逻辑的存储单元来实现逻辑运算,如模6同步计数器和十进制异步计数器的设计。 在编程技术方面,PLD可分为一次性编程和可多次编程。一次性编程器件如熔丝编程和反熔丝编程,一旦编程后无法更改。而可多次编程器件,如浮栅编程技术(包括EPROM、EEPROM和Flash Memory),则可以在断电后保持数据且可多次修改。此外,在系统编程(ISP)和JTAG编程技术使得在不使用外部编程器的情况下,可以直接对已安装在电路板上的器件进行编程。 PLD的种类繁多,简单可编程逻辑器件(SPLD)如PAL和GAL是早期的代表。PAL器件由与-或阵列构成,但因逻辑规模小,一次性编程限制了其应用。后来的GAL器件引入了“与-输出逻辑宏单元”结构,扩展了其灵活性。 在多功能数字钟的设计中,我们利用这些基础概念,通过PLD实现计数器、译码器和控制逻辑,以达到所需的功能。计时器部分通过模10计数器和模60计数器组合实现,校时和复位功能则通过特定的按键信号触发。整个设计过程中,HDL语言仿真对于验证设计的正确性至关重要。 可编程逻辑器件在现代电子系统设计中扮演着重要角色,它们的灵活性和可编程性使得复杂的数字逻辑功能得以高效实现。从简单的计时器到复杂的系统,PLD都是工程师的得力工具。通过理解其基本结构和编程技术,我们可以更好地设计和实现各种数字系统。

剩余38页未读,继续阅读

- 粉丝: 773

- 资源: 4万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功