计算机组成教学课件:Chapter6-PipeliningPPT文档.pptx

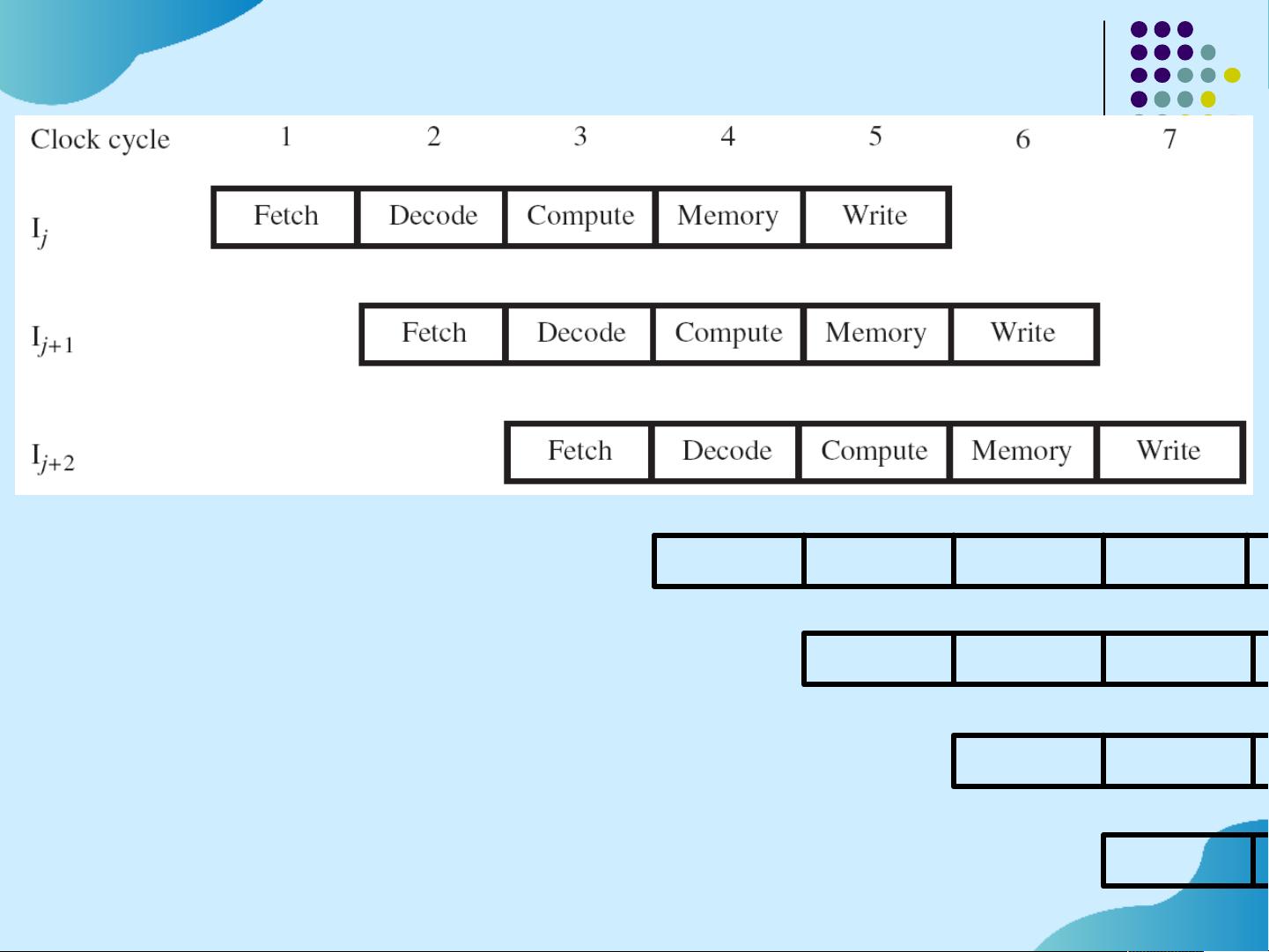

Chapter 6 - Pipelining Pipelining是计算机体系结构中的一个重要概念,它通过将处理器的数据路径分解为多个阶段,使计算机能够在同一时间执行多个操作,从而提高指令执行的效率和速度。这一技术受到了电路技术和硬件安排的影响,更快的电路对于所有计算机单元的性能提升都是有益的。 6.1 基本的Pipelining概念 Pipelining类似于工业生产流水线,其中产品在执行特定任务的工作站间移动。在计算机中,这个概念应用于指令执行的流水线化。传统上,计算机在一个时钟周期内只能执行一个指令的一个阶段,例如:取指、解码、计算、访问内存和写回结果。而通过pipelining,多个阶段可以同时对不同的指令进行操作,使得每个指令的执行时间仍然是五个时钟周期,但每秒可以执行的指令数量却提高了,达到每周期一条指令。 6.2 Pipeline组织 在pipelining中,使用程序计数器(PC)来获取指令,并确保每个时钟周期都有新的指令进入流水线。在指令流经不同阶段的过程中,需要携带与指令相关的特定信息。为了保持这些信息,使用了级间缓冲区,它们包含了寄存器RA、RB、RM、RY、RZ、IR和PC-Temp等从第5章中继承过来的寄存器。此外,这些缓冲区还用于存储控制信号设置,以协调各个阶段的操作。 6.3 Pipeline问题 尽管pipelining能显著提高处理速度,但也带来了一些挑战。其中一个主要问题是数据依赖性。如果两个连续的指令Ij和Ij+1之间存在数据依赖关系,即Ij的结果需要写入Ij+1的源寄存器,那么在pipelining中,Ij+1可能会在Ij的结果写回之前就使用了旧的寄存器值,导致计算错误。为了解决这个问题,必须暂停(延迟)Ij+1的执行,等待Ij完成并更新寄存器值。这种暂停被称为“管道冲突”或“管道阻塞”。 6.4 数据依赖 数据依赖是指指令之间因共享数据而导致的执行顺序要求。在pipelining中,这种依赖可能导致指令执行的延迟,因为某些指令必须等待其依赖的前驱指令完成才能继续执行。例如,写后读依赖(Write-after-Read,WAR)和读后写依赖(Read-after-Write,RAW)是最常见的数据依赖类型,需要通过插入额外的时钟周期(称为“等待周期”)来解决。 6.5 内存延迟 访问内存通常比在寄存器之间操作数据慢得多,这会导致内存操作成为pipelining中的瓶颈。为了解决这个问题,设计者可能采用多种策略,如预取(prefetching)、写回缓冲(write-back buffer)或者增加内存层次结构(如缓存),以减少内存访问对整体性能的影响。 6.6 分支延迟 分支指令会改变程序执行的顺序,因此需要在确定分支目标后才能正确地进行后续指令的调度。分支延迟涉及到预测分支(branch prediction)和分支目标缓冲(branch target buffer)等技术,以减少因分支决策而引起的等待时间。 6.7 资源限制 在pipelining中,当多个指令同时尝试使用同一资源时,可能会出现资源竞争。比如,多个指令同时需要同一个ALU或浮点运算单元。解决方法包括资源复制、多路复用或动态调度。 6.9 超标量操作 超标量(Superscalar)技术是在pipelining的基础上进一步优化,通过包含多个独立的执行单元,允许在同一时钟周期内执行多条指令。这可以进一步提高处理器的吞吐量,但也会增加设计复杂性和功耗。 总结来说,Pipelining是提高计算机性能的关键技术之一,通过将指令执行划分为多个阶段并行处理,能够在保持总执行时间不变的同时增加指令吞吐率。然而,它也引入了一系列挑战,如数据依赖、内存延迟和资源限制,需要通过巧妙的设计和策略来解决。

剩余49页未读,继续阅读

- 粉丝: 778

- 资源: 7万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功