数电实验-多功能数字钟.docx

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

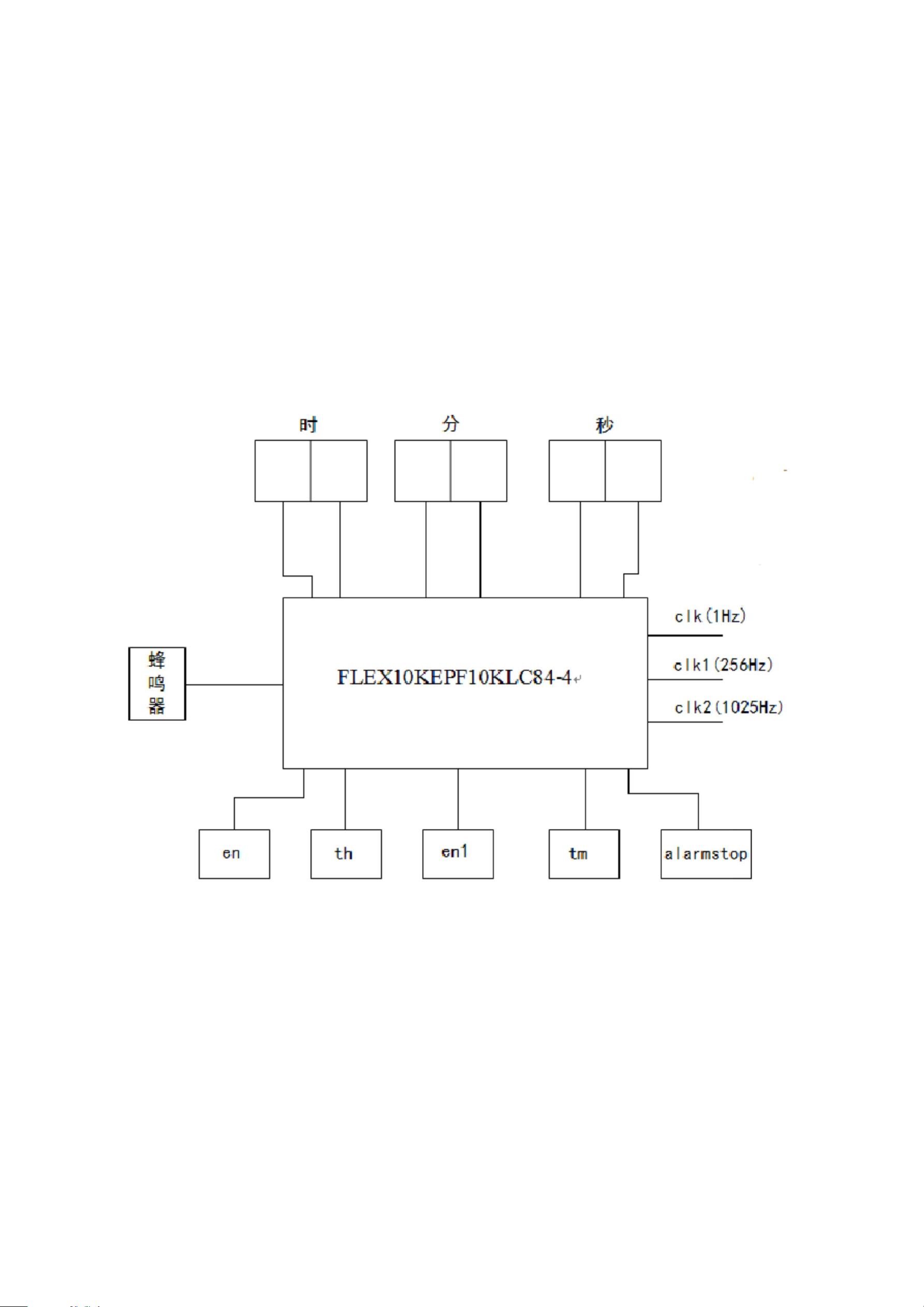

本文将详细介绍一个基于数字电路的多功能数字钟设计,该设计是大连理工大学电子信息与电气工程学部自动化专业的一次实验项目。实验的目标是创建一个能够显示小时、分钟和秒钟的计时器,支持手动校时、设定闹钟以及整点报时功能。设计中采用了模24和模60计数器来实现24小时计时,同时确保在调整闹钟设置时不会影响数字钟的正常运行。 设计要求如下: 1. 实现一个可以显示00到23小时的十进制数字时钟。 2. 提供手动校正时间(小时和分钟)的功能。 3. 设定定时与闹钟功能,能在预设时间发出闹铃声,并在整点进行报时。从59分54秒开始,每隔2秒发出低音,连续3次,整点报时为高音。 系统分析与方案设计: 系统总体设计采用模24计数器来处理小时,模60计数器处理分钟和秒钟。为了在调节闹钟时不干扰正常计时,需要独立的控制逻辑。系统硬件电路设计应包括按键接口、LED或数码管显示、蜂鸣器以及相关的时钟信号。实验中,由于未涉及FPGA芯片的使用,这部分可以通过FPGA最小系统模块框来代替,其他接口部分需要设计电路和参数。 VHDL设计是实现这一系统的软件部分,它描述了系统的各个组成部分。例如,秒计数器(模60计数器)和分计数器(同样为模60计数器)的VHDL代码展示了如何使用进程(process)来实现计数逻辑。在秒计数器中,当秒钟达到59时,会触发进位信号,并重置个位计数器。分计数器类似,但还添加了一个手动校时的控制输入(en),以便在en=1时进行时间调整。 系统结构描述: - 顶层文件(system)包含所有子模块,如模24计数器、模60计数器、手动校时逻辑、闹钟设定和报时控制器。 - 子程序(modules)包括计数器、译码器、驱动数码管的电路以及控制逻辑,每个都有明确的功能描述。 - 秒计数器负责处理秒钟的递增和进位信号。 - 分计数器除了递增和进位外,还包含手动校时功能。 - 闹钟和整点报时逻辑则根据特定频率的时钟信号触发蜂鸣器发出声音。 系统原理图和各模块的符号说明有助于理解整个设计的结构和工作方式。通过VHDL语言实现的计数器,可以通过仿真图验证其正确性,确保在不同状态下的行为符合预期。 总结,这个多功能数字钟的设计结合了数字电路的基础知识,如模计数器和状态机,以及VHDL编程技术,实现了计时、校时、闹钟和报时等功能。这一实验项目不仅锻炼了学生的实践操作能力,也加深了他们对数字系统设计的理解。

剩余17页未读,继续阅读

xiaomin08212023-01-03资源是宝藏资源,实用也是真的实用,感谢大佬分享~

xiaomin08212023-01-03资源是宝藏资源,实用也是真的实用,感谢大佬分享~

- 粉丝: 1w+

- 资源: 5万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功