Cirrus Logic Confidential

Copyright 2017–2020 Cirrus Logic, Inc. and Cirrus Logic

International Semiconductor Ltd. All Rights Reserved.

http://www.cirrus.com

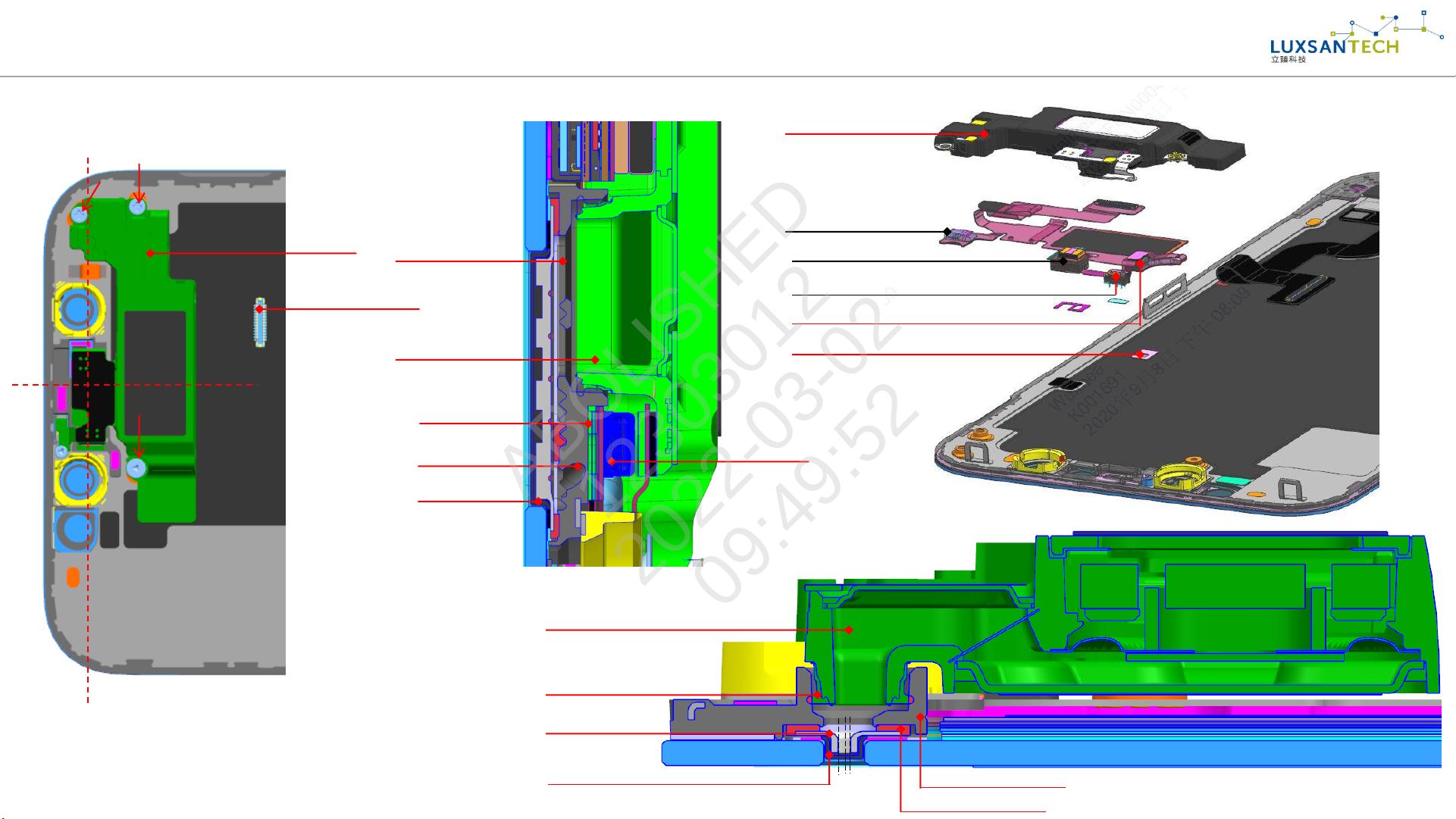

Multi-Channel Audio Codec with ANC, SoundWire, and TIA

Multiple Analog Inputs and ADCs

• Four Type A high-performance paths

— 120 dB dynamic range (A-weighted)

— –90 dB THD+N @ –1 dBFS (differential)

• Two Type B paths with –6 to +18 dB PGA and 96 dB

dynamic range (A-weighted)

• Four Type C paths with –6 to +18 dB PGA and 91 dB

dynamic range (A-weighted)

• Two Type D paths with –6 or 0 dB PGA and 77 dB

dynamic range (MIN, 10 Hz to 40kHz bandwidth)

Active Noise Cancelation (ANC) Block

• ANC algorithm

— Fully-adaptive digital feedforward (plus optional

feedback) architecture with ultralow-latency antinoise

paths

— Programmable detectors (clip, noise, etc.)

— Ability for host software to monitor and override

adaptation

— Hardware accelerators: FIR, FFT, LMS, dB

conversion, and random number generator

• Supports customer low-power (CLP) algorithms and

programmable DSP (digital signal processor) operations

Transimpedance Amplifier

• Excitation output driven from internal DAC

• Selectable transimpedance gains from 1.5 kΩ to 15 kΩ

• 40 kHz passband (±0.25 dB flatness)

Two SoundWire

®

Master Interfaces

•MIPI

®

SoundWire

®

Version 1.1 compliant

• Supports PDM, PCM, and bulk data transport

• Multi-lane capability on SWIRE1 port

Multiple Serial Ports

• Four audio serial ports (ASP)

— Up to 16 I/O time-division multiplex (TDM) channels

— Master or slave mode operation

— Fs = 16, 24, 32, 48, and 96 kHz

• Two PDM digital outputs for connection to external DAC/

amplifiers, such as the CS35L27

— PDM clock supports master or slave operation

— Supports 3 and 6 MHz PDM clock frequency

(Features continued on page 2)

ASP2

(TDM)

ASP3

(TDM)

SPI Port

RCO

AIN1±

JTAG Debug

Controller

GPIO[5:1] / JTAG

VDD_P

16

16

Register

Space

Audio

Serial Port 3

16

16

MCLK1_IN

MCLK

INT

MCLK_OUT

Bulk / Control

Data Bus

ADC A1

ADC

–

+

Digital Routing and Processing

VDD_1P8VDD_D

VDD_A

Analog

Core

MCLK2_IN

PCM Bus

1-bit PDM Crossbar

ASP1

(TDM)

16

16

Audio

Serial Port 2

Audio

Serial Port 1

± Amplifier

Output

AOUT

DAC

VDD_P

AIN2±

ADC A2

ADC

–

+

A2 Decimator and

HPF

AIN3±

AIN4±

ADC B2

ADC

–

+

B2 Decimator and

HPF

AIN6A±

AIN6B±

C1 Decimat or and

HPF

MIC1_BIAS

MIC2_BIAS

MIC3_BIAS

MIC4_BIAS

MIC5_BIAS

MIC6_BIAS

Level Shifters

SoundWire

Master 1

SWIRE1

CLK[2:0]/DATA[2:0]

SoundWire

Master 2

ASP3_BCLK

6

18

6

Mic Bias 1

LP Mic Bias 1

Mic Bias 2

LP Mic Bias 2

Mic Bias 3

LP Mic Bias 3

Mic Bias 4

LP Mic Bias 4

Mic Bias 5

Mic Bias 6

ASP4_BCLK

PDMOUT 1/2

CLK / DATA

Level Shifters

4

8

Diagnostic

Generator

VIO_SWIRE

1

4

2

3

4

8

16

Multibit PDM

Crossbar

2

2

A1 Decimator and

HPF

ADC A3

ADC

–

+

ADC A4

ADC

–

+

A4 Decimator and

HPF

A3 Decimator and

HPF

AIN5A±

ADC B1

ADC

–

+

B1 Decimator and

HPF

AIN5B±

SWIRE2

CLK[1:0]/DATA0

PDM

Outputs

MikeyBus

Core and

Transceiver

MikeyBus

DP/DN

10 10

Level Shifters

VIO_PDM

VDD_P

VDD_1P8

From Interpolator 1

4

4

PDM

Output

PDM

Input

Baseband

Output

Debug

Output

Baseband

Input

Active Noise

Cancelation

(ANC) Algorithm

Digital Signal Processor (DSP)

Customer Low-

Power (CLP)

Algorithm

PCM

Input

PCM

Output

1

To AOUT

MUX

CLP_EN

Voice, Playback,

and Sidetone

Bypass Inputs

ADC C2

ADC

–

+

AIN8±

AIN7±

ADC C1

ADC

–

+

C2 Decimat or and

HPF

C3 Decimat or and

HPF

ADC C4

ADC

–

+

AIN10±

AIN9±

ADC C3

ADC

–

+

C4 Decimat or and

HPF

D1 Decimat or and

HPF

AIN12±

AIN11±

D2 Decimat or and

HPF

1

ASP4

(TDM)

Audio

Serial Port 4

16

16

ASP1_BCLK

ASP2_BCLK

I2C Port

12

3

DSP

16

TIA_EXOUT

VDD_P

1

–

+

–

+

TIA_SENSE

VDD_P

PDM

Remodulator

(x4)

PDM

Remodulator

(x4)

Interpolator

(x4)

Interpolator

(x4)

4

4

EX

DAC

From ANC PDM Ouput

AOUT M UX

To AOUT

MUX

RESET

INT

VIO_ASP

VIO_GPIO

VIO_SPI

Level

Shifters

VIO_I2C

I2C_ADDR

Level

Shifters

Level

Shifters

Level

Shifters

VIO_MCLK

DSP

WAKE

ADC D1

ADC

–

+

ADC D2

ADC

–

+

4

4

3

TIA_OUT

VDD_A

VIO_GPIO

MICBIAS_DIS

DS1208F3

OCT 2020

CS42L77

DS1208F3 Cirrus Logic Confidential 2

Copyright 2017–2020 Cirrus Logic, Inc. and Cirrus Logic International Semiconductor Ltd.

CS42L77

Analog Output

• Fully-differential audio amplifier output

• –80 dB THD+N (–1 dBFS)

• 457 mW output into 13 Ω load, VDD_P = 5.25 V and

VDD_A = 1.94 V

• Selectable analog and digital output gain settings with

mute

• Can drive high-impedance, line-level differential inputs

MikeyBus Digital Bus Interface

• MikeyBus 1.1 compliant host controller operation

• Bidirectional transfer of audio data and bulk data

• Up to 10-downlink and 10-uplink traffic channels

• Supports MikeyBus Wake detection

System Features

• Native (no PLL required) support for 12 or 12.288 MHz

MCLK input

— May be sourced from MCLK input or ASP BCLK input

with a MCLK output

— Built-in RCO and PLL

• Integrated power management to reduce system power

consumption

— Individual power saving controls for ADCs, mic bias

generators, serial ports, DAC, output amplifier,

SoundWire ports, DSP, TIA, and MikeyBus

— Power-on reset for analog battery supply and digital

supplies (VDD_P, VDD_1P8, and VDD_D)

— Five power domains to reduce leakage and power

— All interface logic blocks support independent 1.2 or

1.8 V operation

• Flexible digital audio mixing and routing

• Assignable Type-A and Type-B decimators

• Assignable interpolators

• Assignable PDM remodulators

• Assignable crossfaders

• Assignable stereo three-band parametric EQ

• Assignable mixers

• Assignable internal diagnostic signal generator

• Flexible control port supports SPI™ input, I

2

C slave input, or

control from the internal DSP

• Bulk data transport between SPI port and MikeyBus or

SoundWire ports

• Five multifunction GPIO interfaces to the DSP incorporating

a JTAG debug port

• CLP_EN interface to control power functions.

• Interrupt output

DS1208F3 Cirrus Logic Confidential 3

Copyright 2017–2020 Cirrus Logic, Inc. and Cirrus Logic International Semiconductor Ltd.

CS42L77

General Description

The CS42L77 is an audio codec for portable applications. Four controllable power domains and two low-power record

modes can be utilized to reduce power consumption.

It features two SoundWire master interfaces, four audio serial

ports (ASP), 12 ADCs, a transimpedance amplifier system, two PDM outputs, a differential analog output, and a

MikeyBus host controller. The

CS42L77 uses a reference clock frequency of 12 or 12.288 MHz.

The CS42L77 incorporates a DSP for ANC and Customer Low-Power (CLP) processing that incorporates a free-running

PLL for use in the CLP mode. The CLP mode is capable of 16-channel PCM processing. Four ASPs and two SoundWire

master ports are provided to accommodate multiple digital audio sources and destinations.

The integrated MikeyBus host controller allows MikeyBus control and communication and is compliant with the MikeyBus

Version 1.1 Specification. The integrated MikeyBus host controller allows up to ten channels of uplink and ten channels of

downlink traffic data, as well as uplink and downlink bulk data routing and buffering. MikeyBus wake functionality is also

incorporated. The CS42L77 SPI-to-MikeyBus data throughput is optimized to allow the maximum allowed MikeyBus bulk

data bandwidth.

Line or mic inputs are provided to twelve ADC paths. Type-A consists of four high-performance paths, offering high

dynamic-range operation. Type-B consists of two mid-performance paths with analog gain, optimized for small area.

Type-C consists of four mid-performance paths with analog gain optimized for power consumption. Type-D consists of the

two DC-to-40 kHz paths with analog gain. Six low-noise mic bias voltage supplies are also provided, four of which can be

used for low power operation.

All ADC input paths can be routed directly to a decimator and selectively high-pass filtered (HPF) before routing to the

PCM bus. Additionally, Type-A and Type-B ADCs can also be routed directly to the PDM bus.

An internal PCM bus and PDM audio crossbars are used to route the CS42L77’s inputs (ADCs, SoundWire, MikeyBus,

and/or ASPs) to the outputs (ASPs, SoundWire, MikeyBus, PDM outputs, and/or a differential analog output). Four digital

mixers allow mixing of PCM signals. Additionally, four cross-faders are integrated, allowing smooth transitions between

sources.

External devices with PDM inputs can be driven through the two digital PDM output interfaces. The PDM ports support

both master and slave clock configurations.

A differential-drive audio amplifier, powered from the battery supply, is available for driving the handset receiver, linear

vibrator, etc. A transimpedance amplifier system consists of a DAC and excitation amplifier output and a sense input with

digitally selectable transimpedance gains from 1.5 kΩ to 15 kΩ. The excitation output and the transimpedance amplifier

output route to the Type-D ADCs.

A stereo equalizer is connected directly to the internal PCM audio bus. The two inputs to each equalizer enter three fully

programmable parametric filter banks. Each bank can be independently configured in any of the following topologies:

low-pass filter (LPF), high-pass filter (HPF), all-pass filter (APF), band-pass filter (BPF), notch filter (NF), peaking EQ

(PEQ), low-shelving EQ (LSEQ), or high-shelving EQ (HSEQ).

Acoustic noise is captured through the AIN or SoundWire inputs then passed to the digital ANC filters and adaptive engine

providing adaptive feed-forward noise cancelation. Additionally, the DSP can also be programmed for user-defined

functions via the CLP interface.

The CS42L77 is available in a commercial-grade 144-ball WLCSP package with 0.4 mm pitch, operating from –40°C

to +85°C.

DS1208F3 Cirrus Logic Confidential 4

Copyright 2017–2020 Cirrus Logic, Inc. and Cirrus Logic International Semiconductor Ltd.

CS42L77

Table of Contents

1 Pin Assignments and Descriptions .................................................................................................................................................. 7

1.1 Package Drawing (Top View, Through Package) ...................................................................................................................... 7

1.2 Pin Descriptions .........................................................................................................................................................................8

1.3 Termination of Unused Pins ..................................................................................................................................................... 11

1.4 Electrostatic Discharge (ESD) Protection Circuitry .................................................................................................................. 12

2 Typical Connection Diagrams ......................................................................................................................................................... 13

2.1 Electromagnetic Compatibility (EMC) Circuitry ........................................................................................................................ 14

2.2 Ceramic Capacitor Derating ..................................................................................................................................................... 14

3 Characteristics and Specifications ................................................................................................................................................ 15

Table 3-1. Parameter Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 3-2. Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 3-3. Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 3-4. Output Fault Rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 3-5. Combined Type-A ADC On-Chip Analog and Digital Filter Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 3-6. Combined Type-B ADC On-Chip Analog and Digital Filter Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 3-7. Combined Type-C ADC On-Chip Analog and Digital Filter Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 3-8. Combined Type-D ADC On-Chip Analog and Digital Filter Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 3-9. Combined ASP, Interpolator, AOUT DAC Digital and AOUT Filter Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 3-10. Combined ASP, Interpolator, Excitation DAC, and TIA_EXOUT Filter Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 3-11. Combined ASP, Interpolator, Remodulator, and PDMOUT Filter Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 3-12. Type-A ADC AINx-to-Serial Data Out Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 3-13. Type-B ADC AINx-to-Serial Data Out Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 3-14. Type-C ADC AINx-to-Serial Data Out Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 3-15. Type-D ADC AINx-to-Serial Data Out Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 3-16. ADCx Input Impedance Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 3-17. ASPx_DIN-to-AOUT Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 3-18. ASPx_DIN-to-TIA_EXOUT Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Table 3-19. TIA_SENSE and TIA_OUT Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 3-20. MICx_BIAS Characteristics, High-Performance Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 3-21. MICx_BIAS Characteristics, Low-Power Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 3-22. DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 3-23. Power-Supply Rejection Ratio (PSRR) Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 3-24. Power Consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 3-25. DSP Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 3-26. Master Clock (MCLK) Input Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 3-27. RCO-to-MCLK_OUT Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 3-28. PDM Output Interface Specifications—Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 3-29. PDM Output Interface Specifications—Slave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 3-30. Audio Serial Port Interface Characteristics—Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 3-31. Audio Serial Port Interface Characteristics—Slave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 3-32. SPI Control Port Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 3-33. I²C Control Port Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 3-34. JTAG Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 3-35. SoundWire Port Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 3-36. MikeyBus DP/DN Digital Interface Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 3-37. MikeyBus DP/DN Timing Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 3-38. Digital Interface Specifications and Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

4 Functional Description .................................................................................................................................................................... 50

4.1 Overview .................................................................................................................................................................................. 50

4.2 Resets ..................................................................................................................................................................................

.... 53

4.3 Power Supply Considerations .................................................................................................................................................. 53

4.4 Clocking Architecture ............................................................................................................................................................... 56

4.5 Interrupts .................................................................................................................................................................................. 64

4.6 Analog Inputs ........................................................................................................................................................................... 68

4.7 Internal Audio Routing .............................................................................................................................................................. 78

4.8 Digital Mixer ............................................................................................................................................................................. 86

4.9 Crossfader ................................................................................................................................................................................ 87

4.10 Three-Band Equalizer ............................................................................................................................................................ 88

4.11 Decimators ............................................................................................................................................................................. 91

4.12 Interpolators ...........................................................................................................................................................................91

4.13 Diagnostic Generator ............................................................................................................................................................. 92

4.14 Speaker DAC ......................................................................................................................................................................... 93

4.15 TIA Subsystem ....................................................................................................................................................................... 95

4.16 PDM Output Interface ............................................................................................................................................................ 97

4.17 SoundWire

Interface ............................................................................................................................................................. 100

4.18 Audio Serial Ports ................................................................................................................................................................ 136

4.19 MikeyBus Host Interface Overview ...................................................................................................................................... 146

4.20 SPI Control Port ................................................................................................................................................................... 161

4.21 I²C Control Port Interface ..................................................................................................................................................... 169

4.22 ANC Block ............................................................................................................................................................................ 173

DS1208F3 Cirrus Logic Confidential 5

Copyright 2017–2020 Cirrus Logic, Inc. and Cirrus Logic International Semiconductor Ltd.

CS42L77

5 System Applications ...................................................................................................................................................................... 199

5.1 Device Initialization ................................................................................................................................................................ 199

6 Register Quick Reference ............................................................................................................................................................. 200

6.1 Device Routing (CHIP) ........................................................................................................................................................... 201

6.2 Global, Power, and Clock Gating (GLOBAL) ......................................................................................................................... 202

6.3 Clocking (CCM) ...................................................................................................................................................................... 203

6.4 PLL (PLL) ............................................................................................................................................................................... 205

6.5 Interrupt Controller (INTC) ..................................................................................................................................................... 205

6.6 Pad Interface (PADIF) ............................................................................................................................................................ 211

6.7 ASP 1 RX/TX (ASP1) ............................................................................................................................................................. 212

6.8 ADC Type C (ADC_C) ........................................................................................................................................................... 216

6.9 Mic Bias Control (MICBIAS) ................................................................................................................................................... 216

6.10 OTP (OTP) ........................................................................................................................................................................... 217

6.11 Mixer Control (MIXER) ......................................................................................................................................................... 217

6.12 Stereo Equalizer (EQ) .......................................................................................................................................................... 218

6.13 Crossfader (XFADE) ............................................................................................................................................................ 218

6.14 Interpolator (INTP) ............................................................................................................................................................... 219

6.15 PCM Bus (PCM_BUS) ......................................................................................................................................................... 220

6.16 PDM Crossbar (PDM_XBAR) .............................................................................................................................................. 223

6.17 MikeyBus (MBUS) ................................................................................................................................................................ 223

6.18 SoundWire 1 DP0 (SWIRE1_DP0) ...................................................................................................................................... 229

6.19 SoundWire 1 MCP (SWIRE1_MCP) .................................................................................................................................... 230

6.20 SoundWire 1 DP1 (PCM Sink) (SWIRE1_DP1) ................................................................................................................... 231

6.21 SoundWire 1 DP2 (PCM Sink) (SWIRE1_DP2) ................................................................................................................... 232

6.22 SoundWire 1 DP3 (PCM Sink) (SWIRE1_DP3) ................................................................................................................... 233

6.23 SoundWire 1 DP4 (PCM Source) (SWIRE1_DP4) .............................................................................................................. 234

6.24 SoundWire 1 DP5 (PDM Source) (SWIRE1_DP5) .............................................................................................................. 235

6.25 SoundWire 1 DP6 (PDM Sink) (SWIRE1_DP6) ................................................................................................................... 236

6.26 SoundWire 1 Wrapper (SWIRE1) ........................................................................................................................................ 237

6.27 SoundWire 2 DP0 (SWIRE2_DP0) ...................................................................................................................................... 239

6.28 SoundWire 2 MCP (SWIRE2_MCP) .................................................................................................................................... 240

6.29 SoundWire 2 DP1 (PCM Sink) (SWIRE2_DP1) ................................................................................................................... 241

6.30 SoundWire 2 DP2 (PCM Sink) (SWIRE2_DP2) ................................................................................................................... 242

6.31 SoundWire 2 DP3 (PCM Source) (SWIRE2_DP3) .............................................................................................................. 243

6.32 SoundWire 2 Wrapper (SWIRE2) ........................................................................................................................................ 244

6.33 ASP 2 RX/TX (ASP2) ........................................................................................................................................................... 245

6.34 ASP 3 RX/TX (ASP3) ........................................................................................................................................................... 248

6.35 ASP 4 RX/TX (ASP4) ........................................................................................................................................................... 252

6.36 PDM Interface (PDMOUT) ................................................................................................................................................... 255

6.37 Speaker DAC (DAC) ............................................................................................................................................................ 255

6.38 Transimpedance Amp (TIA) ................................................................................................................................................. 255

6.39 ADC Type A (ADC_A) .......................................................................................................................................................... 256

6.40 ADC Type B (ADC_B) .......................................................................................................................................................... 256

6.41 ADC Type D (ADC_D) ......................................................................................................................................................... 256

6.42 ANC Wrapper (ANC_WRAPPER) ........................................................................................................................................ 257

7 Register Descriptions .................................................................................................................................................................... 258

7.1 Device Routing (CHIP) ........................................................................................................................................................... 258

7.2 Global, Power, and Clock Gating (GLOBAL) ......................................................................................................................... 262

7.3 Clocking (CCM) ...................................................................................................................................................................... 268

7.4 PLL (PLL) ............................................................................................................................................................................... 279

7.5 Interrupt Controller (INTC) ..................................................................................................................................................... 280

7.6 Pad Interface (PADIF) ............................................................................................................................................................ 304

7.7 ASP 1–4 RX/TX (ASPx) ......................................................................................................................................................... 310

7.8 ADC Type C (ADC_C) ........................................................................................................................................................... 326

7.9 Mic Bias Control (MICBIAS) ................................................................................................................................................... 327

7.10 OTP (OTP) ........................................................................................................................................................................... 327

7.11 Mixer Control (MIXER) ......................................................................................................................................................... 328

7.12 Stereo Equalizer (EQ) .......................................................................................................................................................... 331

7.13 Crossfader (XFADE) ............................................................................................................................................................ 333

7.14 Interpolator (INTP) ............................................................................................................................................................... 335

7.15 PCM Bus (PCM_BUS) ......................................................................................................................................................... 336

7.16 PDM Crossbar (PDM_XBAR) .............................................................................................................................................. 344

7.17 MikeyBus (MBUS) ................................................................................................................................................................ 346

7.18 SoundWire 1 DP0 (SWIRE1_DP0) ...................................................................................................................................... 363

7.19 SoundWire 1 MCP (SWIRE1_MCP) .................................................................................................................................... 365

7.20 SoundWire 1 DP1 (PCM Sink) (SWIRE1_DP1) ................................................................................................................... 374

7.21 SoundWire 1 DP2 (PCM Sink) (SWIRE1_DP2) ................................................................................................................... 377

评论0