没有合适的资源?快使用搜索试试~ 我知道了~

锁相环开发+PLL芯片+LMX2595中文数据手册

需积分: 5 8 下载量 96 浏览量

2023-12-26

15:26:30

上传

评论 2

收藏 3.82MB PDF 举报

温馨提示

试读

56页

LMX2595高性能宽带合成器可生成10MHz-20GHz范围内的任何频率。集成的倍频器用于生成 15GHz以上的频率。品质因数为-236dBc/Hz的高性能PLL和高鉴相频率可实现非常低的带内噪声和集成抖动。高速N分频器没有预分频器,从而显著减少了杂散的振幅和数量。还有一个可减轻整数边界杂散的可编程输入乘法器。 LMX2595 允许用户同步多个器件的输出,并可在输入和输出之间确定需要延迟的情况下 应用。频率斜升发生器可在自动斜坡生成选项或手动选项中最多合成2段斜坡,以实现最大的灵活性。通过快速校准算法可将频率加快至20μs以上。LMX2595增添了对生成或重复SYSREF(符合JESD204B标准)的支持,此SYSREF是高速数据转换器的理想低噪声时钟源。此配置中提供了精细的延迟调节(9ps分辨率),以解决板迹线的延迟差异。LMX2595中的输出驱动器在载波频率为15GHz时提供高达7dBm的输出功率。该器件采用单个3.3V电源供电,并具有集成的LDO,无需板载低噪声LDO。

资源推荐

资源详情

资源评论

LMX2595

具有相位同步功能和 JESD204B 支持的 LMX2595 20GHz 宽带 PLLATINUM

TM

射频合成器

1. 特性

10MHz-20GHz输出频率

在15GHz载波100KHz偏频的情况下具有-110dBc/Hz的相位噪声

7.5GHz时,具有45fs rms抖动(100Hz-100MHz)

可编程输出功率

PLL主要规格

– 品质因数:-236dBc/Hz

– 标称 1/f 噪声:-129dBc/Hz

– 最高相位检测器频率

– 400MHz 整数模式

– 300MHz 分数模式

– 32位分数N分频器

用可编程输入乘法器消除整数边界杂散

跨多个设备实现输出相位同步

支持具有9ps分辨率可编程延迟的SYSREF

用于FMCW应用的频率斜升和线性调频脉冲生成能力

小于20μs VCO 校准速度

3.3V 单电源运行

2. 应用

5G和毫米波无线基础设施、测试和测量设备、雷达、MIMO、相控阵天线和波束形成、高

速数据转换器时钟(支持JESD204B)

3. 简介

LMX2595高性能宽带合成器可生成10MHz-20GHz范围内的任何频率。集成的倍频器用于生

成 15GHz以上的频率。品质因数为-236dBc/Hz的高性能PLL

和高鉴相频率可实现非常低的带内

噪声和集成抖动。高速N分频器没有预分频器,从而显著减少了杂散的振幅和数量。还有一个

可减轻整数边界杂散的可编程输入乘法器。

LMX2595 允许用户同步多个器件的输出,并可在输入和输出之间确定需要延迟的情况下

应用。频率斜升发生器可在自动斜坡生成选项或手动选项中最多合成2段斜坡,以实现最大的灵

活性。通过快速校准算法可将频率加快至20μs以上。LMX2595增添了对生成或重复SYSREF

(符合JESD204B标准)的支持,此SYSREF是高速数据转换器的理想低噪声时钟源。此配置中

提供了精细的延迟调节(9ps分辨率),以解决板迹线的延迟差异。LMX2595中的输出驱动器

在载波频率为15GHz时提供高达7dBm的输出功率。该器件采用单个3.3V电源供电,并具有集成

的LDO,无需板载低噪声LDO。

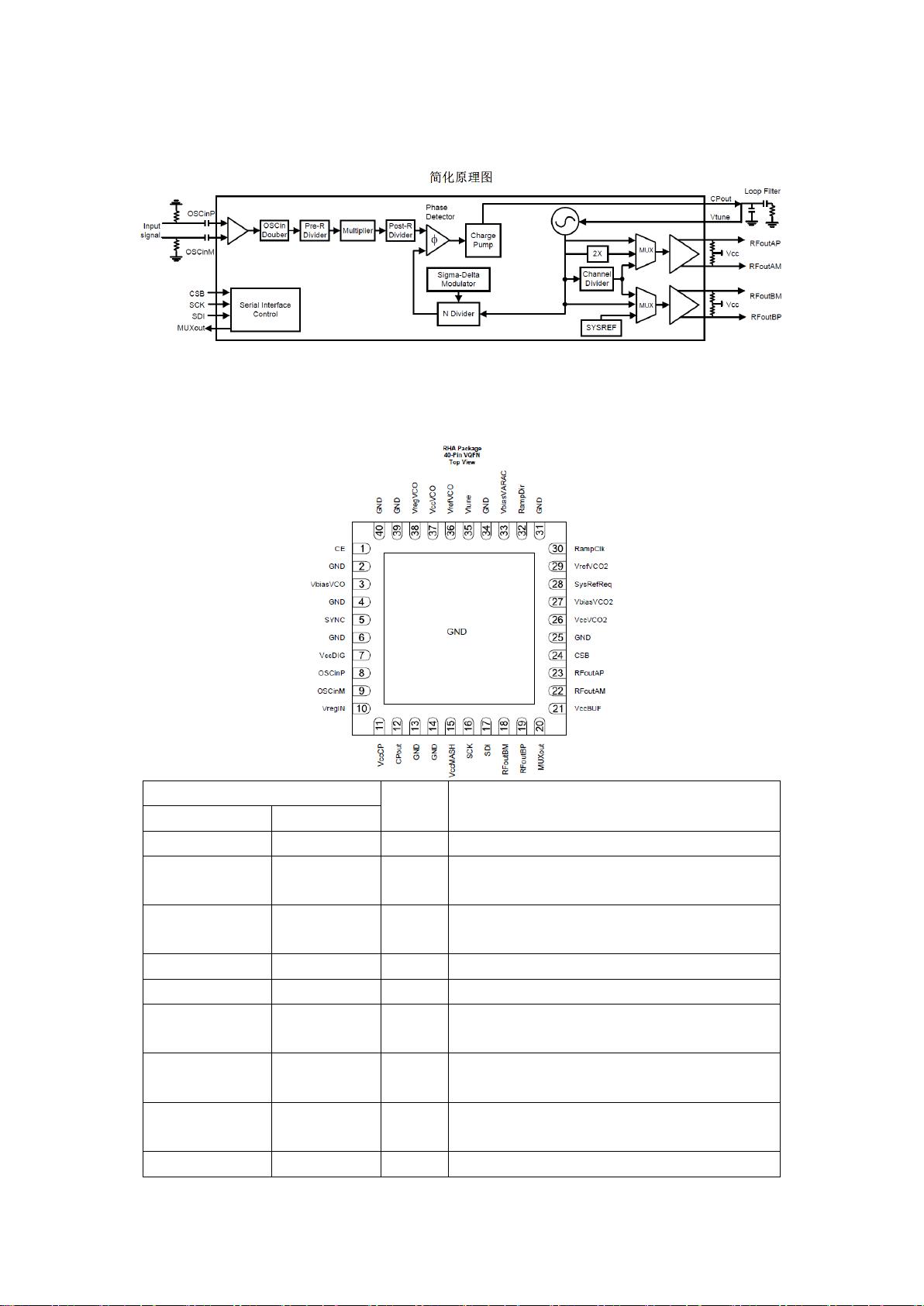

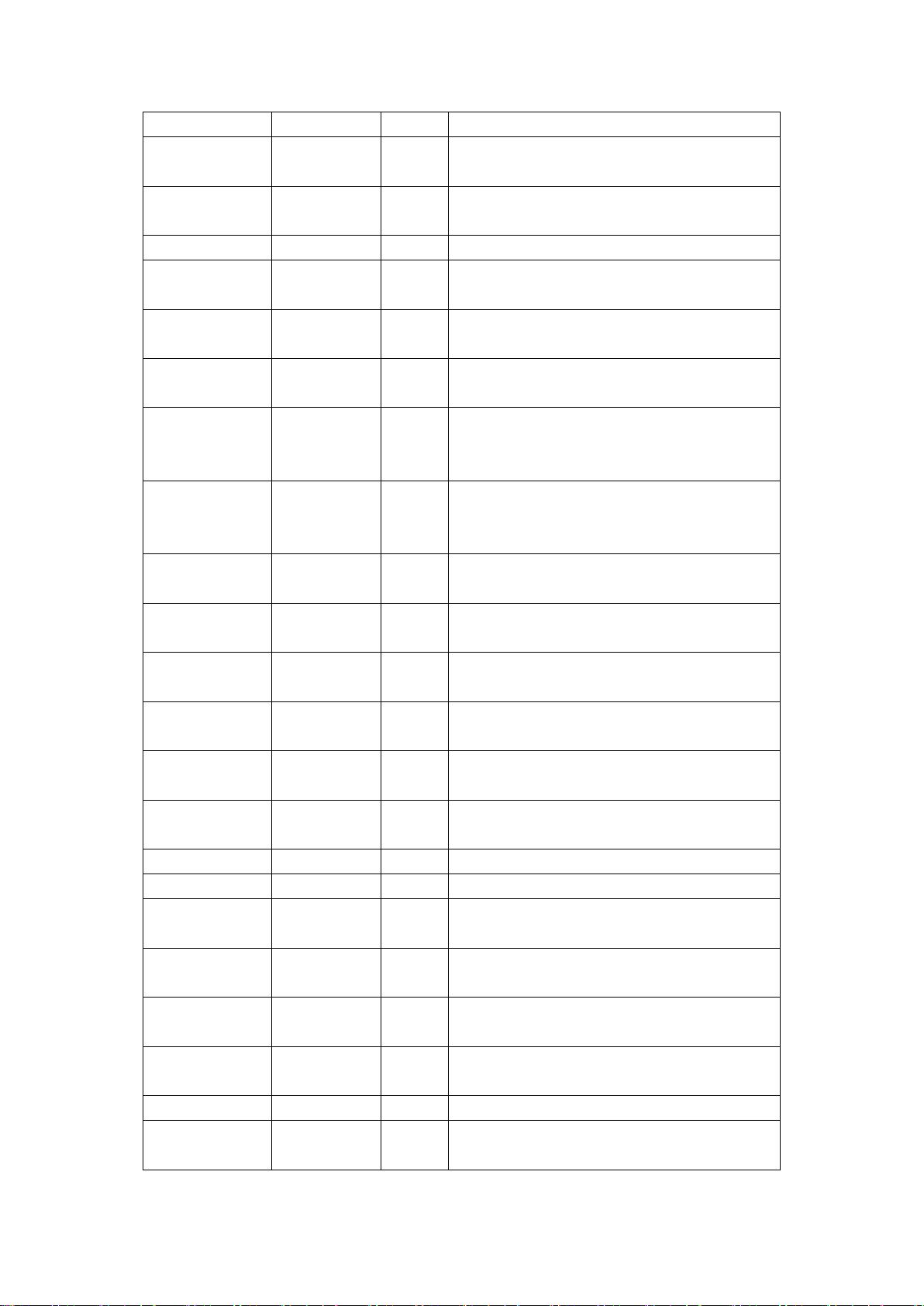

4. 引脚说明

引脚

I/O 描述

编号

名称

1

CE

输入

芯片使能,高电平有效。

2、4、25、31、

34、39、40

GND 地平面 VCO 地平面。

3 VbiasVCO 旁路

VCO

偏置,

10uF

电容连接至

GND

,尽可能

靠近引脚。

5 SYNC 输入 相位同步引脚。具有可编程阈值。

6

、

14

GND

地平面

数字地平面。

7 VccDIG 供电

数字电源,建议使用去耦电容将其旁路至数

字地。

8 OSCinP 输入

参考输入时钟 (+)

。高阻抗自偏压引脚。需要

交流耦合电容器

(

建议使用

0.1 μF

)。

9 OSCinM 输入

参考输入时钟 (-)。高阻抗自偏压引脚。需要

交流耦合电容器(建议使用 0.1 μF)。

10

VregIN

旁路

输入参考路径稳压器输出。

1μF

电容接地。尽

可能靠近引脚。

11 VccCP 供电

Pump 电源,建议使用去耦电容将其旁路至电

荷泵接地。

12 CPout 输出

Pump

电流输出,建议将环路滤波器的

C1

连

接到引脚附近。

13

GND

地平面

Pump

电流接地平面。

15 VccMASH 供电

数字电源,建议使用去耦电容将其旁路至数

字地。

16 SCK 输入

SPI 时钟。高阻抗 CMOS 输入。1.8 V-3.3V 逻

辑电平。

17 SDI 输入

SPI 数据。高阻抗 CMOS 输入。1.8 V-3.3V 逻

辑电平。

18 RFoutBM 输出

差分输出

B (-)

。需要一个尽可能靠近

Vcc

引

脚的上拉(通常为 50Ω 电阻)。可用作输出信

号或 SYSREF 输出。

19 RFoutBP 输出

差分输出 B (+)。需要一个尽可能靠近 Vcc 引

脚的上拉(通常为 50Ω 电阻)。可用作输出信

号或 SYSREF 输出。

20 MUXout 输出

多路输出引脚——锁定检测、回读、诊断、斜

坡状态。

21 VccBUF 供电

输出缓冲电源。建议使用去耦电容将其旁路

至

RFout

接地。

22 RFoutAM 输出

差分输出

A (-)

。需要在尽可能靠近引脚的位

置连接一个 50Ω 的电阻上拉至 Vcc。

23 RFoutAP 输出

差分输出 A (+)。需要在尽可能靠近引脚的位

置连接一个 50Ω 的电阻上拉至 Vcc。

24 CSB 输入

SPI 锁存器,片选信号。高阻抗 CMOS

输入。

1.8 V

至

3.3 V

逻辑电平。

26 VccVCO2 供电

VCO

电源。建议使用去耦电容将其旁路至

VCO 接地。

27

VbiasVCO2

旁路

VCO

偏置。

1μF

电容连接至

VCO

接地平面

。

28

SysRefReq

输入

用于支持

JESD204B

的

SYSREF

请求。

29 VrefVCO2 旁路

VCO

参考电源。需要一个

10μF

的电容与

VCO 接地相连。

30 RampClk 输入

用于斜坡模式的输入引脚,在手动斜坡模式

下可用作斜坡时钟或触发输入引脚

32 RampDir 输入

用于斜坡模式的输入引脚,可用于在手动斜

坡模式下改变斜坡方向或作为触发输入。

33 VbiasVARAC 旁路

VCO

变容偏置。

10μF

的电容连接至

VCO

接

地平面

35

Vtune

输入

VCO

调谐电压输入

36 VrefVCO 旁路

VCO

参考电源。需要一个

10μF

的电容与

VCO 接地相连。

37 VccVCO 供电 VCO

电源。建议使用去耦电容将其旁路接地。

38 VregVCO 旁路 VCO regulator node.1μF 电容接地。

DAP GND 接地 射频输出接地。

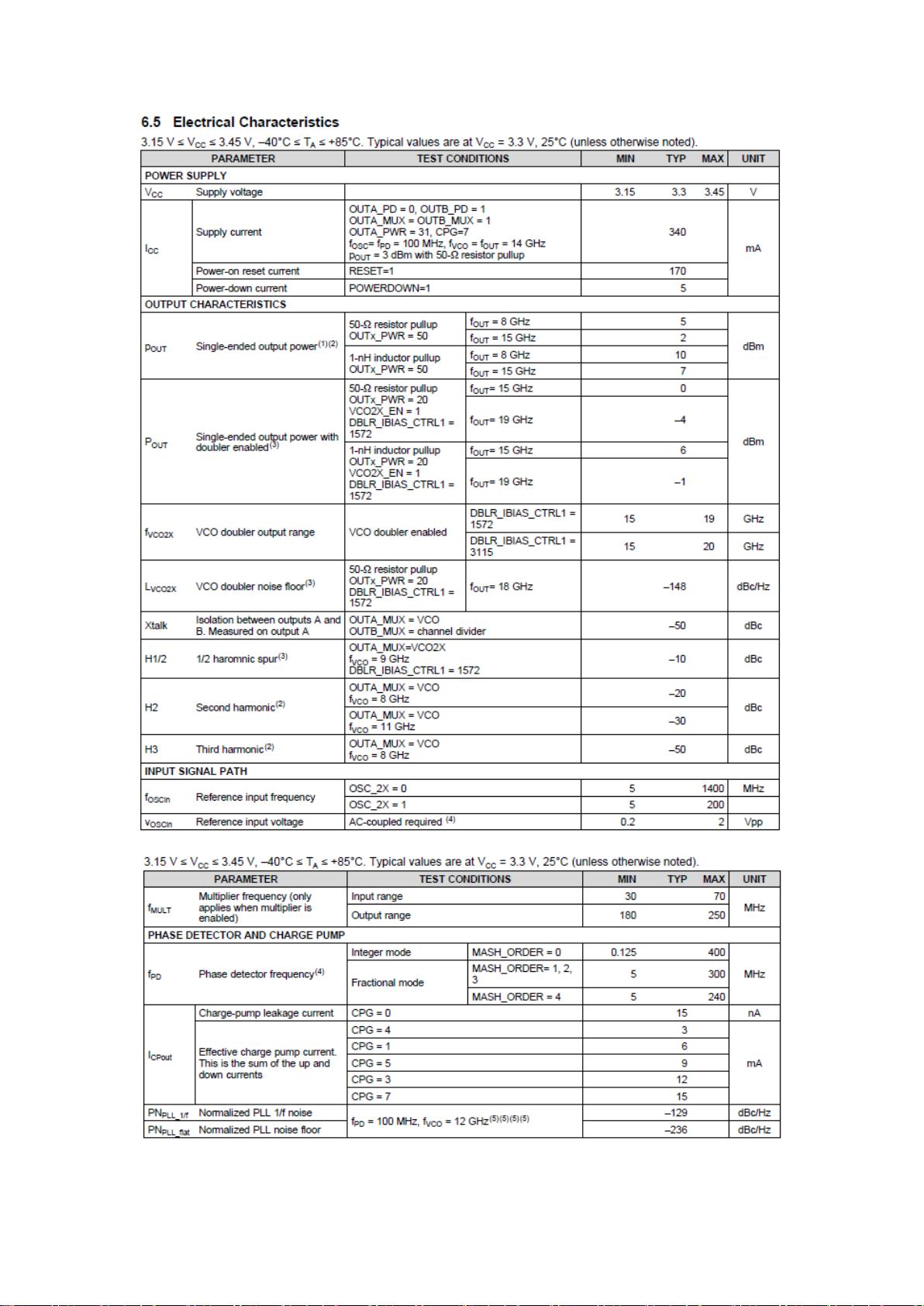

5. 技术规格

(1) 输出功率为去除微带线损耗以及使用手动调谐器匹配后的单端输出功率;

剩余55页未读,继续阅读

资源评论

虚空之月&&轮舞者

- 粉丝: 58

- 资源: 13

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功