STM32F4系列芯片中文学习资料

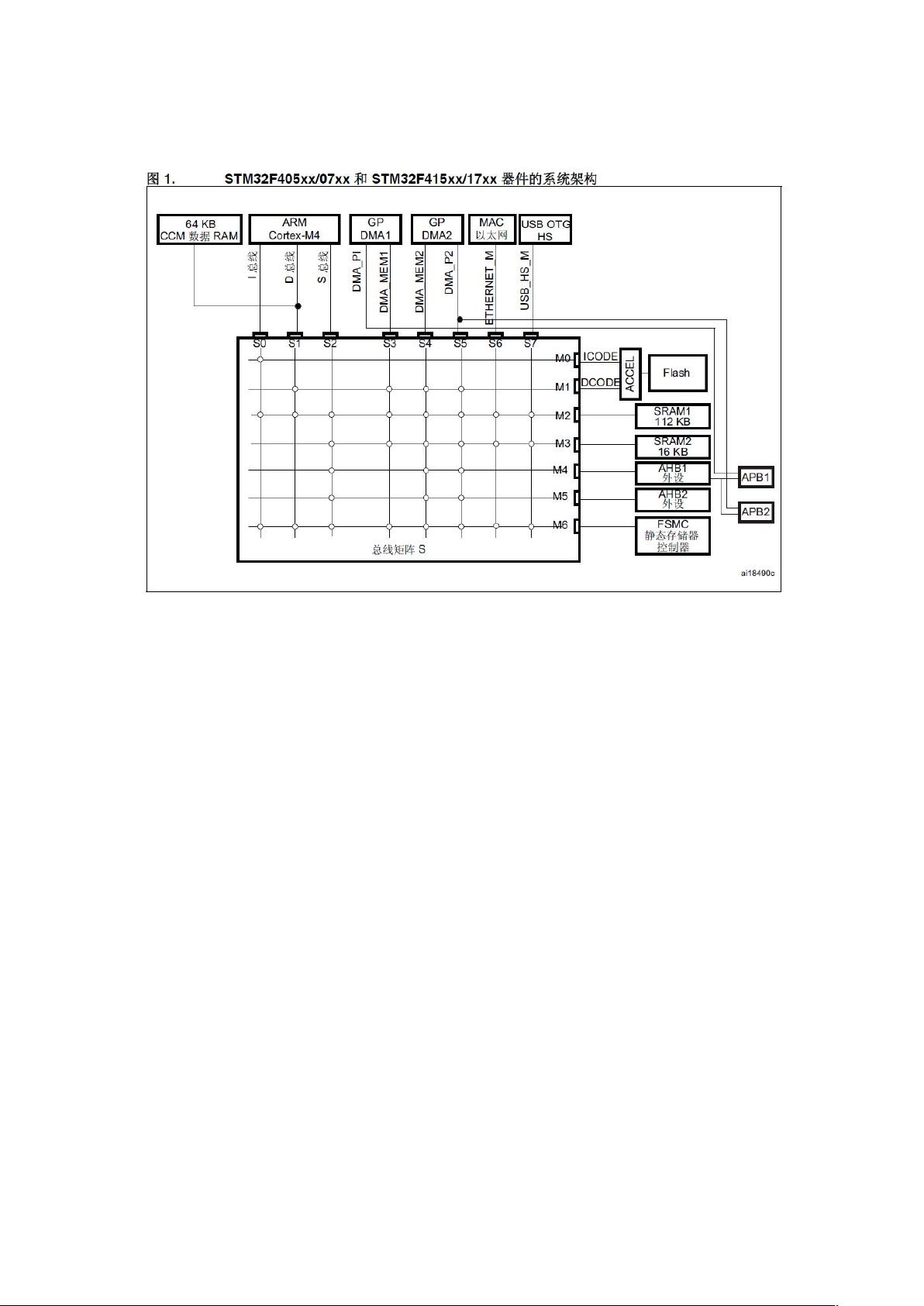

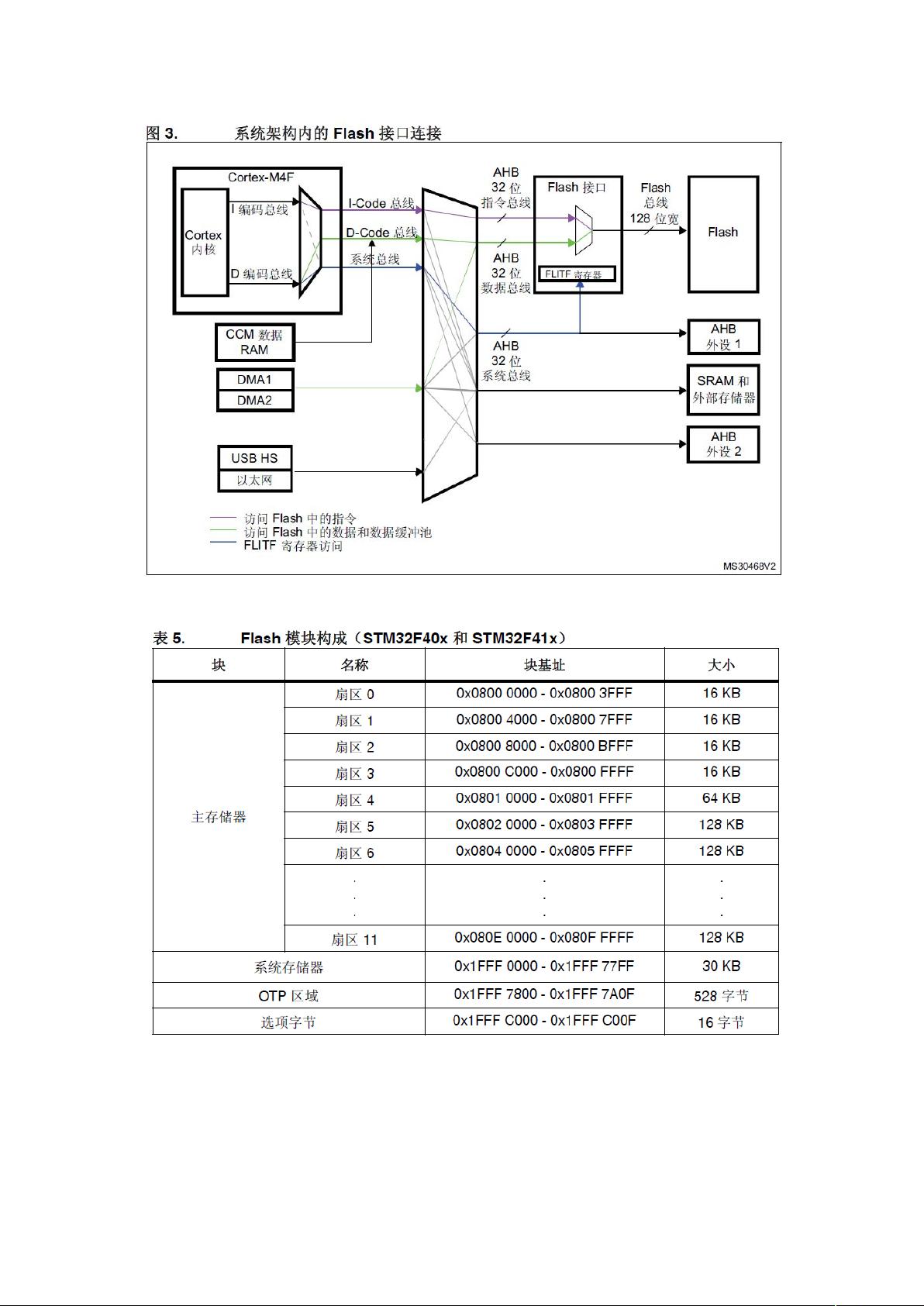

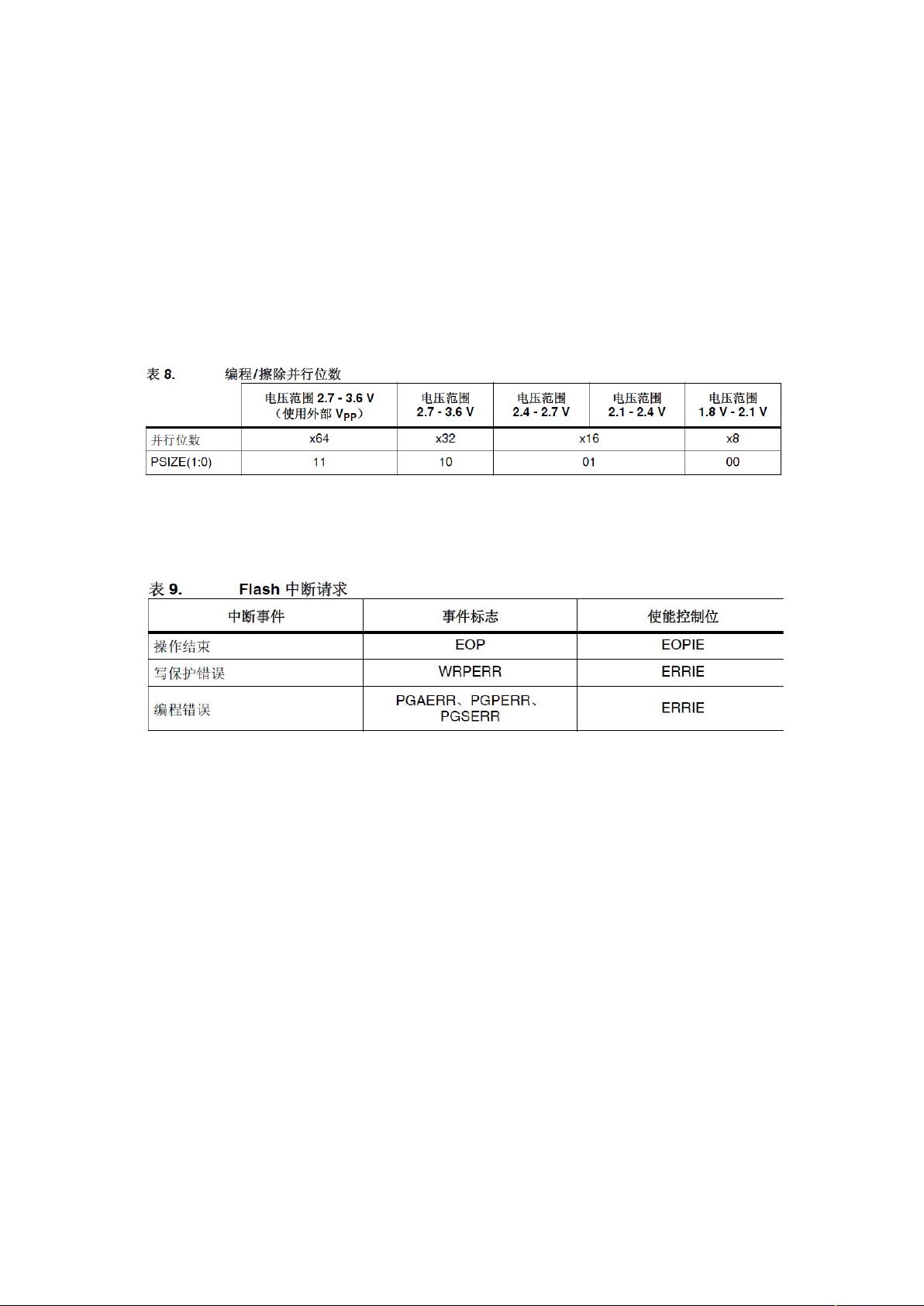

STM32F4系列芯片中文学习资料 本资源为STM32F4系列芯片的中文学习资料,涵盖STM32F40、STM32F41、STM32F42、STM32F43系列芯片的详细学习笔记,对初学者非常有用。 存储器和总线架构 STM32F4系列芯片具有64 KB CCM(内核耦合存储器),数据RAM不属于总线矩阵,只能通过CPU对其进行访问。对APB寄存器执行16位或8位访问时,该访问将转换为32位访问:总线桥将16位或8位数据复制后提供给32位向量。 存储器组织结构程序存储器、数据存储器、寄存器和I/O端口排列在同一个顺序的4 GB地址空间内。各字节按小端格式在存储器中编码。字中编号最低的字节被视为该字的最低有效字节,而编号最高的字节被视为最高有效字节。 嵌入式SRAM STM32F405xx/07xx和STM32F415xx/17xx带有4 KB备份SRAM(请参见第5.1.2节:电池备份域)和192 KB系统SRAM系统SRAM分为三个块: ● 映射在地址0x2000 0000的112 KB和16 KB块 ● 映射在地址0x2002 0000的64 KB块(适用于STM32F42xxx和STM32F43xxx) AHB主总线支持并发SRAM访问(通过以太网或USB OTG HS):例如,当CPU对112 KB或64 KB SRAM进行读/写操作时,以太网MAC可以同时对16 KBSRAM进行读/写操作。 ● 在地址0x1000 0000映射的64 KB块,只能供CPU通过数据总线访问。 位段 Cortex™-M4F存储器映射包括两个位段区域。这些区域将存储器别名区域中的每个字映射到存储器位段区域中的相应位。在别名区域写入字时,相当于对位段区域的目标位执行读-修改-写操作。 自举配置 BOOT0为专用引脚,而BOOT1则与GPIO引脚共用。一旦完成对BOOT1的采样,相应GPIO引脚即进入空闲状态,可用于其它用途。器件退出待机模式时,还会对BOOT引脚重新采样。 嵌入式自举程序模式 用于通过以下串行接口重新编程Flash: ● USART1(PA9/PA10) ● USART3(PB10/11和PC10/11) ● CAN2(PB5/13) ● USB OTG FS(PA11/12)从设备模式(DFU:器件固件升级) 嵌入式自举程序代码位于系统存储器中,在芯片生产期间由ST编程。 物理重映射选择 自举引脚后,应用程序软件可以将某些存储器设定为从代码空间进行访问(这样,可通过ICode总线而非系统总线执行代码)。这样的修改通过在SYSCFG控制器中编程第8.2.1节:SYSCFG存储器重映射寄存器(SYSCFG_MEMRMP)来实现。 嵌入式Flash接口 主要特性: ● Flash读操作 ● Flash编程/擦除操作 ● 读/写保护 ● I-Code上的预取操作 ● I-Code上的64个缓存(128位宽) ● D-Code上的8个缓存(128位宽) ● 对于STM32F40x和STM32F41x,容量高达1 MB;对于STM32F42x和STM32F43x,容量高达2 MB ● 128位宽数据读取 ● 字节、半字、字和双字数据写入 ● 扇区擦除与全部擦除 存储器组织结构Flash结构如下: — 主存储器块,分为4个16 KB扇区、1个64 KB扇区和7个128 KB扇区 — 系统存储器,器件在系统存储器自举模式下从该存储器启动 — 512字节OTP(一次性可编程),用于存储用户数据OTP区域还有16个额外字节,用于锁定对应的OTP数据块。 — 选项字节,用于配置读写保护、BOR级别、软件/硬件看门狗以及器件处于待机或停止模式下的复位。

剩余29页未读,继续阅读

- 粉丝: 0

- 资源: 9

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜 信息提交成功

信息提交成功