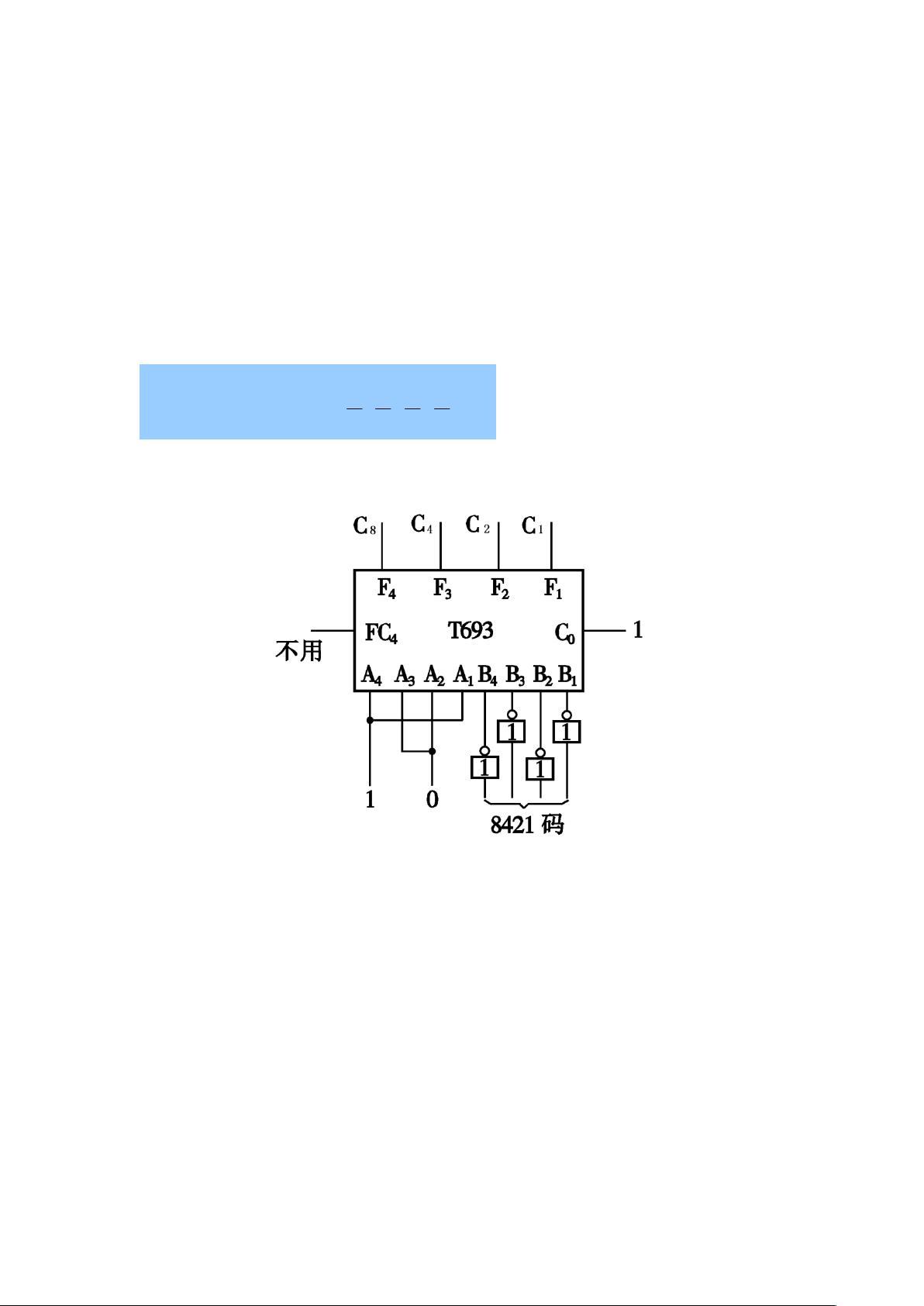

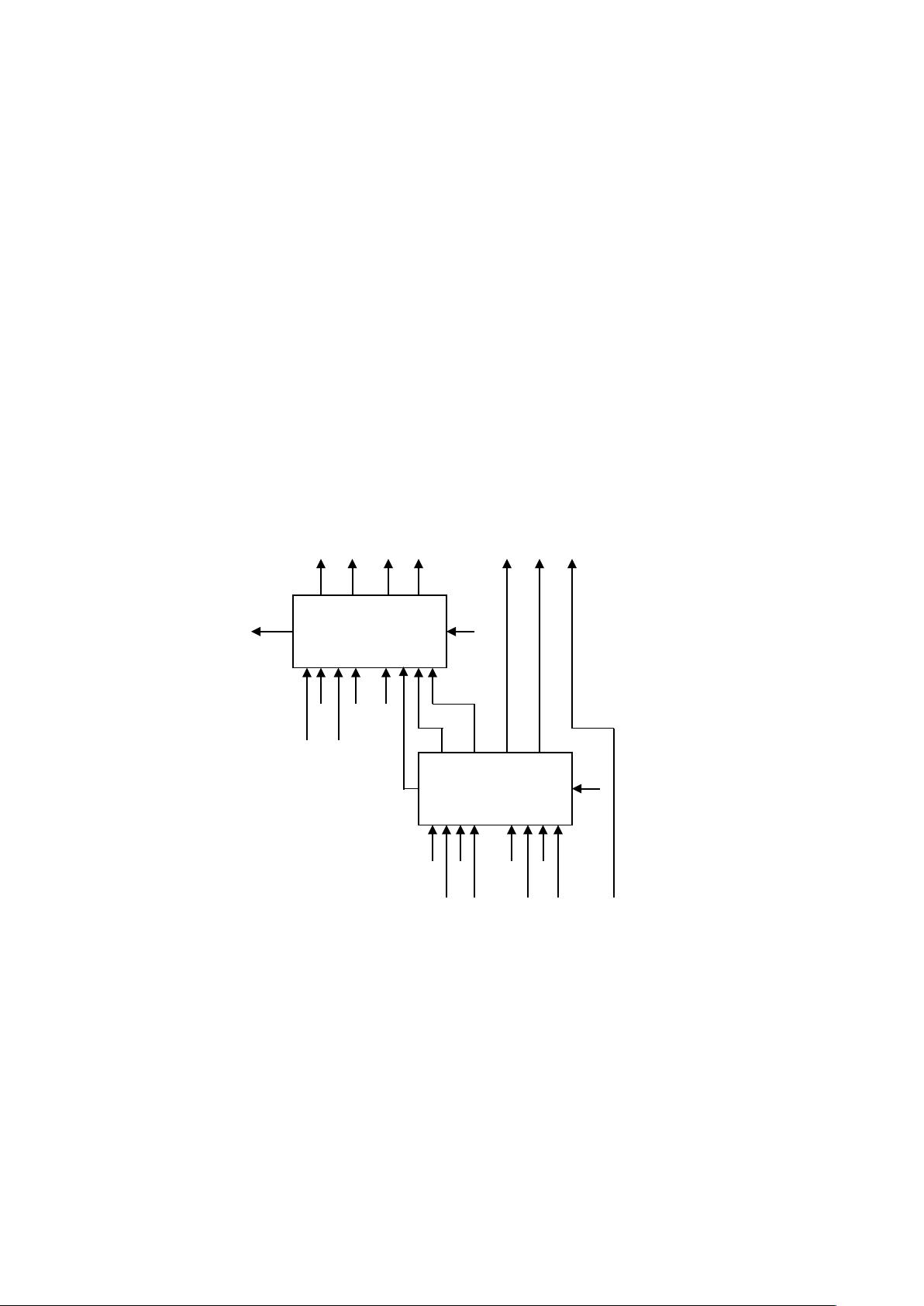

### 数字逻辑知识点总结 #### 一、8421码对9求补的逻辑电路设计 **知识点:** - **8421码:** 是一种常用的BCD码(Binary-Coded Decimal,二进制编码的十进制数),其中每一位分别代表十进制数的千位、百位、十位和个位。 - **对9求补:** 对于BCD码来说,对9求补意味着将给定的BCD码转换为其与9的补码。例如,如果有一个8421码为0101(即十进制数5),那么它的对9补码就是0100(即十进制数4)。 **设计方法:** 1. **确定输入输出:** 输入为8421码`B8B4B2B1`,输出为对9的补码`C8C4C2C1`。 2. **构建逻辑电路:** 通过分析8421码与对9补码之间的关系,可以构建相应的逻辑电路来实现转换。具体来说,可以通过使用4位二进制并行加法器和一些辅助逻辑门来完成这一过程。 **例题解析:** - 设输入8421码为`B8B4B2B1`,输出为`C8C4C2C1`。通过观察输入输出的关系,可以构建相应的逻辑电路图。 **示例电路图**(图1) #### 二、8421码到二进制码的转换 **知识点:** - **二进制码:** 一种表示数值的编码方式,每个数位只有两种可能的状态(0或1)。 - **8421码到二进制码转换:** 将8421码表示的十进制数转换为对应的二进制码。 **设计方法:** 1. **定义输入输出:** 输入为8421码表示的两位十进制数`D80D40D20D10D8D4D2D1`,输出为相应的二进制码`B6B5B4B3B2B1B0`。 2. **计算转换规则:** 根据输入的8421码,计算出对应的二进制码值。 3. **构建逻辑电路:** 使用两个4位二进制并行加法器和其他必要的逻辑门来实现转换。 **例题解析:** - 给定输入为8421码`D80D40D20D10D8D4D2D1`,输出为二进制码`B6B5B4B3B2B1B0`。通过具体的运算步骤,可以得出转换逻辑。 **示例电路图**(图2) #### 三、1位十进制加法器的设计 **知识点:** - **8421码:** 同上所述。 - **加法器:** 一种用于执行加法运算的电子电路。 - **1位十进制加法器:** 可以处理1位十进制数加法的加法器。 **设计方法:** 1. **确定输入输出:** 输入为两个8421码表示的1位十进制数,输出为8421码表示的加法结果。 2. **分析运算范围:** 由于是1位十进制数相加,所以输入的最大值为9,输出的最大值为19。 3. **设计修正电路:** 由于加法结果需要转换回8421码,因此需要设计一个修正电路来确保输出符合8421码的要求。 **例题解析:** - 输入为两个8421码表示的1位十进制数,输出也为8421码表示的加法结果。通过对不同输入情况的分析,可以得出修正函数真值表。 **示例电路图**(图3) #### 四、使用3-8线译码器实现逻辑函数 **知识点:** - **3-8线译码器:** 一种具有三个输入和八个输出的译码器,常用于将二进制代码转换成对应的十进制代码。 - **逻辑函数实现:** 使用特定的逻辑门组合来实现所需的逻辑函数。 **设计方法:** 1. **定义逻辑函数:** 明确所需实现的逻辑函数表达式。 2. **使用译码器:** 根据逻辑函数的表达式,选择合适的输入信号连接到3-8线译码器的输入端口。 3. **添加必要的逻辑门:** 在译码器的输出端添加必要的逻辑门来实现最终的逻辑函数。 **例题解析:** - 实现逻辑函数`F(A, B, C)`,通过将逻辑表达式转化为与译码器输出相对应的形式,进而设计出相应的逻辑电路图。 **示例电路图**(图4) #### 五、2421码的奇偶校验位产生电路 **知识点:** - **2421码:** 一种特殊的BCD码,每位的权重分别为2、4、2、1。 - **奇偶校验位:** 用于检测传输错误的一种校验机制,通过增加一个额外的位来确保数据中的1的总数为奇数或偶数。 **设计方法:** 1. **确定输入输出:** 输入为2421码`ABCD`,输出为奇偶校验位`P`。 2. **列出真值表:** 根据输入输出之间的关系列出真值表。 3. **设计电路:** 使用4-16线译码器和必要的逻辑门来实现奇偶校验位的产生电路。 **例题解析:** - 输入为2421码`ABCD`,输出为奇偶校验位`P`。通过列出真值表,可以得出实现电路的方法。 **示例电路图**(图5) #### 六、优先编码器的工作原理 **知识点:** - **优先编码器:** 一种能够同时处理多个输入信号,并根据优先级顺序选择输出信号的编码器。 - **74LS148:** 一种常见的8通道优先编码器芯片。 **工作原理:** - 当优先编码器74LS148的输入端接0时,表示没有信号输入;当输入端接1时,表示有信号输入。 - 输出端`Q`表示编码的结果,`QEX`表示是否允许编码的信号,`QS`表示是否允许输出的信号。 **例题解析:** - 当输入`I7I6I5I4I3I2I1I0`为11010001时,输出状态为`QCQBQA`=010,表示编码了`I5`,且`QEX`=0,`QS`=1。 **示例电路图**(图6) #### 七、使用数据选择器进行代码转换 **知识点:** - **数据选择器:** 一种多路输入、单路输出的开关器件。 - **余3码到8421码的转换:** 将余3码转换为标准的8421码。 **设计方法:** 1. **定义输入输出:** 输入为余3码`ABCD`,输出为8421码`WXYZ`。 2. **确定转换规则:** 根据余3码与8421码之间的转换规则,确定数据选择器的数据输入端。 3. **构建转换电路:** 使用数据选择器和必要的逻辑门来实现代码转换。 **例题解析:** - 输入为余3码`ABCD`,输出为8421码`WXYZ`。通过确定各个数据选择器的数据输入端,可以构建出转换电路。 **示例电路图**(图6) #### 八、4路数据选择器的功能实现 **知识点:** - **4路数据选择器:** 一种具有四个输入端、一个输出端和两个选择控制端的开关器件。 - **“一致性”检测功能:** 一种检查输入信号是否一致的功能。 **设计方法:** 1. **定义输入输出:** 输入为三个变量`A`、`B`、`C`,输出为一致性检测的结果`W`。 2. **构建逻辑函数:** 根据一致性检测的逻辑需求,构建逻辑函数表达式。 3. **实现电路:** 使用4路数据选择器和必要的逻辑门来实现一致性检测功能。 **例题解析:** - 当选择控制变量`A1`、`A0`分别接变量`A`、`B`,数据输入端`D0`、`D1`、`D2`、`D3`依次接`C`、0、0、`C`时,电路实现的是三变量的一致性检测功能。 **示例电路图**(图8) - 以上是对给定习题的详细解析,每一道题都涵盖了相关的知识点和设计方法,旨在帮助学生深入理解数字逻辑的基本概念和技术应用。

剩余12页未读,继续阅读

- 粉丝: 802

- 资源: 2940

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- (源码)基于Spring Boot和MyBatis的社区问答系统.zip

- (源码)基于Spring Boot和WebSocket的人事管理系统.zip

- (源码)基于Spring Boot框架的云网页管理系统.zip

- (源码)基于Maude和深度强化学习的智能体验证系统.zip

- (源码)基于C语言的Papageno字符序列处理系统.zip

- (源码)基于Arduino的水质监测与控制系统.zip

- (源码)基于物联网的智能家居门锁系统.zip

- (源码)基于Python和FastAPI的Squint数据检索系统.zip

- (源码)基于Arduino的图片绘制系统.zip

- (源码)基于C++的ARMA53贪吃蛇游戏系统.zip

信息提交成功

信息提交成功