Copyright © 2006-2010 ARM Limited. All rights reserved.

ARM DDI 0344K (ID060510)

Cortex

™

-A8

Revision: r3p2

Technical Reference Manual

ARM DDI 0344K Copyright © 2006-2010 ARM Limited. All rights reserved. ii

ID060510 Non-Confidential

Cortex-A8

Technical Reference Manual

Copyright © 2006-2010 ARM Limited. All rights reserved.

Release Information

The following changes have been made to this book.

Proprietary Notice

Words and logos marked with

®

or

™

are registered trademarks or trademarks owned by ARM Limited, except as

otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of

their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be

adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the

product and its use contained in this document are given by ARM in good faith. However, all warranties implied or

expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any

loss or damage arising from the use of any information in this document, or any error or omission in such information,

or any incorrect use of the product.

Some material in this document is based on ANSI/IEEE Std 754-1985, IEEE Standard for Binary Floating-Point

Arithmetic and on IEEE Std. 1500-2005, IEEE Standard Testability Method for Embedded Core-based Integrated

Circuits. The IEEE disclaims any responsibility or liability resulting from the placement and use in the described

manner.

Where the term ARM is used it means “ARM or any of its subsidiaries as appropriate”.

Confidentiality Status

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license

restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this

document to.

Product Status

The information in this document is final, that is for a developed product.

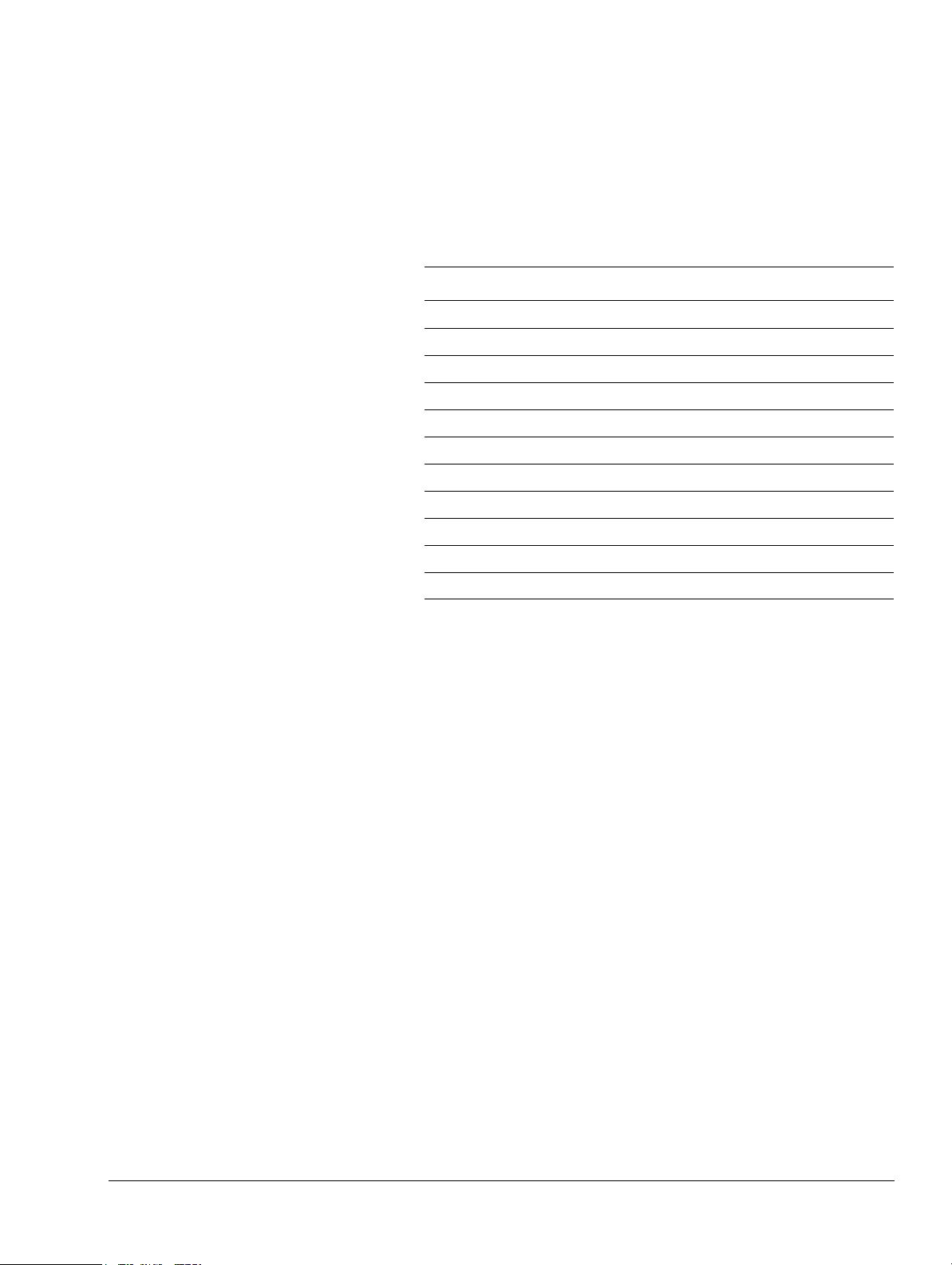

Change history

Date Issue Confidentiality Change

18 July 2006 A Confidential First release for r1p0

13 December 2006 B Non-Confidential First release for r1p1

13 July 2007 C Non-Confidential First release for r2p0

16 November 2007 D Non-Confidential First release for r2p1

14 March 2008 E Non-Confidential First release for r2p2

06 October 2008 F Non-Confidential First release for r2p3

24 October 2008 G Non-Confidential Restricted Access First release for r3p0

03 December 2008 H Non-Confidential Unrestricted Access Second release for r3p0

30 January 2009 I Non-Confidential Unrestricted Access First release for r3p1

15 May 2009 J Non-Confidential Unrestricted Access First release for r3p2

07 May 2010 K Non-Confidential Unrestricted Access Second release for r3p2

ARM DDI 0344K Copyright © 2006-2010 ARM Limited. All rights reserved. iii

ID060510 Non-Confidential

Web Address

http://www.arm.com

ARM DDI 0344K Copyright © 2006-2010 ARM Limited. All rights reserved. iv

ID060510 Non-Confidential

Contents

Cortex-A8 Technical Reference Manual

Preface

About this manual ..................................................................................................... xxi

Feedback ................................................................................................................. xxv

Chapter 1 Introduction

1.1 About the processor ................................................................................................. 1-2

1.2 ARMv7-A architecture .............................................................................................. 1-3

1.3 Components of the processor .................................................................................. 1-4

1.4 External interfaces of the processor ........................................................................ 1-7

1.5 Debug ...................................................................................................................... 1-8

1.6 Power management ................................................................................................. 1-9

1.7 Configurable options .............................................................................................. 1-10

1.8 Product documentation and architecture ............................................................... 1-11

1.9 Product revisions ................................................................................................... 1-13

Chapter 2 Programmers Model

2.1 About the programmers model ................................................................................ 2-2

2.2 Thumb-2 instruction set ........................................................................................... 2-3

2.3 ThumbEE instruction set .......................................................................................... 2-4

2.4 Jazelle Extension ..................................................................................................... 2-7

2.5 Security Extensions architecture ............................................................................. 2-9

2.6 Advanced SIMD architecture ................................................................................. 2-11

2.7 VFPv3 architecture ................................................................................................ 2-12

2.8 Processor operating states .................................................................................... 2-13

2.9 Data types .............................................................................................................. 2-14

2.10 Memory formats ..................................................................................................... 2-15

2.11 Addresses in a processor system .......................................................................... 2-16

2.12 Operating modes ................................................................................................... 2-17

2.13 Registers ................................................................................................................ 2-18

Contents

ARM DDI 0344K Copyright © 2006-2010 ARM Limited. All rights reserved. v

ID060510 Non-Confidential

2.14 The program status registers ................................................................................. 2-21

2.15 Exceptions ............................................................................................................. 2-27

2.16 Software consideration for Security Extensions .................................................... 2-34

2.17 Hardware consideration for Security Extensions ................................................... 2-35

2.18 Control coprocessor ............................................................................................... 2-38

Chapter 3 System Control Coprocessor

3.1 About the system control coprocessor ..................................................................... 3-2

3.2 System control coprocessor registers ...................................................................... 3-7

Chapter 4 Unaligned Data and Mixed-endian Data Support

4.1 About unaligned and mixed-endian data ................................................................. 4-2

4.2 Unaligned data access support ............................................................................... 4-3

4.3 Mixed-endian access support .................................................................................. 4-5

Chapter 5 Program Flow Prediction

5.1 About program flow prediction ................................................................................. 5-2

5.2 Predicted instructions .............................................................................................. 5-3

5.3 Nonpredicted instructions ........................................................................................ 5-6

5.4 Guidelines for optimal performance ......................................................................... 5-7

5.5 Enabling program flow prediction ............................................................................ 5-8

5.6 Operating system and predictor context .................................................................. 5-9

Chapter 6 Memory Management Unit

6.1 About the MMU ........................................................................................................ 6-2

6.2 Memory access sequence ....................................................................................... 6-3

6.3 16MB supersection support ..................................................................................... 6-4

6.4 MMU interaction with memory system ..................................................................... 6-5

6.5 External aborts ......................................................................................................... 6-6

6.6 TLB lockdown .......................................................................................................... 6-7

6.7 MMU software-accessible registers ......................................................................... 6-8

Chapter 7 Level 1 Memory System

7.1 About the L1 memory system .................................................................................. 7-2

7.2 Cache organization .................................................................................................. 7-3

7.3 Memory attributes .................................................................................................... 7-5

7.4 Cache debug ........................................................................................................... 7-7

7.5 Data cache features ................................................................................................. 7-8

7.6 Instruction cache features ........................................................................................ 7-9

7.7 Hardware support for virtual aliasing conditions .................................................... 7-10

7.8 Parity detection ...................................................................................................... 7-11

Chapter 8 Level 2 Memory System

8.1 About the L2 memory system .................................................................................. 8-2

8.2 Cache organization .................................................................................................. 8-3

8.3 Enabling and disabling the L2 cache controller ....................................................... 8-5

8.4 L2 PLE ..................................................................................................................... 8-6

8.5 Synchronization primitives ..................................................................................... 8-10

8.6 Locked access ....................................................................................................... 8-12

8.7 Parity and error correction code ............................................................................ 8-13

Chapter 9 External Memory Interface

9.1 About the external memory interface ....................................................................... 9-2

9.2 AXI control signals in the processor ........................................................................ 9-3

9.3 AXI instruction transactions ..................................................................................... 9-5

9.4 AXI data read/write transactions .............................................................................. 9-6