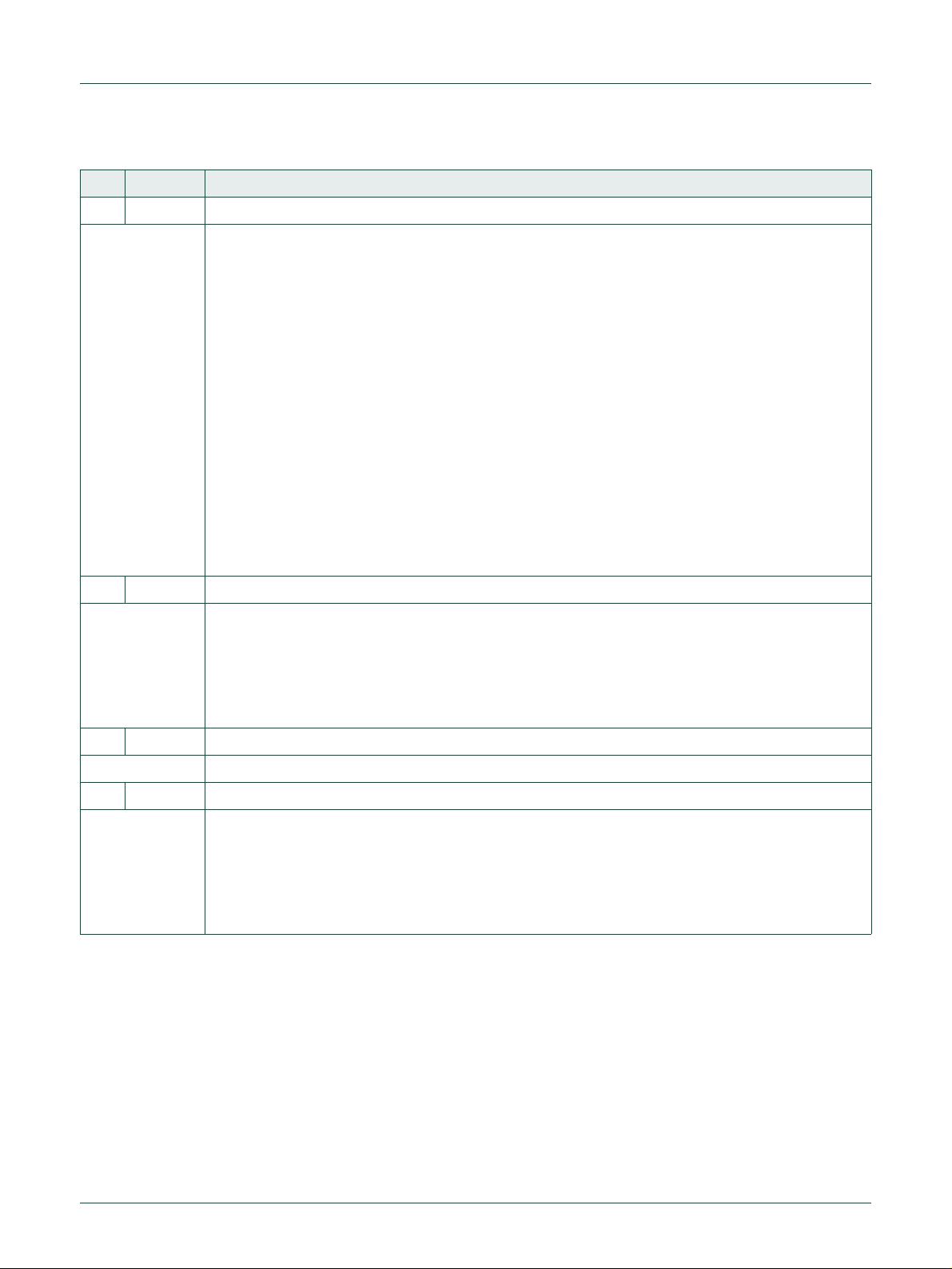

### 关于UM10912LPC546xx用户手册的知识点解析 #### 一、概述 UM10912LPC546xx用户手册是针对NXP半导体公司开发的LPC546xx系列微控制器的一份详尽的技术文档。这份文档包含了该系列微控制器的所有技术细节,旨在帮助工程师们更好地理解和应用这些高性能的微控制器。LPC546xx系列基于ARM Cortex-M4架构,提供了丰富的外设接口和高级特性,使其成为各种嵌入式应用的理想选择。 #### 二、关键技术特性 1. **ARM Cortex-M4内核**:LPC546xx采用了高性能的ARM Cortex-M4处理器内核,支持浮点运算单元(FPU),能够实现高效的数据处理能力。 2. **32位微控制器**:作为一款32位微控制器,LPC546xx具有高速数据处理能力和低功耗特点,适合应用于对性能有较高要求的嵌入式系统中。 3. **丰富的外设接口**: - **LCD控制器**:支持多种LCD显示模式,可直接驱动LCD屏幕,无需额外的外部控制器。 - **Ethernet AVB(音频视频桥接)**:支持高带宽音频视频传输,适用于多媒体应用。 - **SPIFI(串行闪存接口)**:提供高速闪存读写能力,提高存储性能。 - **SCT/PWM(状态控制定时器/脉宽调制)**:用于精密的时间控制和电机控制等场景。 - **USB Host/Device**:支持USB主机和设备模式,便于与其他USB设备通信。 - **CAN FD(灵活数据速率控制器局域网)**:提供高速和灵活的数据传输能力,适用于汽车和其他工业控制系统。 - **I2C/I2S**:支持标准的I2C通信协议和I2S音频接口。 - **EEPROM/Flash/SDRAM控制器**:内置EEPROM、Flash和SDRAM控制器,提供多样化的存储解决方案。 - **DMIC(数字麦克风接口)**:用于连接数字麦克风。 - **SDIO接口/SD卡接口**:支持SD卡读写操作。 - **eCRP(增强型循环冗余校验)**:提供数据完整性验证功能。 - **SHA(安全散列算法)**:支持数据加密和解密操作,确保数据安全性。 4. **EMC(电磁兼容性)设计**:LPC546xx具备良好的EMC特性,能够在复杂的电磁环境中稳定工作。 5. **节能模式**: - 深度睡眠模式下,系统时钟被禁用,所有模拟块默认关闭,但可以通过电源API选择性地维持运行以作为唤醒源。 #### 三、文档修订历史 文档版本的修订历史记录了每次更新的具体内容,包括但不限于新增的功能介绍、错误修正以及技术规范的更改。例如,在2.4版中更新了Section 5.6.8中的Table 80“指向ISP参数数组的指针”的新内容;在2.2版中,修改了I2C/SPI命令的标识符,并添加了有关ISP ReadUID和读取唯一ID编号的部分内容。 #### 四、注意事项 - 所有提供的信息均受法律免责声明的约束。 - 版权归NXP半导体所有,保留所有权利。 UM10912LPC546xx用户手册是一份非常重要的技术文档,它不仅详细介绍了LPC546xx系列微控制器的架构和技术特性,还提供了使用该系列微控制器进行产品设计和开发所需的各种指导和支持。对于从事嵌入式系统设计和开发的专业人员来说,掌握这份手册中的知识点是非常必要的。

剩余1180页未读,继续阅读

- 粉丝: 119

- 资源: 34

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功