XAPP890 (v1.0) September 25, 2012 www.xilinx.com 1

© Copyright 2012 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the

United States and other countries. ARM and Cortex are registered trademarks of ARM in the EU and other countries. All other trademarks are the property of their respective

owners.

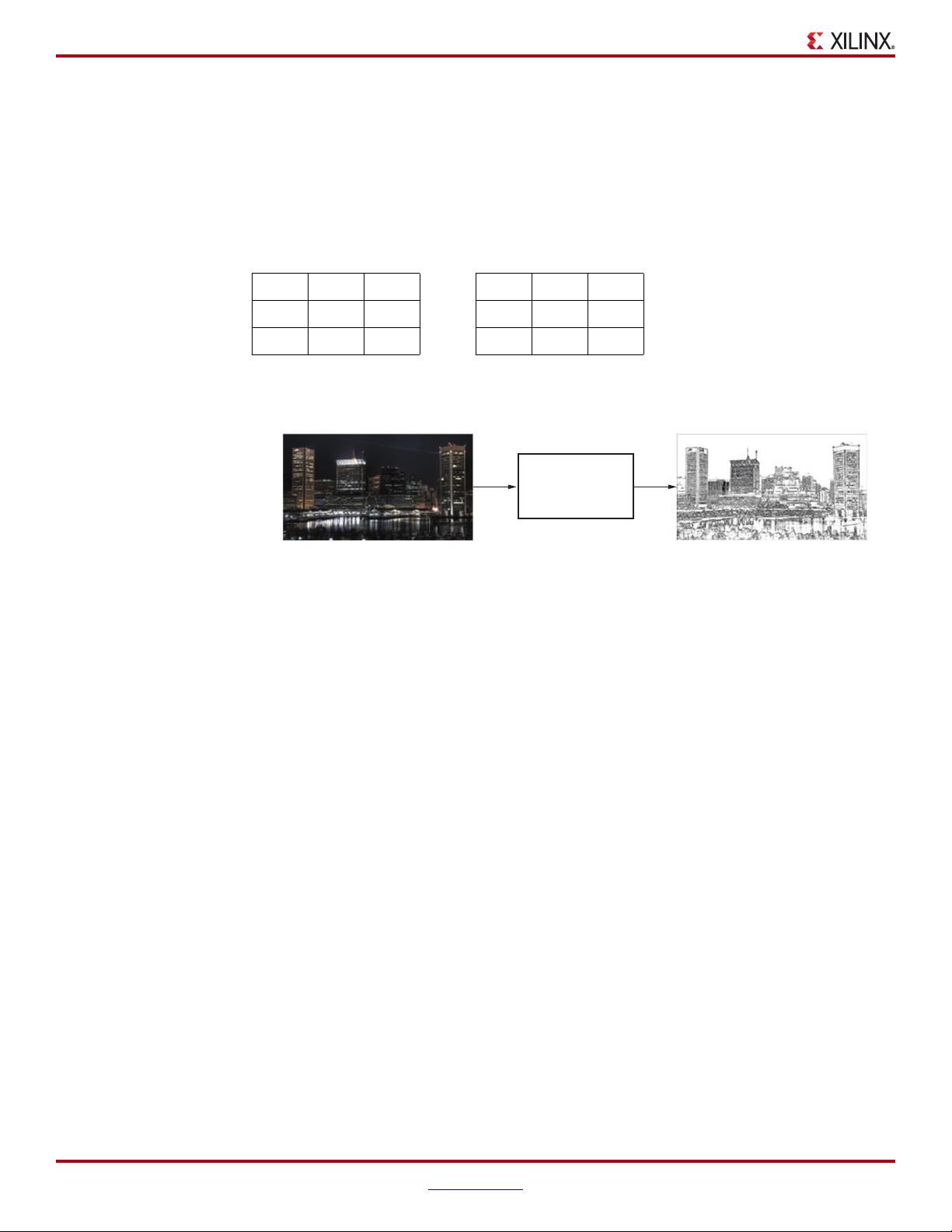

Summary This application note describes how to generate the Sobel edge detection filter in the

Zynq™-7000 All Programmable SoC ZC702 Base Targeted Reference Design (TRD) using the

Vivado™ High-Level Synthesis (HLS) tool. The techniques described in this application note

present the fundamental flow for integrating an IP block generated by the Vivado HLS tool into

a Zynq AP SoC-based system.

Introduction The Vivado HLS tool provides a methodology for migrating algorithms from a processor onto

the FPGA logic. In the context of Zynq devices, this means moving code from the ARM®

dual-core Cortex™-A9 processor to the FPGA logic for acceleration. The code implemented

with the HLS tool in hardware represents the computational bottleneck of the algorithm. This

bottleneck can be discovered through code profiling. For information about profiling processor

code, refer to EDK Concepts, Tools, and Techniques: A Hands-On Guide to Effective

Embedded System Design [Ref 1].

For this application note, the computational bottleneck is the Sobel edge detection algorithm

running at 60 frames per second on a resolution of 1080p. This application note describes how

to take a C description of the algorithm, generate RTL with the HLS tool, and integrate the

resulting block into a hardware system design. This document describes the following aspects

of generating the Sobel edge detection core for the ZC702 Base TRD:

• Sobel Edge Detection Algorithm Overview

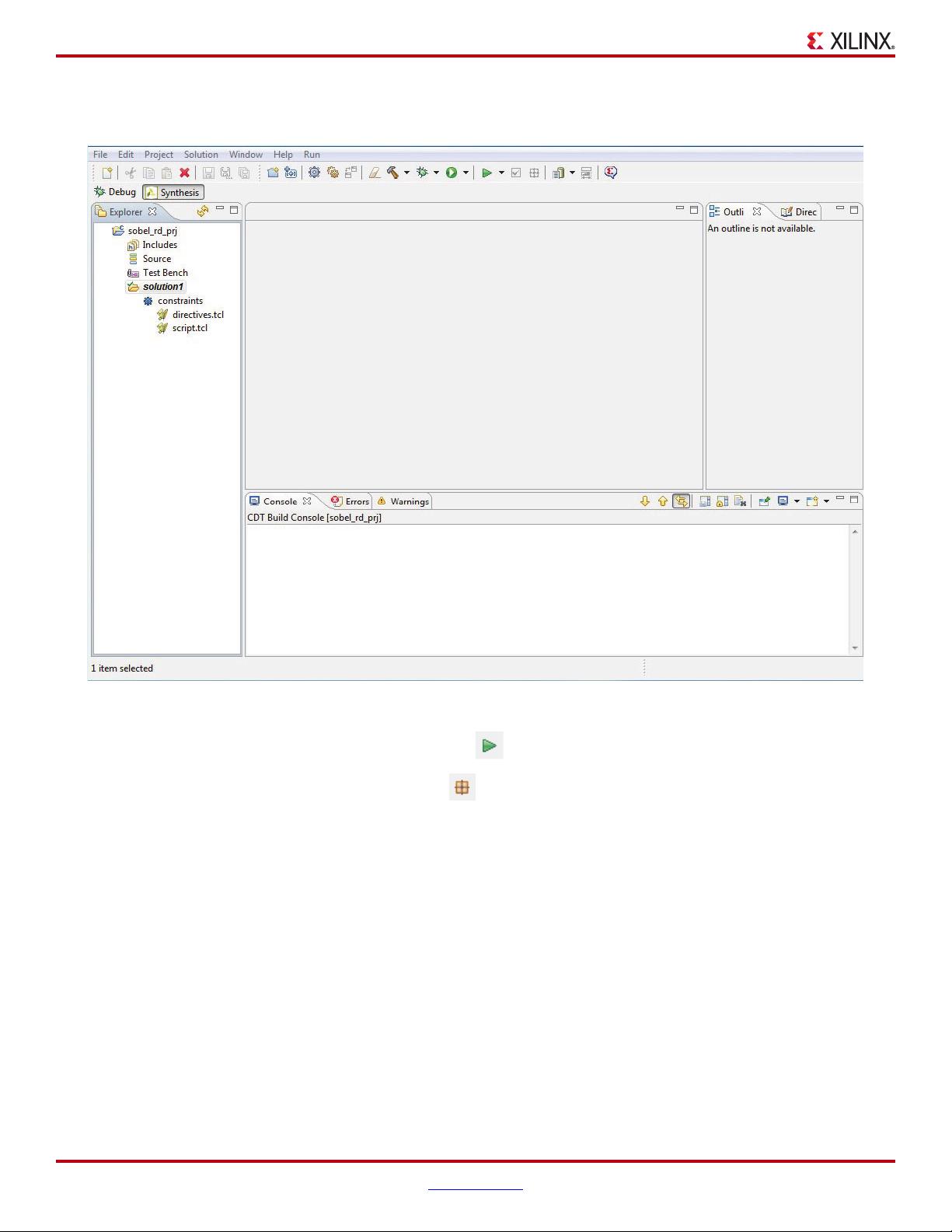

• Implementing the Algorithm in the HLS Tool

• Creating a Linux Driver for the IP Core Generated by the HLS Tool

• Integrating the System into the Zynq Base TRD

Programming

Environment

Specifics

This application note assumes that the user has some general knowledge of the Vivado HLS

tool and XPS. For more information on these tools, see EDK Concepts, Tools, and Techniques:

A Hands-On Guide to Effective Embedded System Design [Ref 1] and Vivado Design Suite

User Guide: High-Level Synthesis [Ref 2].

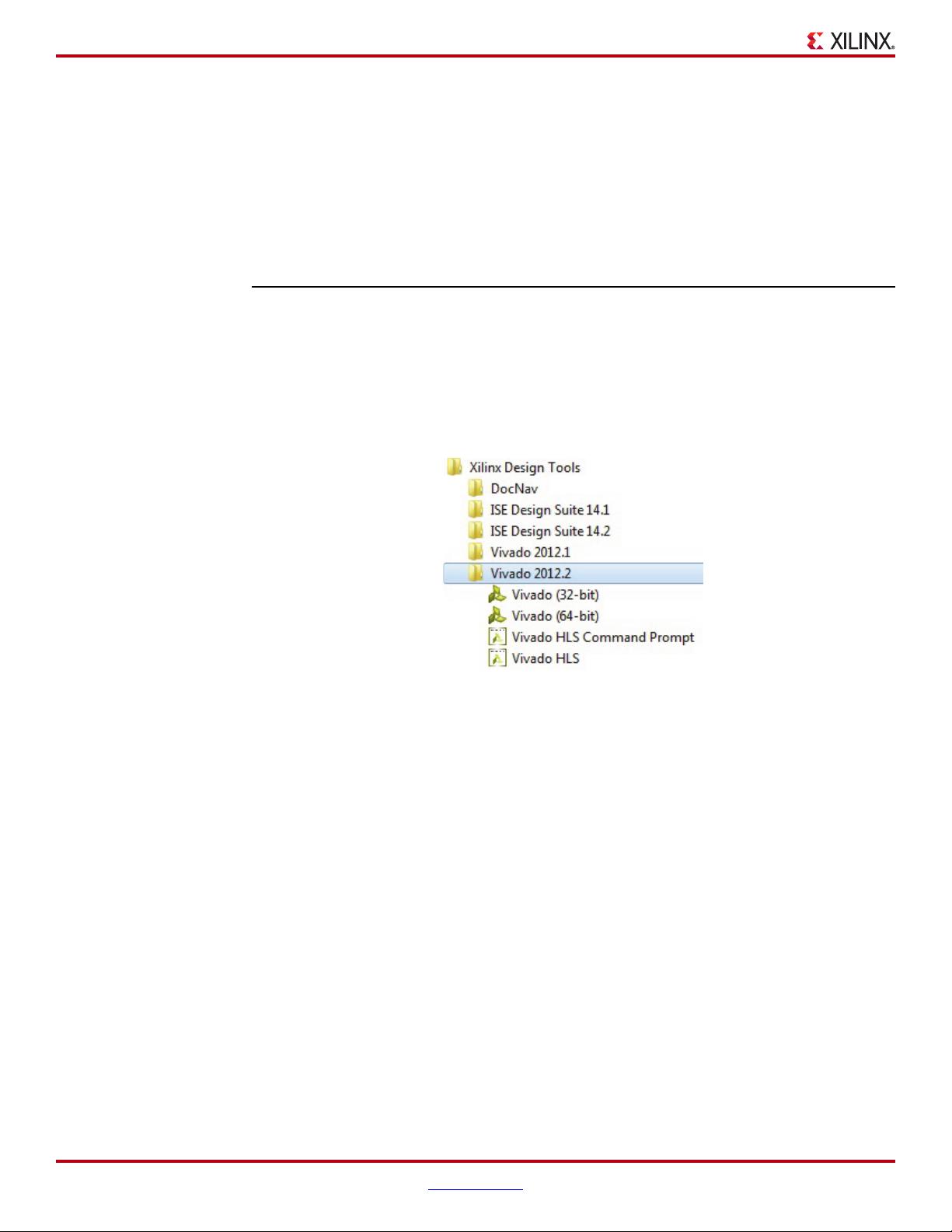

The design in this application note requires the use of the Vivado HLS tool 2012.2 and

ISE® Design Suite: System Edition 14.2.

Required

Hardware

The reference design in this application note requires the Zynq-7000 ZC702 board. For more

information on this hardware platform, refer to the Zynq Base TRD wiki page [Ref 3].

Application Note: Vivado HLS Tool

XAPP890 (v1.0) September 25, 2012

Zynq All Programmable SoC Sobel Filter

Implementation Using the Vivado HLS Tool

Author: Fernando Martinez Vallina, Christian Kohn, and Pallav Joshi

zynq-sobel.rar (2个子文件)

zynq-sobel.rar (2个子文件)  新建文件夹

新建文件夹  xapp890.zip 7.32MB

xapp890.zip 7.32MB xapp890-zynq-sobel-vivado-hls.pdf 1.59MB

xapp890-zynq-sobel-vivado-hls.pdf 1.59MB

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功

- 1

- 2

前往页