没有合适的资源?快使用搜索试试~ 我知道了~

fpga使用说明书 fpga入门必读

需积分: 50 8 下载量 60 浏览量

2009-07-26

14:03:54

上传

评论

收藏 378KB DOC 举报

温馨提示

试读

33页

很好的fpga基础知识,可以让你了解fpga的内部构成,这是学习和使用fpga的关键

资源推荐

资源详情

资源评论

可编程逻辑器件

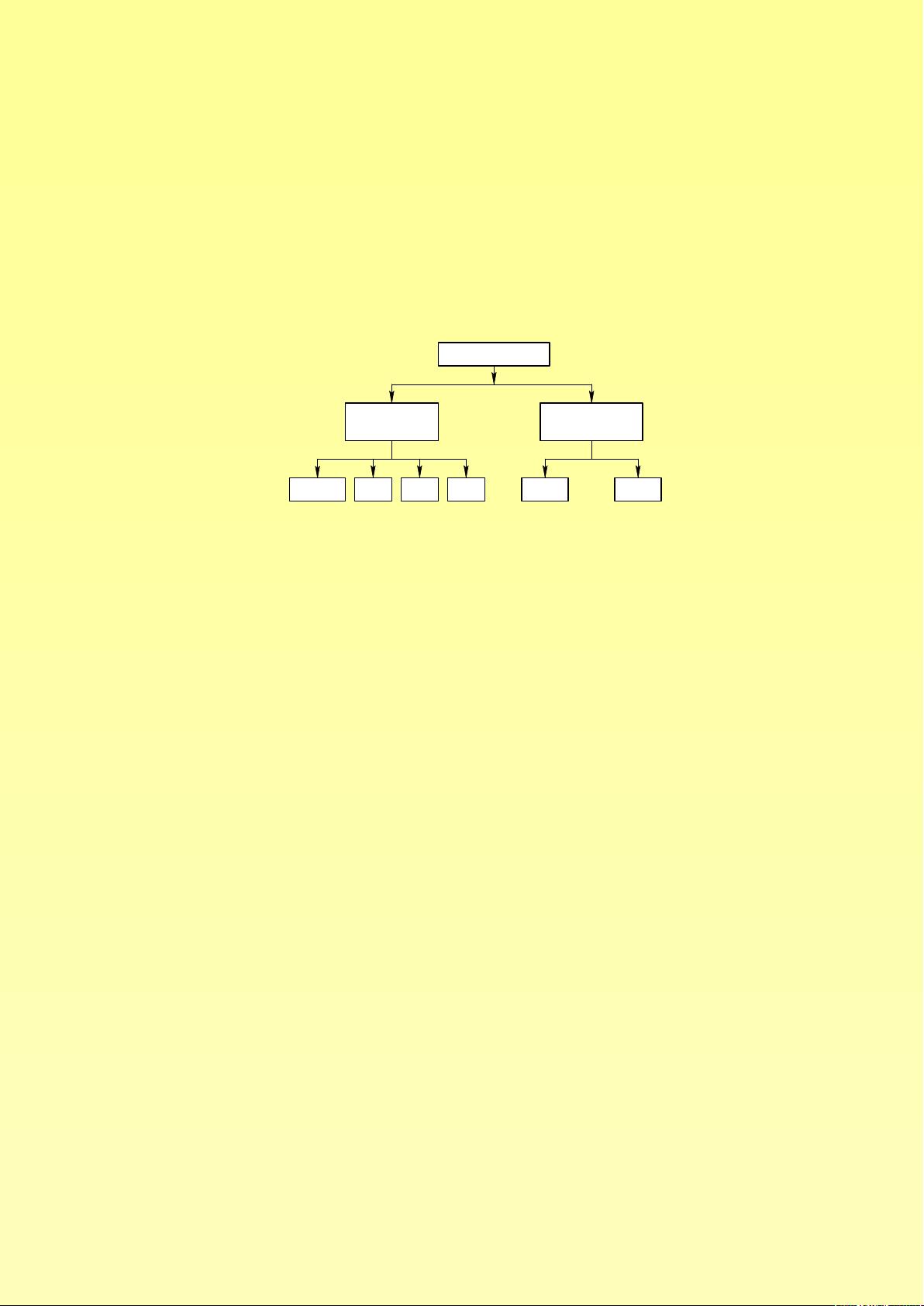

2.1 可编程逻辑器件的分类

2.1.1 可编程逻辑器件按集成度分类

集成度是可编程逻辑器件的一项很重要的指标,如果从集成密度上分类,可分为简单

可编程逻辑器件(SPLD)和高密度可编程逻辑器件(HDPLD)。通常将 PROM、PLA、PAL 和

GAL 这四种 PLD 产品划归为简单可编程逻辑器件,而将 CPLD 和 FPGA 统称为高密度可编

程逻辑器件,如图 2-1 所示。

PROM PLA PAL GAL

¼òµ¥¿É±à³ÌÂß

¼ Æ÷¼þ(SPLD)

CPLD FPGA

¸ßÃܶȿɱà³ÌÂß

¼ Æ÷¼þ(HDPLD)

¿É±à³ÌÂß¼ Æ÷¼þ

图 2-1 可编程逻辑器件按集成度分类

2.1.2 可编程逻辑器件的其他分类方法

目前常用的可编程逻辑器件都是从“与-或阵列”和“门阵列”两类基本结构发展起来的,

所以又可从结构上将其分为两大类:

(1) PLD 器件——基本结构为与或阵列的器件。

(2) FPGA 器件——早期的基本结构为门阵列,目前已发展到逻辑单元 (包含了门、触

发器等)阵列。

PLD 是最早的可编程逻辑器件,它的基本逻辑结构由与阵列和或阵列组成,能够有效

地实现“积之和”形式的布尔逻辑函数。FPGA 是最近 10 年发展起来的另一种可编程逻辑器

件,它的基本结构类似于门阵列,能够实现一些较大规模的复杂数字系统。 PLD 主要通过

修改具有固定内部电路的逻辑功能来编程,FPGA 主要通过改变内部连线的布线来编程。

所有的 CPLD 器件和 FPGA 器件均采用 CMOS 技术,但它们在编程工艺上有很大的区

别。如果按照编程工艺划分,可编程逻辑器件又可分为四个种类:

(1) 熔丝(Fuse)或反熔丝(Antifuse)编程器件。PROM 器件、Xilinx 公司的 XC5000 系列

器件和 Actel 的 FPGA 器件等采用这种编程工艺。

(2) U/EPROM 编程器件,即紫外线擦除/电可编程器件。大多数的 FPGA 和 CPLD 用这

种方式编程。

(3) E2PROM 编程器件,即电擦写编程器件。GAL 器件、ispLSI 器件用这种方法编程。

(4) SRAM 编程器件。Xilinx 公司的 FPGA 是这一类器件的代表。

2.2 可编程逻辑器件的基本结构

PLD 器件种类较多,不同厂商生产的 PLD 器件结构差别较大,不能够逐一介绍,本节

选择 PLD 器件中一些具有代表性的结构来说明其实现的主要逻辑功能。图 2-2 所示为 PLD

器件的基本结构框图,它由输入缓冲电路、与阵列、或阵列、输出缓冲电路等四部分组成

其中“与阵列”和“或阵列”是 PLD 器件的主体,逻辑函数靠它们实现;

输入缓冲电路主要用来对输入信号进行预处理,以适应各种输入情况;输出缓冲电路

主要用来对输出信号进行处理,用户可以根据需要选择各种灵活的输出方式(组合方式、时

序方式等)。我们知道,任何组合逻辑函数均可化为与或式,用“与门-或门”二级电路实现,

而任何时序电路又都是由组合电路加上存储元件(触发器)构成的,因而 PLD 的这种结构对

实现数字电路具有普遍的意义。

图 2-2 PLD 器件的基本结构框图

2.2.1 PLD 电路的表示方法及有关符号

可编程逻辑器件有一个相同的基本结构,其核心由与阵列和或阵列构成。由于阵列规

模一般远大于普通电路,用传统的器件符号已不能满足 PLD 原理图的需要,因此在 PLD

中,有关器件有其专门的表示方法。

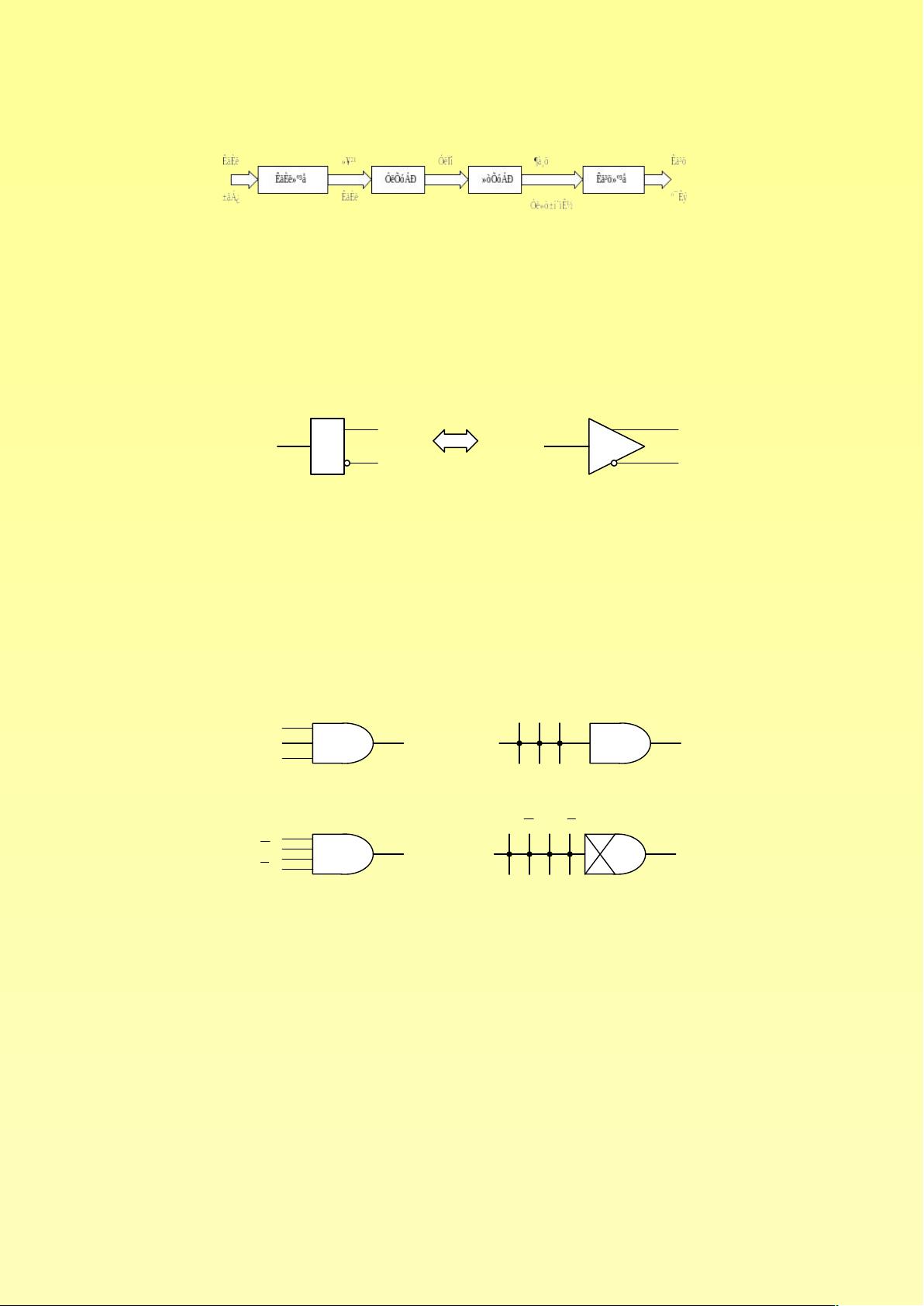

1.PLD 缓冲器表示法

为了使输入信号具有足够的驱动能力并产生原码和反码两个互补的信号, PLD 的输入

缓冲器和反馈缓冲器都采用互补的输出结构,如图 2-3 所示。图中 B=A,C=A。

1

A

B

C

A

B

C

(a) Ï°¹ß±íʾ·¨ (b) PLD±íʾ·¨

图 2-3 PLD 输入缓冲器电路

2.PLD 与门表示法

图 2-4(a)、(b)所示分别为一个四输入与门的习惯表示法和 PLD 表示法,图中

Y=A·B·C·D

若有逻辑表达式 Y=A·A·B·B,则显然此时 D 恒为电平“0”,PLD 对此有专门的简化表

示法,如图 2-4(c)、(d)所示。

A

B

C

Y

(a) Ï°¹ß±íʾ·¨

Y

A B C

(b) PLD±íʾ·¨

A

Y

(c) Ï°¹ß±íʾ·¨

A

B

B

Y

A

B

(d) ¼ò»¯PLD±íʾ·¨

A

B

图 2-4 与门表示法

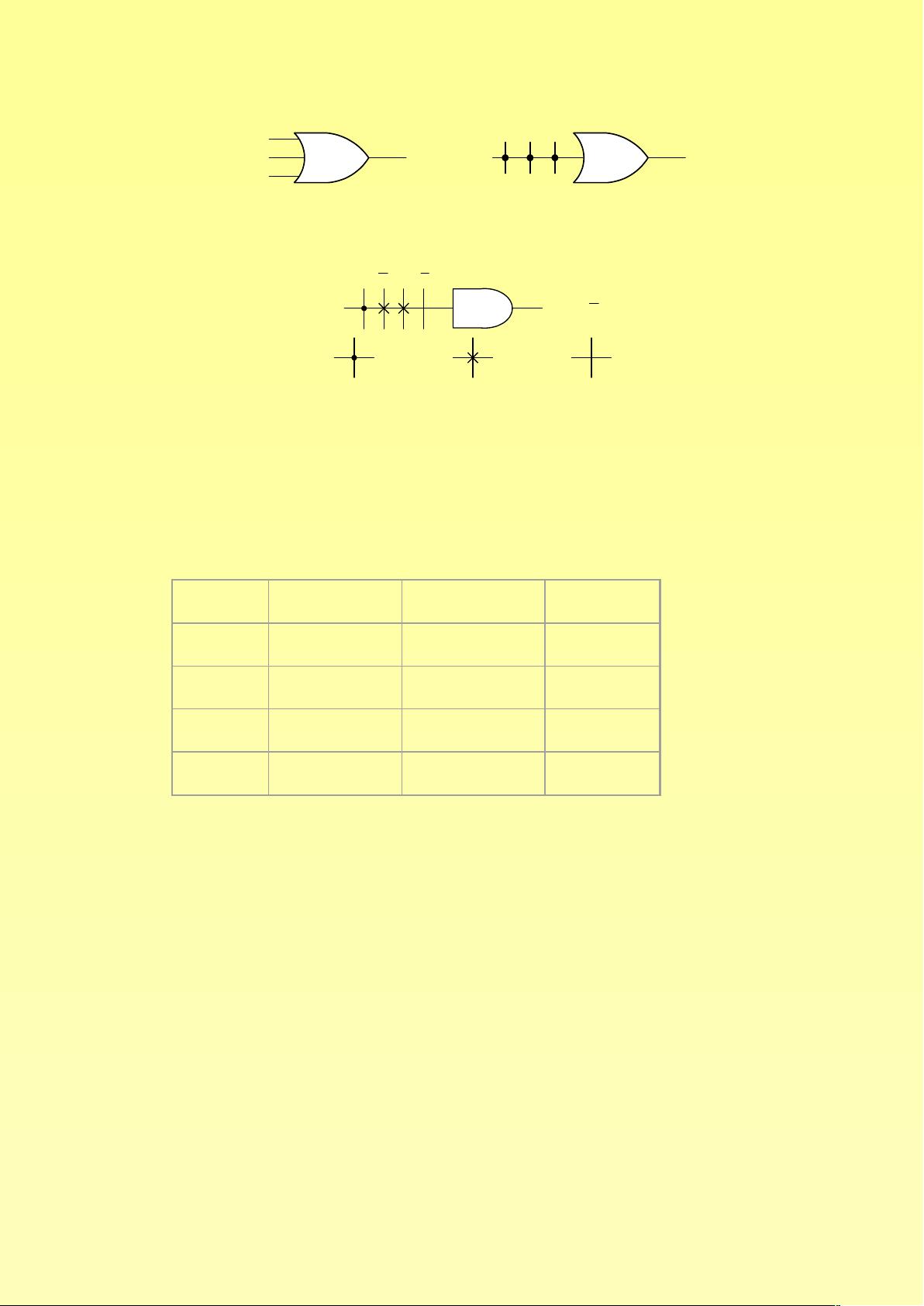

3.或门表示法

图 2-5 所示为一个三输入或门的习惯表示法和 PLD 表示法,图中 D=A+B+C。

4.PLD 连接的表示法

图 2-6 所示为 PLD 中阵列交叉点上三种连接方式的表示法。其中,交叉处为“· ”的表示

纵、横两线固定连接,不能通过“编程”手段使其断开;交叉处为“×”的表示该处为可编程连

接,即通过“编程”可使该处断开;交叉处无任何符号的表示纵、横不连接。

A

D

C

B

(a) Ï°¹ß±íʾ·¨

D

(b) PLD±íʾ·¨

A B C

图 2-5 或门表示法

A B

B

A

BAAD

(a) ¹Ì¶¨Á¬½Ó (b) ¿É±à³ÌÁ¬½Ó (c) ²»Á¬½Ó

图 2-6 PLD 连接表示法

2.2.2 与-或阵列

“与-或阵列”是 PLD 器件中最基本的结构,通过编程改变“与阵列”和“或阵列”的内部连

接,就可以实现不同的逻辑功能。依据可编程的部位可将 SPLD 器件分为可编程只读存储

器 PROM、可编程逻辑阵列 PLA、可编程阵列逻辑 PAL、通用阵列逻辑 GAL 等 4 种最基本

的类型,如表 2-1 所示。

表 2-1 4 种 SPLD 器件的区别

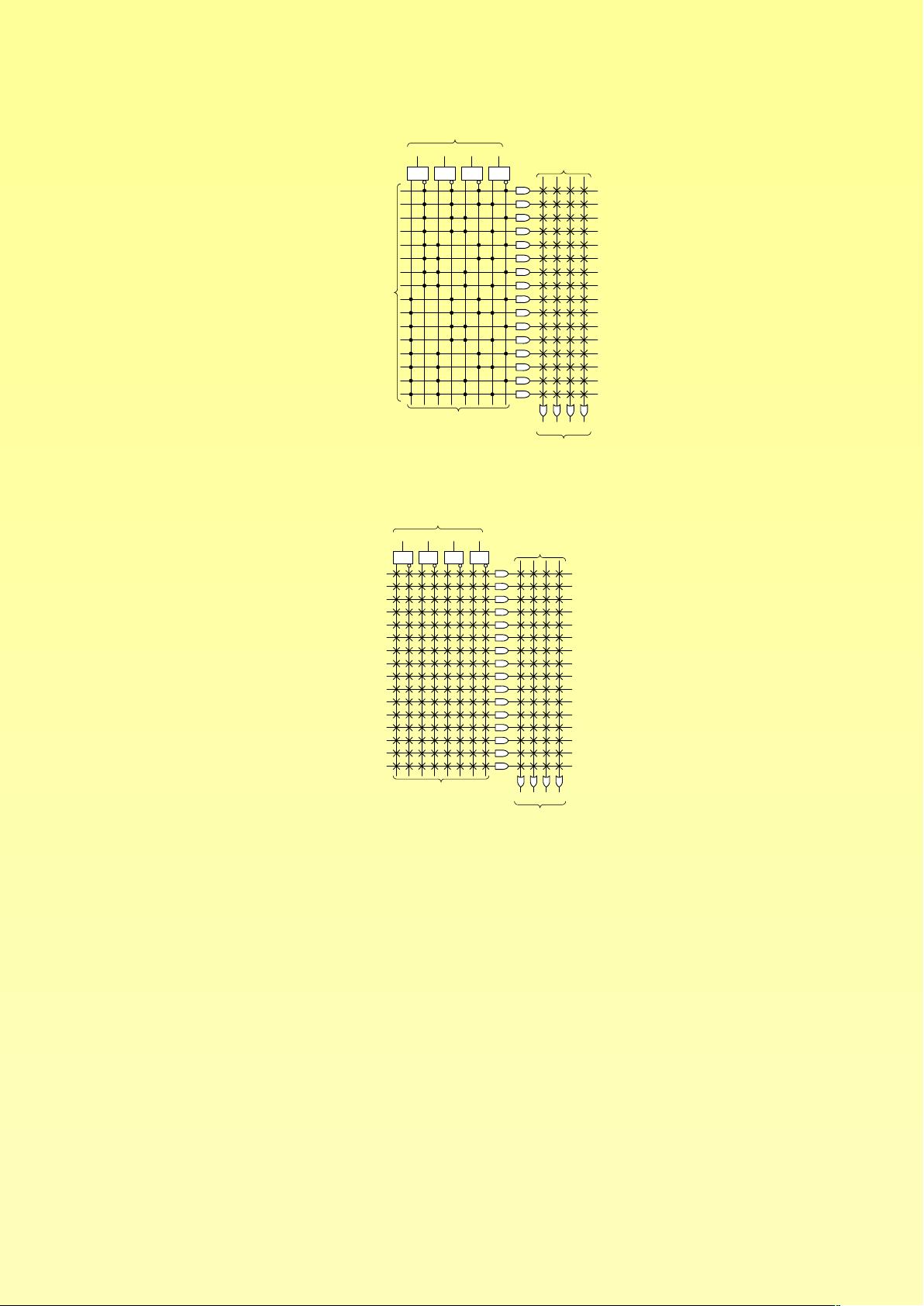

PROM 中包含一个固定连接的“与阵列”和一个可编程连接的“或阵列”,其示意图见图 2-

7。图中的 PROM 有 4 个输入端、16 个乘积项、4 个输出端。其中“· ”表示固定连接点,“×”

表示可编程连接点。PLA 中包含一个可编程连接的“与阵列”和一个可编程连接的“或阵列”,

如图 2-8 所示。

PAL 和 GAL 的基本门阵列部分的结构是相同的,即“与阵列”是可编程的,“或阵列”是

固定连接的。它们之间的差异除了表现在输出结构上,还表现在 PAL 器件只能编程一次,

而 GAL 器件则可以实现再次编程,这一点使得 GAL 器件更受用户的欢迎。

器件名 与阵列 或阵列 输出电路

PROM

固定 可编程 固定

PLA

可编程 可编程 固定

PAL

可编程 固定 固定

GAL

可编程 固定 可组态

1

1

1

1

I3 I2 I1 I0

nÊäÈë

¿É±à¡°»ò¡±¾ØÕó

O3 O2 O1 O0

mÊä³ö

¹Ì¶¨¡°Ó롱¾ØÕó

2

n

³Ë»ýÏß

图 2-7 PROM 示意图

1

1

1

1

I3 I2 I1 I0

4ÊäÈë

¿É±à¡°»ò¡±¾ØÕó

O3 O2 O1 O0

4Êä³ö

¿É±à¡°Ó롱¾ØÕó

图 2-8 PLA 示意图

2.2.3 宏单元

与或阵列在 PLD 器件中只能实现组合电路的功能,PLD 器件的时序电路功能则由包含

触发器或寄存器的逻辑宏单元实现,宏单元也是 PLD 器件中的一个重要的基本结构。

PLD 器件的主要生产商 Altera、Xilinx、Lattice 和 AMD 公司等在各自的 PLD 产品的宏

单元设计上有着各自的特点,总的来说,逻辑宏单元结构具有以下几个作用:

(1) 提供时序电路需要的寄存器或触发器。

(2) 提供多种形式的输入/输出方式。

(3) 提供内部信号反馈,控制输出逻辑极性。

(4) 分配控制信号,如寄存器的时钟和复位信号,三态门的输出使能信号。

2.3 可编程逻辑器件的基本资源

可编程逻辑器件可以由用户编程实现特定要求的功能,主要是由于其提供了四种可编

程资源,即位于芯片中央的可编程功能单元;位于芯片四周的可编程 I/O 引脚;分布在芯

片各处的可编程布线资源和片内存储块 RAM。本节以 FPGA 为例,对这些资源作概括介绍。

2.3.1 功能单元

可编程逻辑器件有以下三种基本的功能单元。

1.RAM 查找表

在 RAM 查找表结构中,RAM 存储器中需预先存入所要实现函数的真值表数值,输入

变量作为地址,用来从 RAM 存储器中选择相应的数值作为逻辑函数的输出值,这样就可

以实现输入变量的所有可能的逻辑函数。

2.基于多路开关的功能单元

采用基于多路开关的功能单元是基于如下的考虑:只要在多路开关的输入端放置输入

的变量、反变量、固定的 0 和 1 等相应的组合,两输入变量的所有函数就可以由单个 2 选 1

的多路开关来实现。

3.固定功能单元

固定功能单元提供单个固定的功能。单个固定功能有单级简单和延时短的优点,它的

主要缺点是要有大量的功能单元才能实现用户设计的逻辑,而且相应功能单元的级联和布

线的延时会导致整个器件性能的降低。

2.3.2 输入/输出引脚

由于可编程 ASIC 器件的功耗通常由所用的 I/O 引脚决定,所以当芯片有较多的 I/O 引

脚被利用时,必须考虑 I/O 配置的潜在功耗(瞬态和静态的)及 I/O 块的有效性,否则可编程

ASIC 芯片有可能因功耗问题被严重损坏。

随着半导体工艺的线宽不断缩小,从器件功耗的要求出发,器件的内芯必须采用低电

压。由于 I/O 块与内芯供电电压也可能不同,这就要求 I/O 块的结构能够兼容多个电压标准,

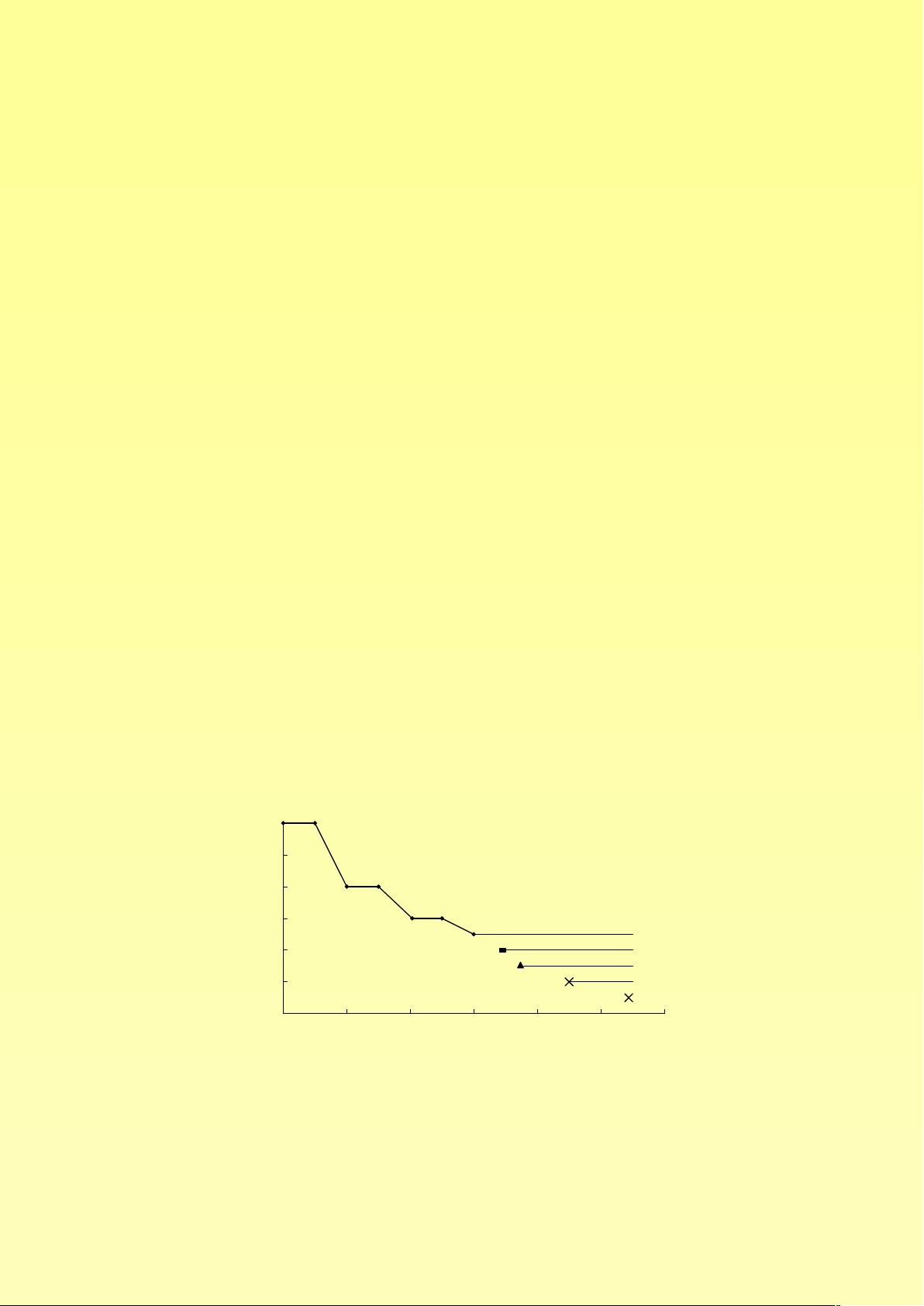

既能接收外部器件的高电压输入信号,又能驱动任何高电压的器件。ASIC 工艺线宽与供电

电压逐年改变情况如图 2-9 所示,一般来说,工艺线宽越小,对功耗的要求就越高,工作

电压就必须降低。

如工艺线宽为 1.2~0.5 μm 时,器件一般采用 5 V 电压供电;当工艺线宽为 0.35 μm 时,

器件的供电电压为 3.3 V,此时 I/O 块与内芯的供点电压相同;当工艺线宽为 0.25 μm 时,

I/O 块与芯片内芯的供电电压不再相同,内芯的供电电压为 2.5 V,I/O 块的供电电压为 3.3

V,并且能兼容 5 V 和 3.3 V 的器件;当工艺线宽为 0.18 μm 时,器件应采用 1.8 V 的供电

电压,I/O 块要能够兼容 2.5 V 和 3.3 V 的器件。

Size(

m)

0.6

0.8

1

1.2

0.4

0.2

0

1990 1992 1994 1996 1998 2000 2002

5 V

3.3 V

2.5 V

1.8 V

1.3 V

Year

图 2-9 ASIC 工艺线宽与供电电压逐年改变示意图

2.3.3 布线资源

布线资源是可编程逻辑器件中一种专用的内部互连结构,它主要用来提供高速可靠的

内部连线,以保证信号在芯片内部的相邻功能单元之间、功能单元与 I/O 块之间进行有效

的传输。可编程 ASIC 一般有以下几种基本的布线资源:

1.长线和直接连线

剩余32页未读,继续阅读

资源评论

leftgod110

- 粉丝: 5

- 资源: 22

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功