5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Table of Content

-1

Thurman UMA

A3

446Friday, May 25, 2007

<Variant Name>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Table of Content

-1

Thurman UMA

A3

446Friday, May 25, 2007

<Variant Name>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Table of Content

-1

Thurman UMA

A3

446Friday, May 25, 2007

<Variant Name>

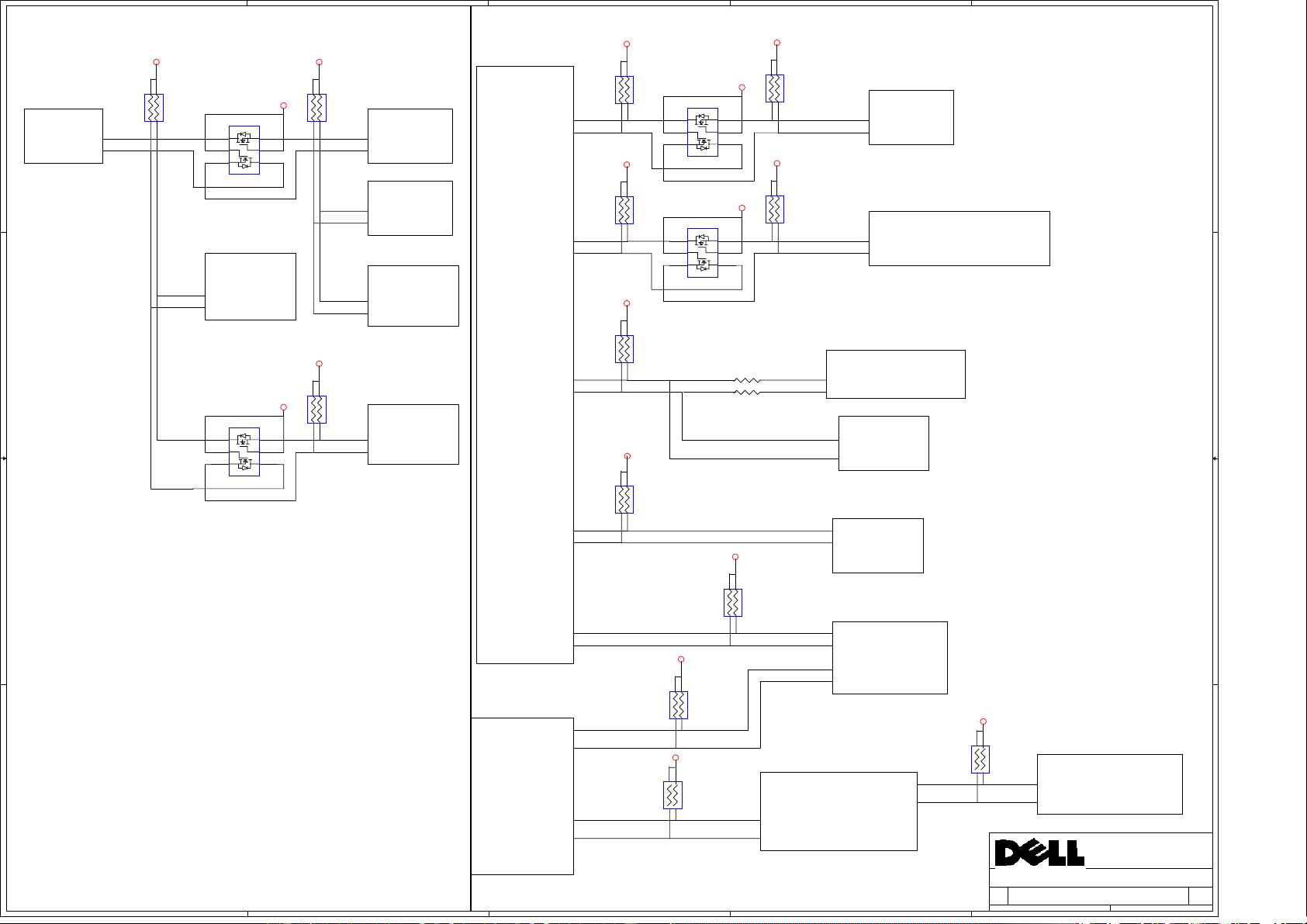

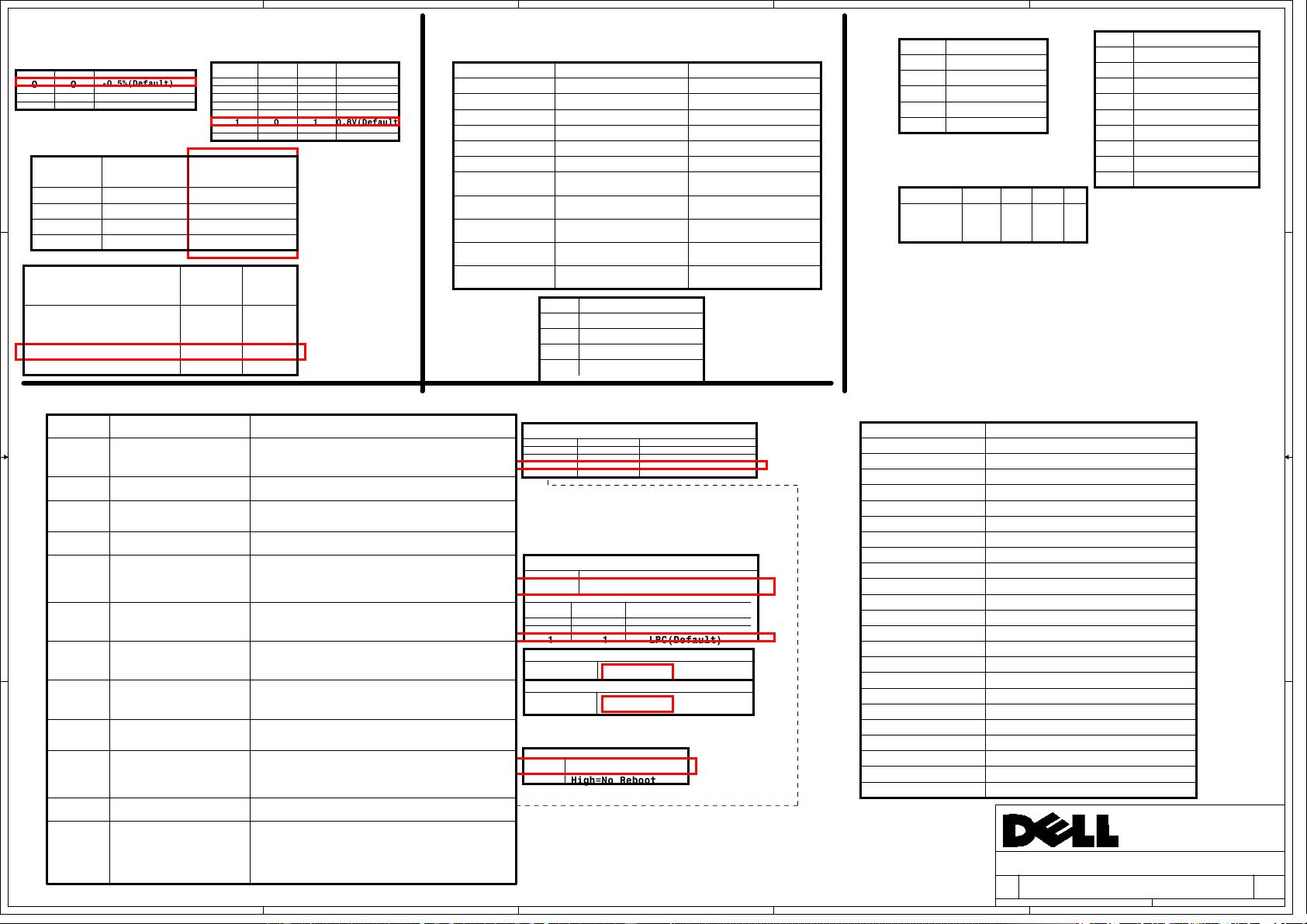

PCIE LAN REVERSAL.Rising

Edge of PWROK.

This signal has weak internal pull-up.

set bit27 of MPC.LR(Device28:Function0:Offset D8)

No Reboot.

Rising Edge of PWROK.

XOR Chain Entrance.

Rising Edge of PWROK.

This signal should not be pull low unless using

XOR Chain testing.

If sampled high, the system is strapped to the

"No Reboot" mode(ICH8M will disable the TCO Timer

system reboot feature). The status is readable

via the NO REBOOT bit.(Offset:3410h:bit5)

LANE3

LANE5

No use

No use

MiniCard WWAN

10/100 LOM

LANE4

LANE2

Internal Pull-Up.If sampled low,the Flash Descriptor

Security will be overidden.if high,the Security

measures defined in the Flash Descriptor will be in

effect.

This should only be used in manufacturing

environments

Express Card

LANE1

MiniCard WLAN

1 DISC.0 UMA

LANE6

PCI ROUTING

PIN44

DOT96T

LCD100/96T

PIN47

PCIE Routing USB TABLE

PIN43

PIN34

FCTSEL1

LCD100/96C

27M_NonSpread

27M_Spread

PIN48

SRCT_0

SEL1

FSB

SEL0

FSA

133M

SRCC_0

DOT96C

100M

166M

800M

01

X

0

1

X

667M

200M

01

CPU

SEL2

FSC

FSB

01

0

1

01

Sets bit2 of RPC.PC(Config Registers:Offset 224h)

Reserved

INT REQ GNTIDSEL

11C

D

AD171394/

MediaCard

LAN100_SLP

Integrated VccLAN1_05

VccCL1_05 VRM enable

/Disable. Always sampled.

Enables integrated VccLAN1_05,VccCL1_05 VRM

when sampled high

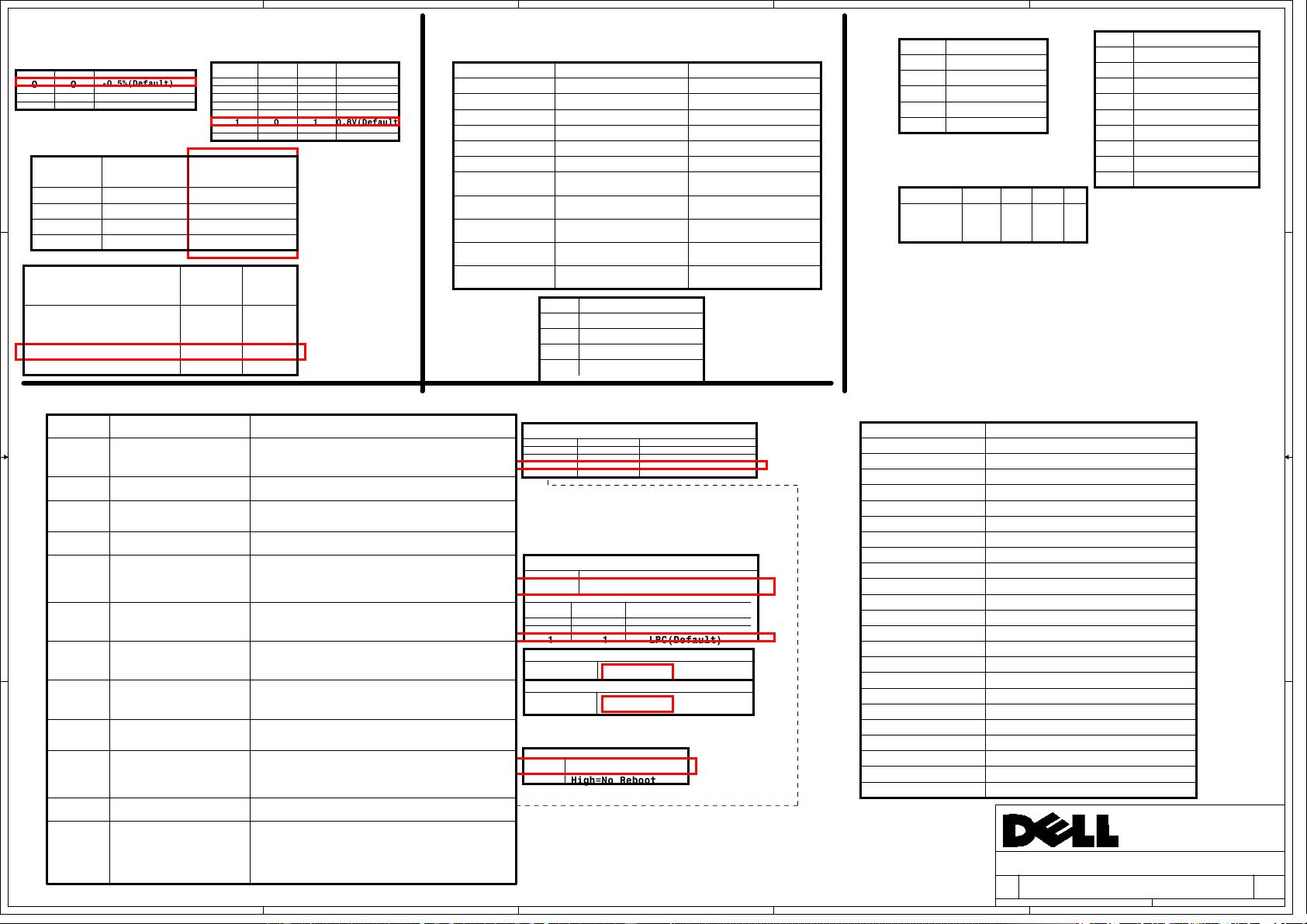

27M_SS/LCD96_100M SELECTION TABLE

Bit5 S1 Bit4 S0 Spread Spectrum S[1:0]

00

0

0

1

1

11

-0.5%(Default)

-1.0%

-1.5%

-2.0%

CLOCK GEN CY28547

No Reboot Strap

SPKR LOW = Defaule

High=No Reboot

XOR Chain Entrance Strap

ICH_RSVD

AZ_DOUT_ICH

0

1

0

0

01

11

Description

RSVD

Enter XOR Chain

Normal Operation(default)

Set PCIE port cofig bit1

01

11

A16 swap override strap

BOOT BIOS Strap

SPI_CS#1 BOOT BIOS LocationPCI_GNT#0

PCI_GNT#3 low = A16 swap override enable

high = default

0 1 SPI

LPC(Default)

PCI

INTEL ICH8-M STRAP PIN

BYTE 10

BYTE 15

IO_VOUT[2,1,0]

Bit2

IO_VOUT2

Bit1

IO_VOUT1

Bit0

IO_VOUT0

IO_VOUT[2,1,0]

0

00

0

0

0

0

0

0

0

0

0

1

11

1

11

1

1

1

1

1

1

0.3V

0.4V

0.5V

0.6V

0.7V

0.8V(Default)

0.9V

1.0V

tp3

DEFAULE HIGH

8.2K PULL HIGH

integrated VccSus1_05,VccSus1_5,VccCL1_5

integrated VccLan1_05VccCL1_05

SM_INTVRMEN

LAN100_SLP

High=Enable Low=Disable

High=Enable Low=Disable

GPIO33/

HDA_DOCK_EN#

Flash Descriptor Security

Override Strap

Rising Edge of PWROK.

USB3

USB7

USB4

USB5

USB6

USB0

USB1

USB2

USB8

USB9

ICH

INTEL ICH8-M INTEGRATED

PULL-UPS and PULL-DOWNS

SIGNAL Resistor Type/Value

HDA_BIT_CLK

HDA_RST#

HDA_SDIN[3:0]

HDA_SDOUT

HDA_SYNC

GNT[3:0]

GPIO[20]

LDA[3:0]#/FHW[3:0]#

LDRQ[0]

PME#

PWRBTN#

SATALED#

LAN_RXD[2:0]

LDRQ[1]/GPIO23

TP[3]

SPKR

SPI_CLK

SPI_CS1#

USB[9:0][P,N]

CL_RST#

SPI_MOSI

SPI_MISO

TACH_[3:0]

NONE

PULL-DOWN 20K

PULL-DOWN 15K

TBD

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-DOWN 20K

PULL-DOWN 20K

PULL-DOWN 20K

PULL-DOWN 20K

PULL-DOWN 20K

INTEL CRESTLINE STRAP PIN

PCIE Port Config 2 bit0,

Rising Edge of PWROK.

Weak Internal PULL-DOWN.NOTE:This signal should

not be pull HIGH.

INTVRMEN

SATALED#

SPKR

TP3

GNT2#

Sets bit0 of RPC.PC(Config Registers:Offset 224h)

Top-Block Swap Override.

Rising Edge of PWROK.

GNT0#

SPI_CS1#

Boot BIOS Destination

Selection.

Rising Edge of PWROK.

Controllable via Boot BIOS Destination bit

(Config Registers:Offset 3410h:bit 11:10).

GNT0# is MSB, 01-SPI, 10-PCI, 11-LPC.

HDA_SDOUT

HDA_SYNC

GNT3#

Signal

Sampled low:Top-Block Swap mode(inverts A16 for all

cycles targeting FWH BIOS space).

Note: Software will not be able to clear the

Top-Swap bit until the system is rebooted

without GNT3# being pulled down.

XOR Chain Entrance/

PCIE Port Config 1 bit1,

Rising Edge of PWROK

Allows entrance to XOR Chain testing when TP3

pulled low at rising edge of PWROK.When TP3 not

pulled low at rising edge of PWROK,sets bit1 of

RPC.PC(Config Registers:offset 224h)

PCIE Port Config 1 bit0,

Rising Edge of PWROK.

GPIO20

Usage/When Sampled Comment

Integrated VccSus1_05

VccSus1_5 and VccCL1_5

VRM Enable/Disable.Always

sampled.

Enables integrated VccSus1_05,VccSus1_5 and

VccCL1_5 VRM when sampled high

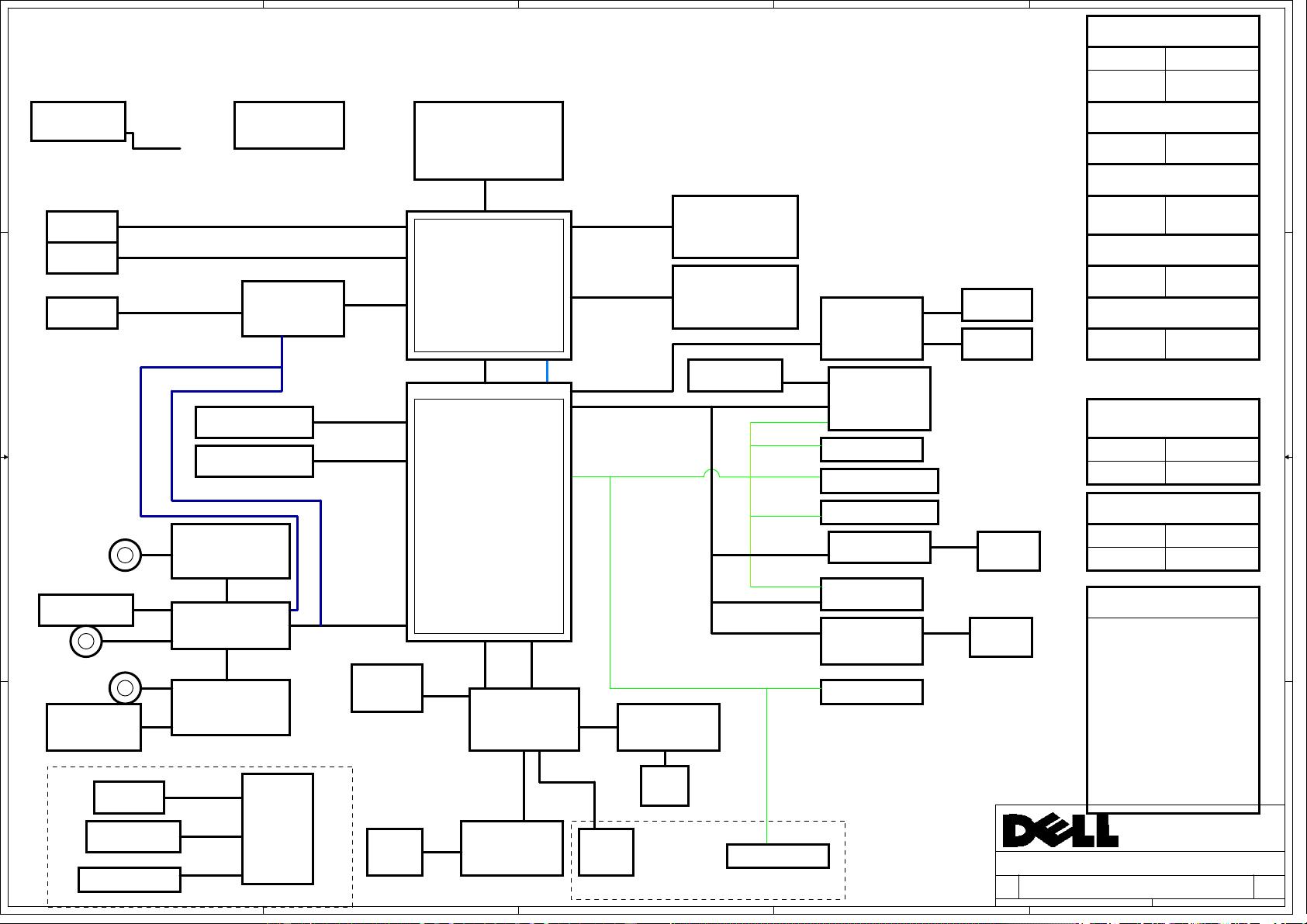

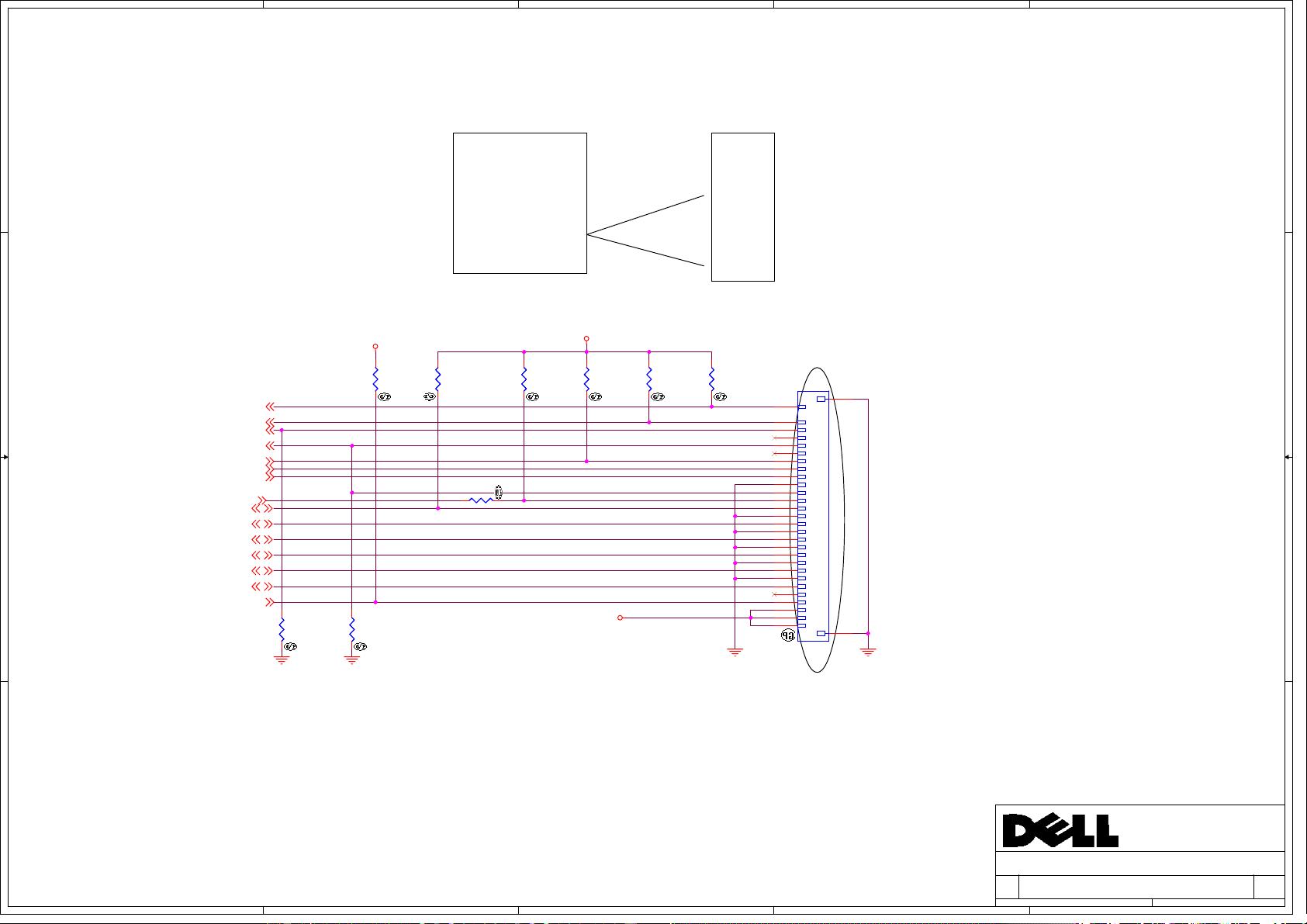

Mobile CPU

*

*

CFG 16

*

FSB Dynamic ODT

*

CFG Strap

Disabled

High

*

Low

Enabled

*

DMI X 2

CFG 18

VCC Select

*

*

*

*

*

*

CFG 9

1.05V

Reserved Lane

1.5V

is Default setting

Normal Operation

CFG 19

DMI Lane Reserved

DMI X 4

Normal Operation

CFG 10

Reserved Lane

Reserved

PCIE/SDVO Select

Moby Dick

Only PCIE or SDVO

is operation

Calistoga

Mobility

CFG 20 PCIE and SDVO

are operation simu

CFG 11

Reserved

SDVO_CTRLDATA

CFG 5

CFG 6

No SDVO Device

present

CFG 7

Calistoga

DT/Transportable CPU

SDVO Device present

LL

LH

HL

HH

*

CFG[13:12]

Reserved

XOR Mode Enabled

All Z Mode Enabled

Normal Operation

USB2

USB1

Camera

Express Card

BT

Biometric

MINI Card WWAN

cwzqhdx2012-07-11资料可以使用。

cwzqhdx2012-07-11资料可以使用。 我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功