PCI BIOS SPECIFICATION

Revision 2.1

August 26, 1994

ii PCI BIOS Specification Revision 2.1

Copyright PCI Special Interest Group

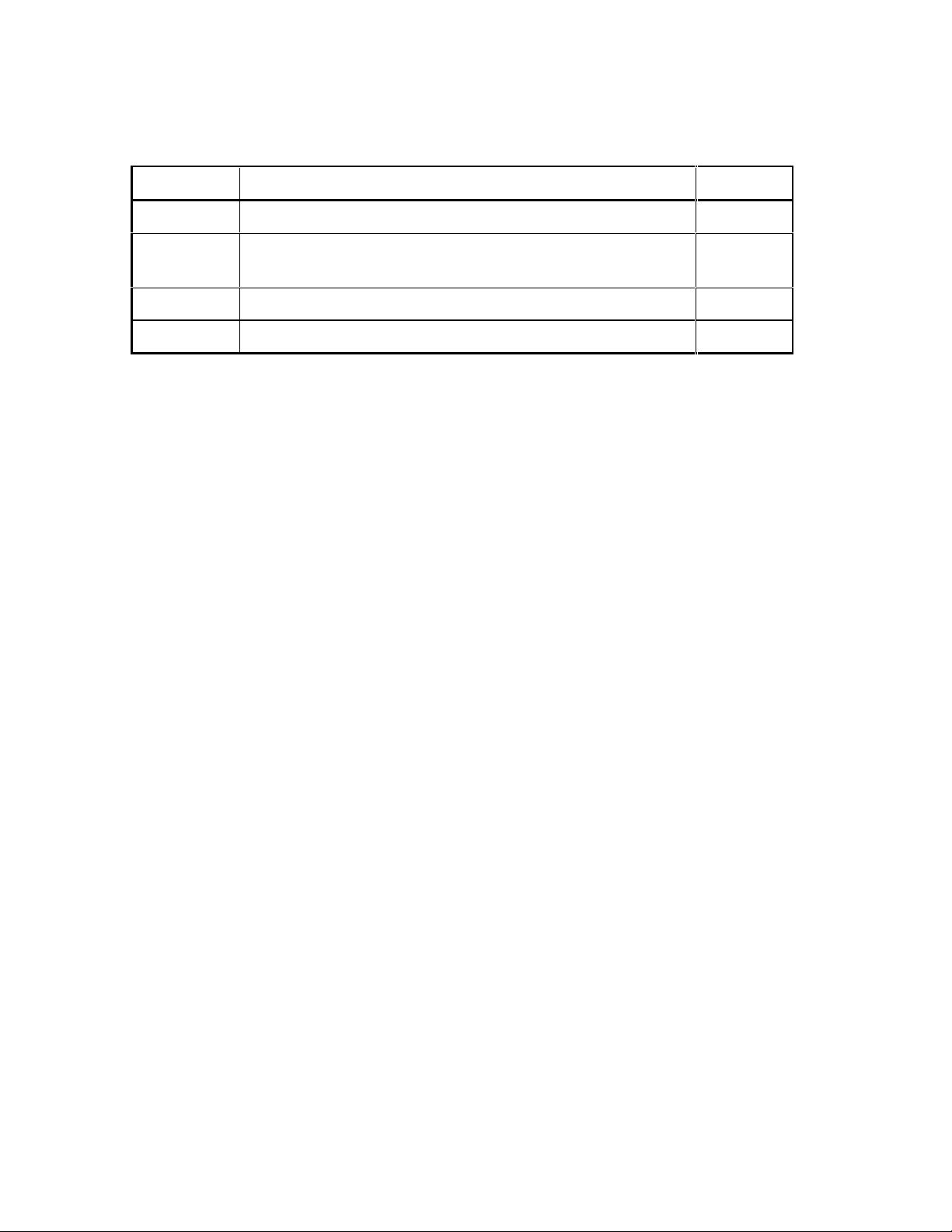

REVISION REVISION HISTORY DATE

1.0 Original issue distributed by Intel 9/28/92

2.0 Updated to be in synch with PCI Bus Specification Rev

2.0

7/20/93

2.1 Added functions for PCI IRQ routing; Clarifications. 8/26/94

The PCI Special Interest Group disclaims all warranties and liability for the use of this

document and the information contained herein and assumes no responsibility for any

errors that may appear in this document, nor does the PCI Special Interest Group make a

commitment to update the information contained herein.

Contact the PCI Special Interest Group office to obtain the latest revision of the

specification.

Questions regarding the PCI BIOS specification or membership in the PCI Special

Interest Group may be forwarded to:

PCI Special Interest Group

2575 NE Kathryn St #17

Hillsboro, OR 97124

(800) 433-5177 - Domestic

(503) 693-6232 - International

(503) 693-8344 - Fax

techsupp@pcisig.com

Revision 2.1 PCI BIOS Specification iii

Copyright PCI Special Interest Group

TABLE OF CONTENTS

1. Introduction ...............................................................................................................1

1.1. Purpose.......................................................................................................1

1.2. Scope..........................................................................................................1

1.3. Related Documents.....................................................................................1

1.4. Terms and Abbreviations ........................................................................... 1

2. Functional Description .............................................................................................. 2

3. Assumptions and Constraints....................................................................................3

3.1. ROM BIOS Location..................................................................................3

3.2. Calling Conventions...................................................................................3

3.3. BIOS32 Service Directory..........................................................................4

3.3.1. Determining the existence of BIOS32 Service Directory............4

3.3.2. Calling Interface for BIOS32 Service Directory .........................5

3.4. PCI BIOS 32-bit service.............................................................................6

4. Host Interface ............................................................................................................ 7

4.1. Identifying PCI Resources..........................................................................7

4.1.1. PCI BIOS Present........................................................................7

4.1.2. Find PCI Device..........................................................................9

4.1.3. Find PCI Class Code ................................................................... 10

4.2. PCI Support Functions ............................................................................... 11

4.2.1. Generate Special Cycle................................................................ 11

4.2.2. Get PCI Interrupt Routing Options.............................................. 12

4.2.3. Set PCI Hardware Interrupt.........................................................15

4.3. Accessing Configuration Space..................................................................17

4.3.1. Read Configuration Byte.............................................................17

4.3.2. Read Configuration Word ........................................................... 18

4.3.3. Read Configuration Dword ......................................................... 19

4.3.4. Write Configuration Byte............................................................20

4.3.5. Write Configuration Word ..........................................................21

4.3.6. Write Configuration Dword ........................................................22

APPENDIX A: Function List.........................................................................................23

APPENDIX B: Return Code List...................................................................................24

Revision 2.1 PCI BIOS Specification 1

Copyright PCI Special Interest Group

1. Introduction

1.1. Purpose

This document describes the software interface presented by the PCI BIOS functions.

This interface provides a hardware independent method of managing PCI devices in a

host computer.

1.2. Scope

This document is intended to provide enough information to software developers to

utilize PCI devices in a host computer without any knowledge of how the actual hardware

performs the desired functions. It is also intended to provide enough information for an

implementor to create these BIOS functions for a particular system design.

1.3. Related Documents

PCI Local Bus Specification, Revision 2.0 April 30, 1993

Standard BIOS 32-bit Service Directory Proposal, Revision 0.4 May 24, 1993

(available from Phoenix Technologies Ltd., Norwood, MA)

1.4. Terms and Abbreviations

Bus Number A number in the range 0 .. 255 that uniquely selects a PCI

bus.

Configuration Space A separate address space on PCI buses. Used for device

identification and configuring devices into Memory and IO

spaces.

Device ID A predefined field in configuration space that (along with

Vendor ID) uniquely identifies the device.

Device Number A number in the range 0..31 that uniquely selects a device

on a PCI bus.

Function Number A number in the range 0..7 that uniquely selects a function

within a multi-function PCI device.

Multi-function PCI

device

A PCI device that contains multiple functions. For instance,

a single device that provides both LAN and SCSI functions,

and has a separate configuration space for each function is a

multi-function device.

PCI Acronym for Peripheral Component Interconnect bus.

Special Cycle A specific PCI bus command used for broadcasting to all

PCI devices on a bus.

Vendor ID A predefined field in configuration space that (along with

Device ID) uniquely identifies the device.