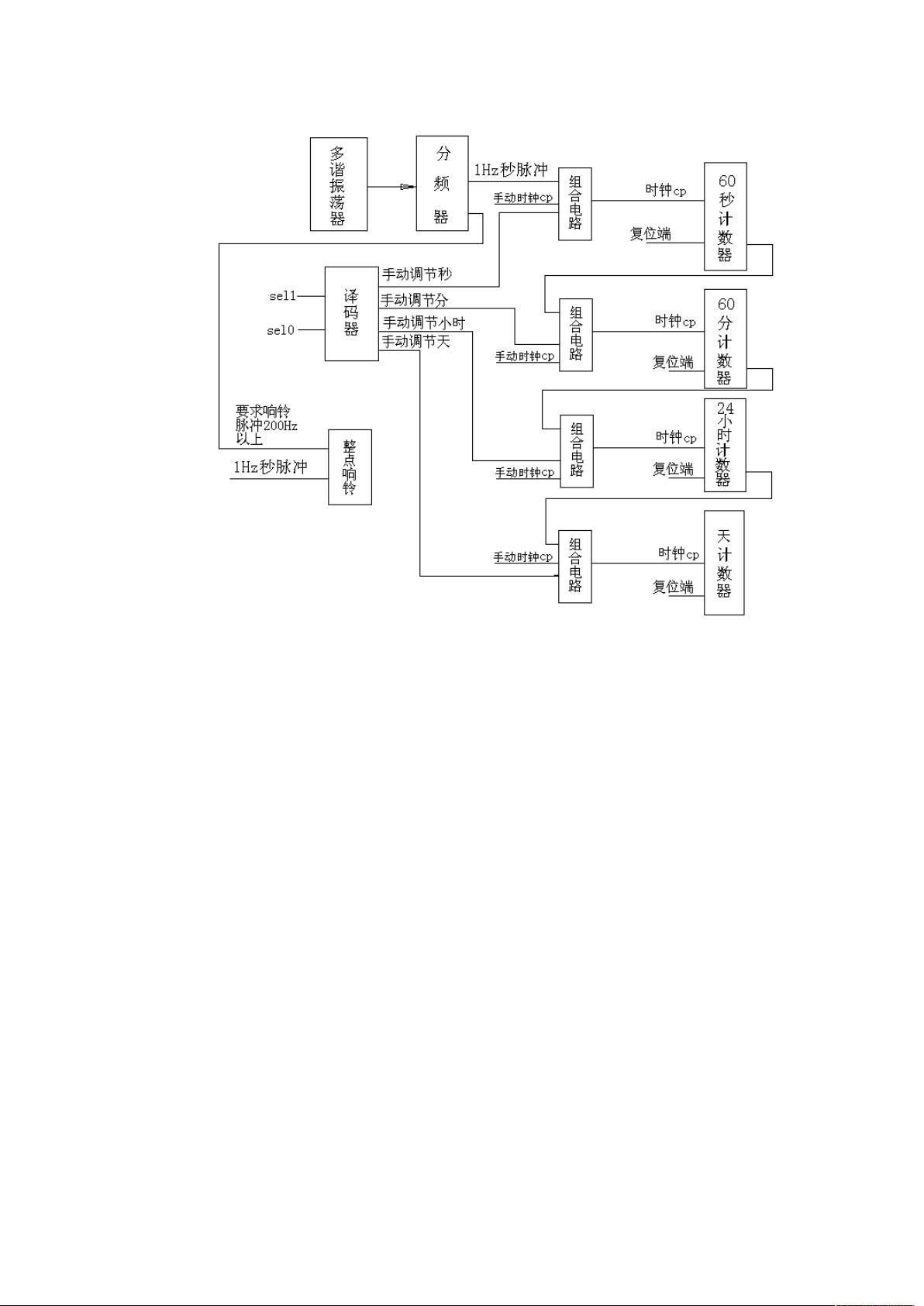

【课程设计:多功能倒计时牌】 数字电子电路课程设计的目标是实现一个多功能倒计时牌,通过ISP软件仿真来加深对数字电路的理解。倒计时牌作为一种实用的计时工具,广泛应用于生活和工作中,它由数字电路技术构建,包括组合逻辑电路和时序电路,具备更高的精确度和持久的使用寿命。 设计指标要求使用ispLSI1032E芯片实现倒计时功能。倒计时牌应具备以下特性: 1. 显示天、时、分、秒,使用六个数码管和四个发光二极管。 2. 可以复位倒计时。 3. 可以启动或停止倒计时。 4. 停止状态下可修改计时值。 5. 设有报时功能,整点时通过喇叭鸣叫六秒。 6. 必须保证分频器输出的是秒脉冲。 设计中,数字钟的构成基于一个标准的1Hz频率计数电路,通常采用石英晶体振荡器保证时间信号的准确稳定。整体设计包含一个顶层模块和多个底层模块,顶层模块`clock`通过原理图实现,包括计数器、整点报时模块、译码器等组件。底层模块如`clk-ring`用于分频,产生1Hz脉冲,`cnt60`、`cnt24`、`cnt30`作为秒、分、时计数器,`encode24`为2-4译码器,用于选择预置数的计数器,`ring`模块则负责整点报时。 在设计思想上,各模块通过控制信号实现暂停和置数功能,比如计数器的进位信号复位端取自自身,以确保高电平脉冲宽度尽可能窄。555定时器被用于设计多谐振荡器,产生1000Hz的时钟信号。此外,设计中还涉及多种元器件,如七段数码管、555定时器、集成块、电阻、电位器、电容、蜂鸣器、2-4译码器、JK触发器和门器件。 底层模块`clk-ring`的ABEL语言源文件用于描述其具体逻辑操作,这部分代码是实现分频和整点报时功能的关键。每个模块的设计都需要考虑逻辑门的组合和时序逻辑的实现,以确保整个系统的正确运行。 通过这个课程设计,学生将深入理解数字电路的基本原理,熟悉中小规模集成电路的应用,以及如何利用它们来构建复杂的数字系统。同时,也会掌握如何使用ISP软件进行电路仿真,提高问题解决和实践操作能力。这不仅是理论知识的验证,更是动手能力和工程素养的培养。

剩余13页未读,继续阅读

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- HTML-CSS-JS学习-01百度登录界面练习.zip

- 毕业设计:基于SpringBoot的网上订餐系统,前后端分离,含支付功能-1.zip

- selective-scan-cuda.cp310-win-amd64.pyd

- 计算机二级 NCRE2 Python 练习题 .zip

- 基于springboot+vue的物业管理系统,采用前后端分离模式实现.zip

- springboot教学资源库(代码+数据库+LW)

- java课程设计作业:基于Java的打地鼠小游戏.zip

- causal-conv1d-cuda.cp310-win-amd64.pyd

- 全国计算机等级考试二级python的学习笔记(适用2020年).zip

- 机器学习(大模型):GPT大型语言模型辅助训练数据集

信息提交成功

信息提交成功