没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

PSoC

®

3: CY8C38 Family

Data Sheet

Programmable System-on-Chip (PSoC

®

)

Cypress Semiconductor Corporation • 198 Champion Court • San Jose, CA 95134-1709 • 408-943-2600

Document Number: 001-63724 Rev. *A 修订时间: 4 2, 2012

9 概述

凭借其独特的可配置模块阵列,PSoC

®

成为一个真正的系统级解

决方案,可在单个芯片中提供微控制器单元 (MCU)、存储器、模

拟和数字外设功能。 CY8C38 系列提供了一种新型的信号采集、

信号处理和控制方法,并具有高精度、高带宽和高灵活性等特

点。 其模拟功能涵盖了从热电偶信号(接近直流电压)到超声波

信号的广泛信号范围。 CY8C38 系列可以处理数十个数据采集通

道以及每个通用输入 / 输出 (GPIO) 引脚上的模拟输入。 CY8C38

系列还是一个高性能的可配置数字系统,部分器件具有 USB、

(I

2

C) 以及控制器区域网络 (CAN) 等接口。 除了通信接口之外,

CY8C38 系列还具有易于配置的逻辑阵列,至所有 I/O 引脚的灵

活路由,以及高性能的单周期 8051 微处理器内核。 借助 PSoC

Creator ™ 这一基于层级的原理图设计输入工具,您可使用丰富

的预建组件和布尔基元库来轻松创建系统级设计。 使用 CY8C38

系列不仅可以实现模拟和数字材料表的集成,而且只需通过简单

的固件更新,即可轻松纳入最新的设计变更。

特性

单周期 8051 CPU

工作频率介于 DC 至 67 MHz 之间

乘法和除法指令

上至 64KB 闪存程序存储器,100,000 次写循环,20 年保留

时间和多种安全功能

最高可达 8 KB 的纠错码 (ECC) 或配置闪存

最高可达 8 KB 的 SRAM

最高可达 2 KB 可电擦除可编程只读存储器 (EEPROM),

1 百万 次写循环以及 20 年保留时间

24 通道直接存储器访问 (DMA),多层 AHB

[1]

总线访问

• 可编程链式描述符和优先级

• 支持高带宽 32 位传输

低电压、超低功耗

宽广的工作电压范围: 0.5 V 到 5.5 V

高效升压调节器 (输入 0.5V,输出 1.8V-5.0V)

在 3 MHz 下为 0.8 mA,在 6 MHz 下为 1.2 mA,在 48 MHz

下为 6.6 mA

低功耗模式包括:

• 1 µA 睡眠模式,提供实时时钟和欠压检测 (LVD) 中断

• 200 nA 休眠模式,RAM 保留数据

多功能 I/O 系统

28 至 72 个 I/O(62 个 GPIO,八个特别输入 / 输出 (SIO),

两个 USBIO

[2]

)

可从任意 GPIO 路由至任意数字或模拟外设

LCD 驱动从任何 GPIO,上至 46 × 16 段

[2]

任何 GPIO 均支持 CapSense®

[3]

1.2V 至 5.5V I/O 接口电压,多达 4 个电压域

任何引脚或端口都可设置成可接受独立的可屏蔽 IRQ

施密特触发器晶体管 - 晶体管逻辑 (TTL) 输入

集电极开路模式 高电平 / 低电平

在上电复位 (POR) 时可配置 GPIO 引脚的状态

SIO 具有 25 mA 的灌电流能力

数字外设

20 至 24 个基于可编程逻辑器件 (PLD) 的通用数字模块

(UDB)

Full CAN 2.0b RX 缓冲区(16 个)和 TX 缓冲区(8 个)

[2]

全速 (FS) USB 2.0 12 Mbps (采用内部振荡器)

[2]

多达 4 个 16 位可配置定时器、计数器和 PWM 模块

实现 FIR 和 IIR 滤波器

标准外设库

• 8、16、24 和 32 位定时器、计数器和 PWM

• SPI, UART、I

2

C

• 目录中列出的许多其他外设

高级外设库

• 循环冗余校验 (Cyclic Redundancy Check, CRC)

• 伪随机序列 (Pseudo Random Sequence, PRS) 发生器

• 本地互连网络 (LIN) 总线 2.0

• 正交解码器

模拟外设 (1.71 V VDDA 5.5 V)

-40 °C 至 +85 °C 时内部电压参考为 1.024 V ± 0.1%

具有 8 至 20 位分辨率的可配置 Delta-Sigma ADC

• 采样率最高可达 192 ksps

• 可编程增益级: ×0.25 到 ×16

• 12 位模式,192-ksps,66-dB 信噪比和失真比

(SINAD),±1 位 INL/DNL

• 16 位模式,48 ksps,84-dB SNR,±2 位 INL,±1 位 DNL

最多四个 8 位、8-Msps IDAC 或 1-Msps VDAC

四个响应时间为 95 ns 的电压比较器

最多四个驱动能力为 25 mA 的未赋定 (uncommitted)运算

放大器

最多四个可配置的多功能模拟模块。 配置示例包括可编程增

益放大器 (PGA)、互阻放大器 (TIA)、混频器,以及采样和

保持

CapSense 支持

编程、调试和跟踪

JTAG (4 线)接口,串行线调试 (SWD) (2 线)接口,以及

单线浏览器 (SWV) 接口

八个地址断点和一个数据断点

4 KB 的指令跟踪缓冲区

支持通过 I

2

C、SPI、UART、USB 以及其他接口进行

bootloader 编程

高精度的可编程时钟

涵盖整个温度和电压范围的 3 至 62 MHz 内部振荡器

4 至 25 MHz 晶振,能够实现晶振 PPM 精度

能够生成高达 67 MHz 的内部 PLL 时钟

32.768 kHz 监视晶振

频率为 1 kHz、33 kHz 和 100 kHz 的低功耗内部振荡器

温度和包装

-40 °C 至 +85 °C 工业级温度

48 引脚 SSOP、48 引脚 QFN、68 引脚 QFN 以及 100 引脚

TQFP 封装可供选择

注

1. AHB – AMBA (高级微控制器总线架构)高性能总线,是 ARM 数据传输总线

2. 此特性仅在某些器件上提供。 有关详细信息,请参见订购信息第 120 页的。

3. 建议不要将带运算放大器输出的 GPIO 同 CapSense 一起使用。

PSoC

®

3: CY8C38 Family

Data Sheet

Document Number: 001-63724 Rev. *A 页码:2/ 130

目录

1. 架构概述 ............................... 3

2. 引脚分布 ............................... 5

3. 引脚说明 .............................. 10

4. CPU ................................... 11

4.1 8051 CPU .......................... 11

4.2 寻址模式 .......................... 11

4.3 指令集 ............................11

4.4 DMA 与 PHUB ....................... 15

4.5 中断控制器 ........................ 17

5. 存储器 ................................ 21

5.1 静态 RAM ..........................21

5.2 闪存程序存储器 .................... 21

5.3 闪存安全性 ........................ 21

5.4 EEPROM ............................ 21

5.5 非易失性锁存器 (NVL) .............. 22

5.6 外部存储器接口 .................... 23

5.7 存储器映射 ........................ 24

6. 系统集成 .............................. 26

6.1 时钟系统 .......................... 26

6.2 供电系统 .......................... 29

6.3 复位 ..............................32

6.4 I/O 系统与路由 .................... 33

7. 数字子系统 ............................ 40

7.1 外设示例 .......................... 40

7.2 通用数字模块 ...................... 43

7.3 UDB 阵列说明 ...................... 47

7.4 DSI 路由接口说明 .................. 47

7.5 CAN ............................... 49

7.6 USB ............................... 51

7.7 定时器、计数器和 PWM .............. 51

7.8 I

2

C ............................... 52

7.9 数字滤波器模块 .................... 53

8. 模拟子系统 ............................ 53

8.1 模拟路由 .......................... 54

8.2 Delta-sigma ADC ................... 56

8.3 电压比较器 ........................ 57

8.4 运算放大器 ........................ 59

8.5 可编程 SC/CT 模块 ................. 59

8.6 LCD 直接驱动 ...................... 60

8.7 CapSense .......................... 61

8.8 温度传感器 ........................ 61

8.9 DAC ............................... 61

8.10 上变频 / 下变频混频器 ............ 62

8.11 采样和保持 ...................... 62

9. 编程、调试接口与资源 .................. 63

9.1 JTAG 接口 ......................... 63

9.2 串行线调试接口 .................... 65

9.3 调试功能 .......................... 66

9.4 跟踪功能 .......................... 66

9.5 单线浏览器接口 .................... 66

9.6 编程功能 .......................... 66

9.7 器件安全性 ........................ 66

10. 开发支持 ............................. 67

10.1 文档 ............................ 67

10.2 在线资源 ........................ 67

10.3 工具 ............................ 67

11. 电气规范 ............................. 68

11.1 绝对最大额定值 .................. 68

11.2 器件级规范 ...................... 69

11.3 电源调节器 ...................... 73

11.4 输入和输出 ...................... 77

11.5 模拟外设 ........................ 84

11.6 数字外设 ........................ 103

11.7 存储器 .......................... 107

11.8 PSoC 系统资源 ................... 113

11.9 时钟 ............................ 116

12. 订购信息 ............................ 120

12.1 部件编号约定 .................... 121

13. 封装 ................................ 122

14. 缩略语 .............................. 126

15. 参考文档 ............................ 127

16. 文档规范 ............................ 127

16.1 测量单位 ........................ 127

17. 修订记录 ............................ 129

18. 销售、解决方案和法律信息 ............ 130

PSoC

®

3: CY8C38 Family

Data Sheet

Document Number: 001-63724 Rev. *A 页码:3/ 130

1. 架构概述

CY8C38 系列的超低功耗闪存可编程片上系统 (PSoC

®

) 器件是可扩放的 8 位 PSoC 3 和 32 位 PSoC

5 平台的一部分。 CY8C38 系列

围绕 CPU 子系统提供了多个可配置的模拟、数字和互连电路模块。 通过将 CPU 同高度灵活的模拟子系统、数字子系统、路由及 I/O

相结合,可以在众多消费、工业和医学应用领域实现高度集成。

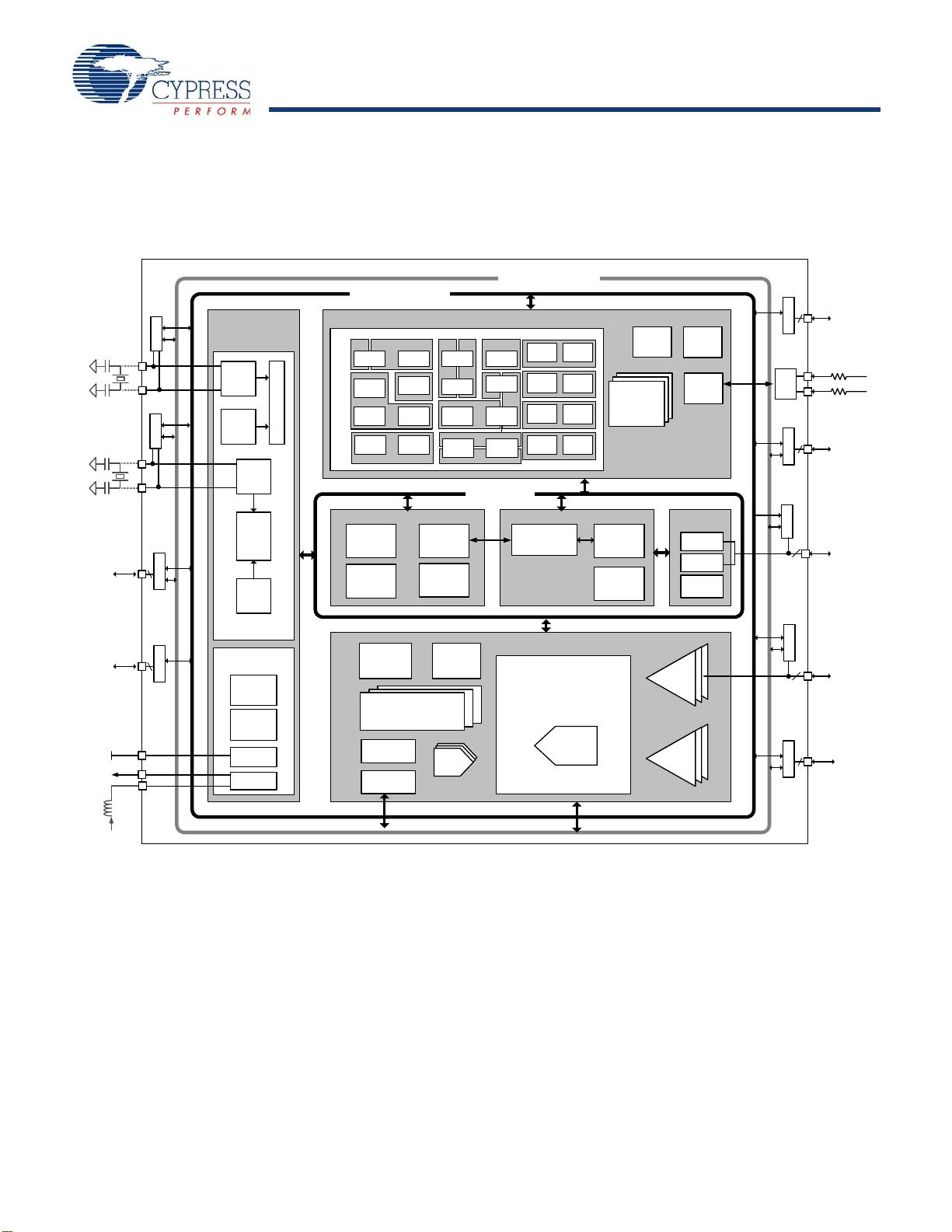

图 1-1. 简化的框图

图 1-1 显示了 CY8C38 系列的主要组件。 其中包括:

8051 CPU 子系统

非易失性子系统

编程、调试和测试子系统

输入和输出

时钟

功耗

数字子系统

模拟子系统

PSoC 具有独特的可配置性,其中有一半是由其数字子系统提供

的。 数字子系统不仅能够通过数字系统互连 (Digital System

Interconnect, DSI) 将来自任意外设的数字信号连接至任意引

脚, 而且还能够通过小而快的低功耗 UDB 实现功能灵活性。

PSoC Creator 提供了一个外设库,其中包括经过测试并已映射至

UDB 阵列的标准预建数字外设,如 UART、SPI、LIN、PRS、CRC、

定时器、计数器、PWM、AND、OR 等。 此外,您还可以通过图形

设计输入的方式,使用布尔基元轻松创建数字电路。 每个 UDB

均包含可编程阵列逻辑 (PAL)/ 可编程逻辑器件 (PLD) 功能,以

及支持众多外设的小型状态机引擎。

除了能够提高 UDB 阵列的灵活性之外,PSoC 还提供旨在实现特

定功能的可配置数字模块。 对于 CY8C38 系列,这些模块包括四

个 16 位定时器、计数器和 PWM 模块; I

2

C 从器件、主控和多

主控;全速 USB ;以及 Full CAN 2.0b。

Digital

Filter

Block

Analog System

LCD Direct

Drive

CapSense

Temperature

Sensor

4 x

Opamp

+

-

ADC

4 x DAC

1 x

Del Sig

ADC

4 x SC/CT Blocks

(TIA, PGA, Mixer etc)

4 x

CMP

+

-

CAN

2.0

I

2

C

Master/

Slave

Universal Digital Block Array (24 x UDB)

4 x

Timer

Counter

PWM

FS USB

2.0

System Wide

Resources

Digital System

Program

Debug

&

Trace

Boundary

Scan

Program

&

Debug

8051 or

Cortex M3 CPU

Interrupt

Controller

PHUB

DMA

SRAM

FLASH

EEPROM

EMIF

CPU SystemMemory System

System Bus

Digital Interconnect

Analog Interconnect

1.71 to

5.5 V

0.5 to 5.5 V

( Optional)

425MHz

(Optional)

Xtal

Osc

32.768 KHz

( Optional)

RTC

Timer

IMO

Clock Tree

WDT

and

Wake

ILO

Clocking System

1.8V LDO

SMP

POR and

LVD

Sleep

Power

Power Management

System

USB

PHY

3 per

Opamp

GPIOs

GPIOs

GPIOs

GPIOs

GPIOs

GPIOsSIO

GPIOsSIOs

UDB

UDB

UDB

UDB

UDB

UDB

UDB UDB UDB

UDB

UDB

UDBUDB

UDB UDB

UART

Logic

12-bit PWM

I

2

C Slave

8-bit SPI

12-bit SPI

Logic

8-bit

Timer

16-bit PRS

UDB

8-bit

Timer

Quadrature Decoder

16-bit

PWM

Sequencer

Usage Example for UDB

UDB

UDB

UDB

UDB

UDB

UDB

UDB

UDB

22

V

V

to

PSoC

®

3: CY8C38 Family

Data Sheet

Document Number: 001-63724 Rev. *A 页码:4/ 130

有关外设的详细信息,请参见本数据表 “ 外设示例 ” 第40页

的。 有关 UDB、DSI 及其他数字模块的信息,请参见本数据表

“ 数字子系统 ” 第 40 页的。

PSoC 独特可配置性的另外一半则来自于其模拟子系统。 所有模

拟性能都基于高度精确的绝对电压参考(在有效工作温度和电压

下误差小于 0.1%)。 可配置模拟子系统包括:

模拟复用器

电压比较器

电压参考

模数转换器 (ADC)

数模转换器 (DAC)

数字滤波器模块 (DFB)

所有 GPIO 引脚都可以使用内部模拟总线将模拟信号输入和输出

器件。 因此,器件可接多达 62 个分立模拟信号。 模拟子系统的

核心是一个快速、精确,并具有以下特性的可配置的

Delta-Sigma ADC:

偏移小于 100 µV

增益误差为 0.2%

INL 小于 ±2 LSB

DNL 小于 ±1 LSB

SINAD 在 16 位模式下优于 84 dB

该转换器能够满足众多高精度模拟应用的需求,其中包括一些要

求最为严苛的传感器。 而不需要 CPU 的参预。

四个高速电压 DAC 或电流 DAC 支持 8 位输出信号,其更新速率

最高可达 8 Msps。 它们可以路由到任何 GPIO 引脚输入 / 输出。

您可以使用 UDB 阵列创建分辨率更高的电压 PWM DAC 输出。 利

用此方法,可以在高达 48 kHz 的频率下创建高达 10 位的脉冲

宽度调制 (PWM) DAC。 每个 UDB 中的数字 DAC 都支持 PWM、PRS

或 delta-sigma 算法,并且宽度可编程。 除了 ADC、DAC 和 DFB

以外,模拟子系统还提供:

多个未赋定运算放大器

多个可配置的开关电容 / 连续时间 (Switched

Capacitor/Continuous Time, SC/CT) 模块。 这些模块支持:

互阻放大器

可编程增益放大器

混频器

其他类似模拟组件

有关详细信息,请参见本数据表 “ 模拟子系统 ” 第 53 页的。

PSoC 的 8051 CPU 子系统是围绕工作频率高达 67 MHz 的单周期

流水线 8051 8 位处理器构建的。 CPU 子系统包括可编程的嵌套

矢量中断控制器、DMA 控制器和 RAM。 PSoC 的嵌套矢量中断控

制器可让 CPU 直接前进到中断服务例程的第一个地址,而无需在

其他架构中使用的跳转指令,因此具有较低的延迟。 DMA 控制器

使外设能够在没有 CPU 干预的情况下交换数据。 这样一来,CPU

就能够以较慢的速度运行 (降低功耗)或使用这些 CPU 周期来

提高固件算法的性能。 单周期 8051 CPU 的运行速度比标准 8051

处理器快十倍。 处理器速度本身是可以配置的,从而能够针对特

定应用调整运行功耗。

PSoC 的非易失性子系统由闪存、按字节写入的 EEPROM 以及非易

失性配置选项构成。 能够提供高达 64 KB 的片上闪存。 CPU 可以

对闪存的各个区块重新编程,以便使能引导加载程序。 您可以针

对可靠性较高的应用使能纠错码 (Error Correcting Code, ECC)。

功能强大且非常灵活的保护模型能够保护用户的敏感信息,并能

够锁定选定的存储器模块,以便实现读写保护。 片上提供了高达

2 KB 的按字节写入的 EEPROM,用于存储应用程序数据。 此外,

选定的配置选项 (如引导速度和引脚驱动模式)存储在非易失性

存储器中, 以便在上电复位 (POR) 后立即激活相关设置。

PSoC 的三种类型的 I/O 都非常灵活。 多种可在 POR 时设置的驱

动模式。 PSoC 还通过 Vddio 引脚提供多达四个 I/O 电压域。 每

个 GPIO 都具有模拟 I/O、LCD 驱动

[4]

、CapSense

[5]

、灵活的中

断生成、斜率控制,以及数字 I/O 功能。 PSoC 上的 SIO 在用作

输出时,允许独立于 Vddio 设置 V

OH

。 SIO 在输入模式下处于高

阻抗状态。 即使当器件未加电或引脚电压高于供电电压时,亦是

如此。 这使得 SIO 非常适合在 I

2

C 总线上使用,因为当该总线上

的其他器件处于加电状态时,PSoC 可能未加电。 SIO 引脚还具有

非常高的灌电流能力,适用于 LED 驱动等应用。 通过使用 SIO 的

可编程输入阈值特性,可以将 SIO 用作通用模拟电压比较器。 此

外,对于带全速 USB 的器件,还提供了 USB 物理接口 (USBIO)。

当不使用 USB 时,这些引脚还可以用于实现有限的数字功能和进

行器件编程。 本数据表 “I/O 系统与路由 ” 第 33 页的对 PSoC

I/O 的所有特性进行了详细说明。

PSoC 器件集成了非常灵活的内部时钟生成器,能够实现高度的

稳定性和精度。 内部主振荡器 (IMO) 是系统的主时基,在 3 MHz

下的精度为 1%。 IMO 的工作频率介于 3 MHz 至 62 MHz 之间。

可以从主时钟频率生成多个时钟分频,以满足应用需求。 器件提

供了一个 PLL,以便从 IMO、外部晶振或外部参考时钟生成高达

67 MHz 的系统时钟频率。

注

4. 此特性仅在某些器件上提供。 有关详细信息,请参见订购信息第 120 页的。

5. 建议不要将带运算放大器输出的 GPIO 同 CapSense 一起使用。

PSoC

®

3: CY8C38 Family

Data Sheet

Document Number: 001-63724 Rev. *A 页码:5/ 130

器件还包含一个单独的超低功耗内部低速振荡器 (ILO),以便供

睡眠和看门狗定时器使用。 此外,在实时时钟 (RTC) 应用中,

还支持使用 32.768 kHz 的外部监视晶振。 时钟以及可编程时钟

分频器具有高度的灵活性,能够满足大多数时序要求。

CY8C34 系列能够在 1.71 V 至 5.5 V 的电压范围内工作。可以

采用 1.8V ± 5%、2.5 V ±10%、3.3 V ± 10% 或 5.0V ± 10%

等稳压电源,或直接采用多种不同类型的电池。 此外,该系列还

提供了一个集成的高效同步升压转换器,能够采用低至 0.5 V 的

供电电压为器件供电。这样一来,便可以通过单个电池或太阳能

电池为器件直接供电。 不仅如此,您还可以使用升压转换器来生

成器件所需的其他电压,例如,驱动 LCD 显示屏所需的 3.3V 电

压。 升压转换器的输出引脚是 VBOOST,从而可以从 PSoC 为应

用中的其他器件供电。

PSoC 支持多种低功耗模式, 其中包括 200 nA 休眠模式 (RAM

保留数据)和 1 µA 睡眠模式 (RTC 保持运行 )。 在第二种模式

下,可选的 32.768 kHz 监视晶振会连续运行,以保持精确的

RTC。

对所有主要功能模块(包括可编程数字和模拟外设)的供电可由

固件独立控制。 因此,当某些外设未被使用时,可以采用低功耗

后台处理模式。 这样一来,当 CPU 在 6 MHz 下运行时,器件总

电流仅为 1.2 mA,在 3 MHz 下则仅为 0.8 mA。

关于 PSoC 功耗模式的详细信息,请参见本数据表 “ 供电系统 ”

第 29 页的。

PSoC 采用 JTAG(4 线)接口或 SWD (2 线)接口进行编程、调

试和测试。 单线查看器 (SWV) 也可用于进行 “printf” 式调

试。 通过结合使用 SWD 和 SWV,您只需三个引脚,即可实现全

功能调试接口。 借助这些标准接口,您能够利用赛普拉斯公司或

第三方供货商提供的众多硬件解决方案对 PSoC 进行调试或编

程。 PSoC 支持片上断点以及 4 KB 的指令和数据竞争存储器,

以便进行调试。 有关编程、测试和调试接口的详细信息,请参见

本数据表 “ 编程、调试接口与资源 ” 第 63 页的。

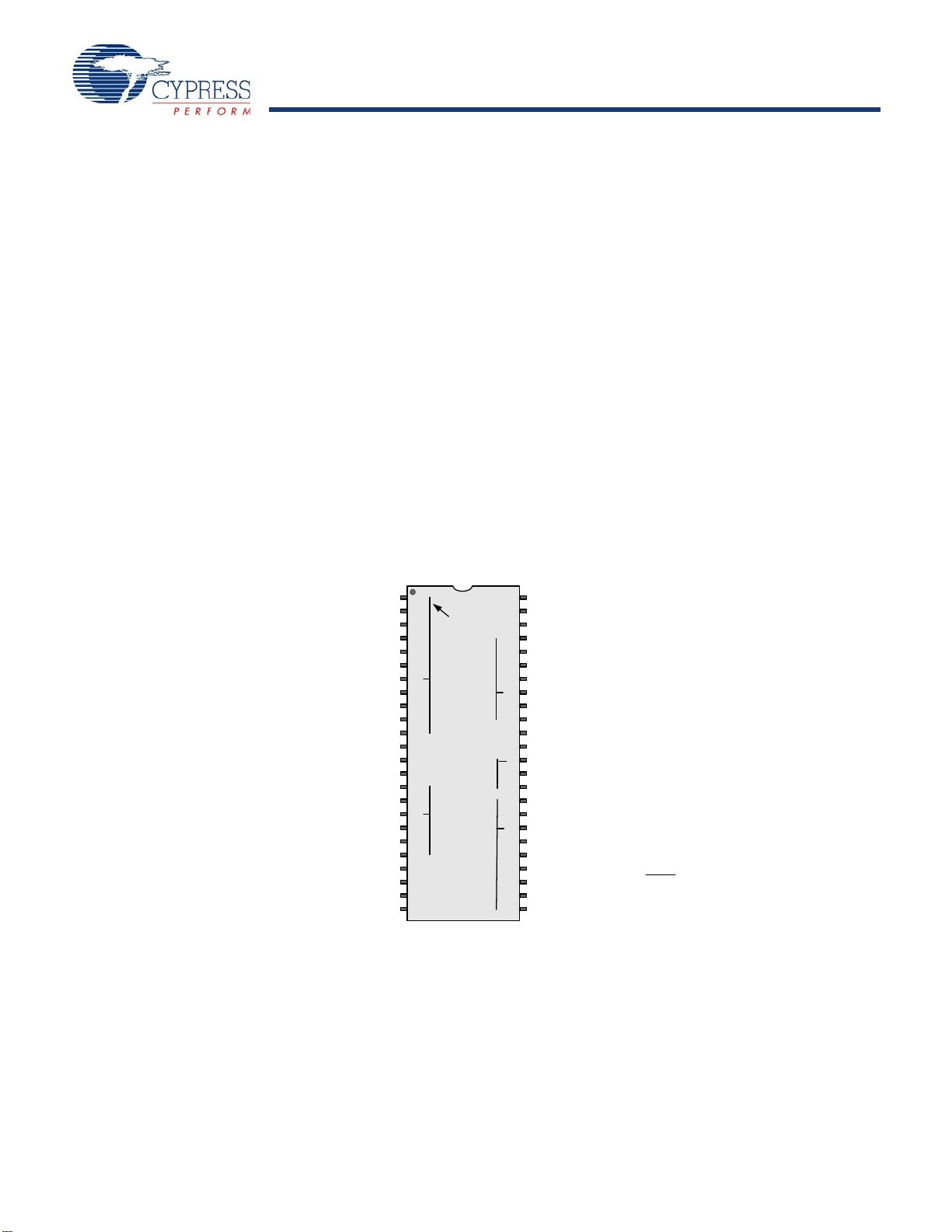

2. 引脚分布

在图 2-1 至图 2-4 的引脚分布图中,用黑色线条标出了为特定

引脚组供电的 VDDIO 引脚。 通过使用 VDDIO 引脚,单个 PSoC

即可支持多个接口电压电平,而无需片外电平转换器。 每个

VDDIO 都可以将高达 100 mA 的总电流灌入到关联的 I/O 引脚和

运算放大器中。 在 68 引脚器件和 100 引脚器件上,每组同

VDDIO 关联的引脚都可以灌入高达 100 mA 的电流。 48 引脚器

件可以为同 VDDIO0 + VDDIO2 关联的所有 I/O 引脚灌入高达 100

mA 的总电流,并为同 VDDIO1 + VDDIO3 关联的所有 I/O 引脚灌

入高达 100 mA 的总电流。

图 2-1. 48 引脚 SSOP 部件的引脚分布图

SSOP

VSSA(SIO) P12[3]

247

VCCA(Opamp2OUT, GPIO) P0[0]

346

P15[3] (GPIO, KHZ XTAL: XI)(Opamp0OUT, GPIO) P0[1]

445

P12[0] (SIO, I2C1: SCL)VDDIO0

742

P12[1] (SIO, I2C1: SDA)

643

(Opamp0-/Extref0, GPIO) P0[3]

P15[1] (GPIO, MHZ XTAL: XI)(Opamp2-, GPIO) P0[5]

940

P15[0] (GPIO, MHZ XTAL: XO)(IDAC0, GPIO) P0[6]

10 39

VCCD(IDAC2, GPIO) P0[7]

11 38

VSSDVCCD

12 37

VDDD

VSSD

13 36

P15[7] (USBIO, D-, SWDCK)VDDD

14 35

P15[6] (USBIO, D+, SWDIO)

(GPIO) P2[3]

15 34

P1[7] (GPIO)

(GPIO) P2[4]

16 33

P1[6] (GPIO)

VDDIO2

17 32

VDDIO1

(GPIO) P2[5]

18 31

P1[5] (GPIO, nTRST)(GPIO) P2[6]

19 30

P1[4] (GPIO, TDI)

(GPIO) P2[7]

20 29

P1[3] (GPIO, TDO, SWV)

VSSB

21 28

IND

22 27

P1[1] (GPIO, TCK, SWDCK)

VBOOST

23 26

P1[0] (GPIO, TMS, SWDIO)

VBAT

24 25

VDDA(SIO) P12[2]

148

VDDIO3(Opamp2+, GPIO) P0[4]

841

P15[2] (GPIO, KHZ XTAL: XO)(Opamp0+, GPIO) P0[2]

544

Lines show

VDDIO to I/O

supply

association

P1[2] (GPIO, Configurable XRES)

[6]

[6]

注

6. 在不带 USB 的器件上,引脚请勿使用 (DNU)

剩余129页未读,继续阅读

资源评论

lanzhenhua11

- 粉丝: 1

- 资源: 5

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功