没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

Allwinner Technology CO., Ltd. A13

A13 User Manual

V1.2

2013.01.08

Allwinner Technology CO., Ltd. A13

A13 User Manual V1.2

Copyright © 2013 Allwinner Technology. All Rights Reserved. 1

Jau.8, 2013

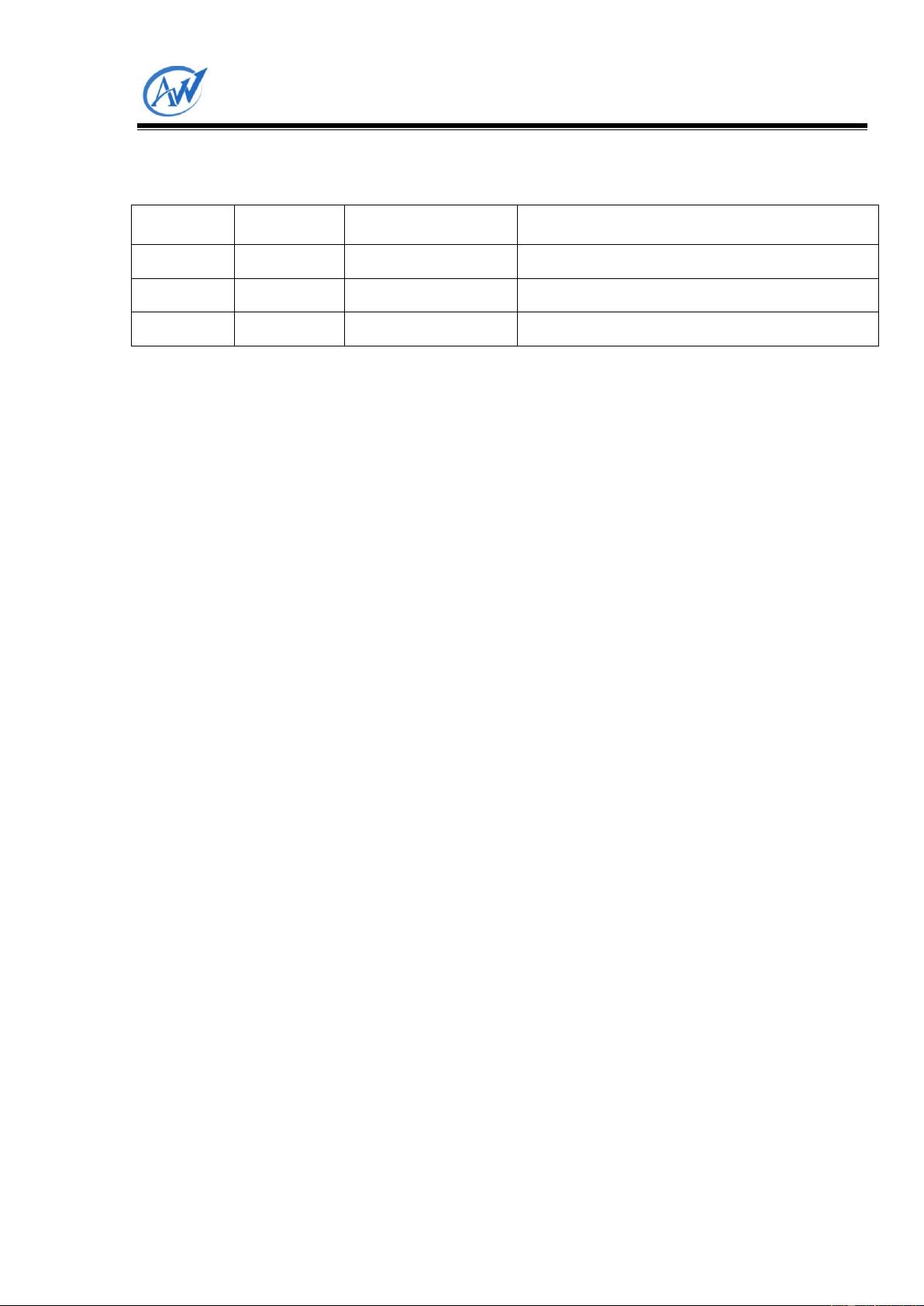

Revision History

Version

Date

Author

Description

V1.0

2012.04.16

Initial version

V1.1

2012.10.25

Modify SDRAM/NAND module descriptions

V1.2

2013.1.8

Modify nand, usb otg, sd3.0

Allwinner Technology CO., Ltd. A13

A13 User Manual V1.2

Copyright © 2013 Allwinner Technology. All Rights Reserved. 2

Jau.8, 2013

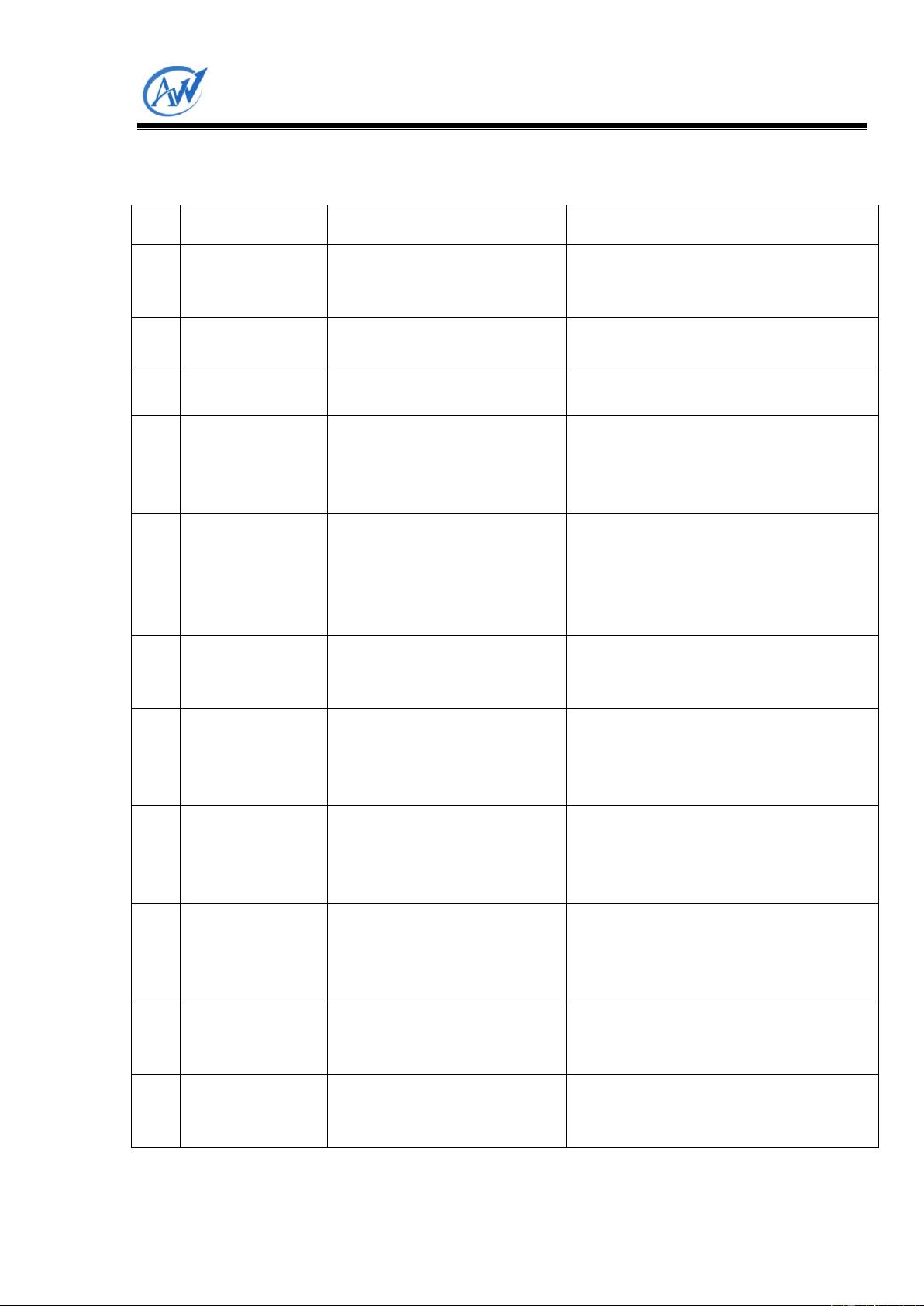

Technical Items

NO.

Abbreviation

Full Name

Description

1

ARM Cortex™-A8

ARM Cortex™-A8

A processor core designed by ARM

Holdings implementing the ARM v7

instruction set architecture

2

Mali-400

Mali-400

A 2D/3D graphic processor unit designed by

ARM Holdings

3

SDRAM

Synchronous Dynamic Random

Access Memory

Dynamic random access memory (DRAM)

that is synchronized with the system bus

4

PWM

Pulse Width Modulator

A commonly used technique for controlling

power to inertial electrical devices, made

practical by modern electronic power

switches

5

SPI

Serial Peripheral Interface

A synchronous serial data link standard

named by Motorola that operates in full

duplex mode. Devices communicate in

master/slave mode where the master device

initiates the data frame

6

UART

Universal Asynchronous

Receiver/Transmitter

used for serial communication with a

peripheral, modem (data carrier equipment,

DCE) or data set

7

DMA

Direct Memory Access

A feature of modern computers that allow

certain hardware subsystems within the

computer to access system memory

independently of the CPU

8

PWM

Pulse Width Modulation

A commonly used technique for controlling

power to inertial electrical devices, made

practical by modern electronic power

switches

9

Audio Codec

Audio Codec

A computer program implementing an

algorithm that compresses and decompresses

digital audio data according to a given audio

file format or streaming media audio format.

10

SD 3.0

Security Digital 3.0

A non-volatile memory card format

developed by the SD Card Association for

use in portable devices.

11

USB OTG

USB On-The-Go

dual-role controller, which supports both

Host and device functions and is full

compliant with the On-The-Go Supplement

Allwinner Technology CO., Ltd. A13

A13 User Manual V1.2

Copyright © 2013 Allwinner Technology. All Rights Reserved. 3

Jau.8, 2013

to the USB 2.0 Specification, Revision 1.0a

12

EHCI

Enhanced Host Controller

Interface

a high-speed controller standard that is

publicly specified

13

OHCI

Open Host Controller Interface

A register-level interface that enables a host

controller for USB or FireWire hardware to

communicate with a host controller driver in

software

14

TP

Touch Panel

A Human-Machine Interactive Interface

15

LRADC

Low Resolution Analog to Digital

Converter

A module which can transfer analog signal

to digital signal

16

CSI

CMOS Sensor Interface

The hardware block that interfaces with

different image sensor interfaces and

provides a standard output that can be used

for subsequent image processing.

Allwinner Technology CO., Ltd. A13

A13 User Manual V1.2

Copyright © 2013 Allwinner Technology. All Rights Reserved. 4

Jau.8, 2013

Table of Contents

Revision History .................................................................................................................................................. 1

Technical Items .................................................................................................................................................... 2

1. A13 Introduction ....................................................................................................................................... 23

1.1. Features .................................................................................................................................. 23

2. Pin Description .......................................................................................................................................... 26

2.1. Pin Placement Table ................................................................................................................. 26

2.2. Pin Detail Description .............................................................................................................. 26

3. Architecture ............................................................................................................................................... 27

3.1. Functional Block Diagram ........................................................................................................ 27

3.2. Memory Mapping .................................................................................................................... 27

4. Boot System ............................................................................................................................................... 31

4.1. Overview ................................................................................................................................ 31

4.2. Boot Diagram .......................................................................................................................... 31

5. Power Management Unit (PMU) ............................................................................................................. 32

5.1. Overview ................................................................................................................................ 32

5.2. PMU Register List ................................................................................................................... 32

5.3. PMU Register Description ........................................................................................................ 33

5.3.1. PMU DVFS Control Register 0 .................................................................................. 33

5.3.2. PMU DVFS Control Register 1(Default : 0x00001010) ............................................. 34

5.3.3. PMU DVFS Control Register 2 .................................................................................. 34

5.3.4. PMU AXI Clock Range Register0 .............................................................................. 35

5.3.5. PMU AXI Clock Range Register1 .............................................................................. 35

5.3.6. PMU DVFS Control Register 3 .................................................................................. 35

5.3.7. PMU DVFS TimeOut Control Register(Default : 0x00000027) .................................. 35

5.3.8. PMU IRQ En Register ................................................................................................ 36

5.3.9. PMU IRQ Status Register .......................................................................................... 37

5.3.10. PMU Status Register .................................................................................................. 38

5.3.11. PMU CPUVDD DCDC Control Register Address(Default : 0x00000023) ................. 38

5.3.12. PMU TWI Address(Default : 0x00000068) ................................................................. 38

5.3.13. PMU CPUVDD Value(Default : 0x00000016) ............................................................ 38

5.3.14. PMU CPUVDD Voltage Ramp Control in DVM .......................................................... 39

5.3.15. PMU 32KHz CPUVDD Minimum Value(Default : 0x0000000C) ................................ 39

5.3.16. PMU VF Table Register 0 ........................................................................................... 40

5.3.17. PMU VF Table Register 1 ........................................................................................... 40

剩余408页未读,继续阅读

lamtao

- 粉丝: 2

- 资源: 6

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

- 1

- 2

- 3

- 4

- 5

- 6

前往页