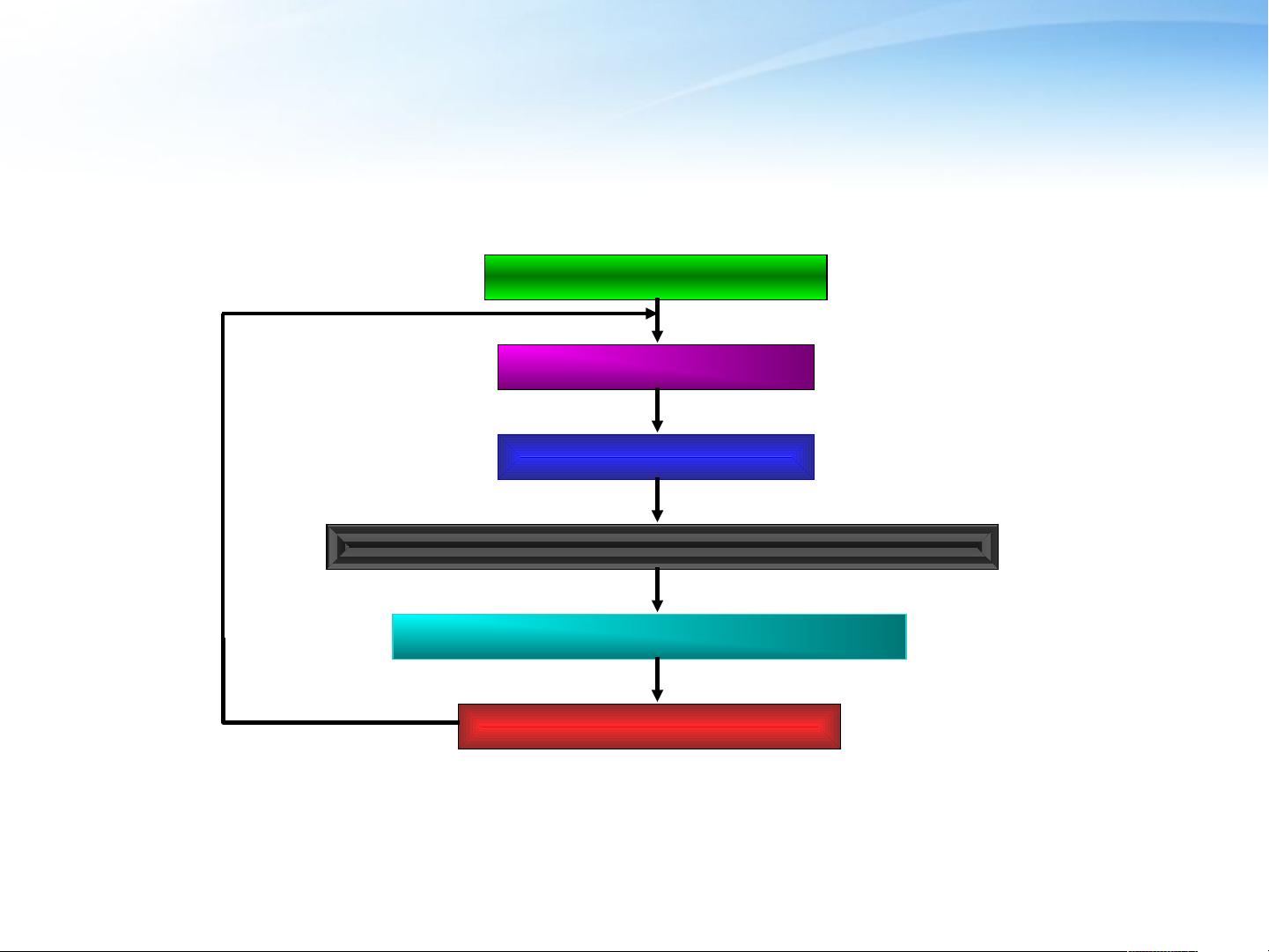

传统数字系统设计流程

设计目标

人工给出真值表

人工化简卡诺图

得到最简表达式

人工使用 LSI 电路实现

系统调试和验证

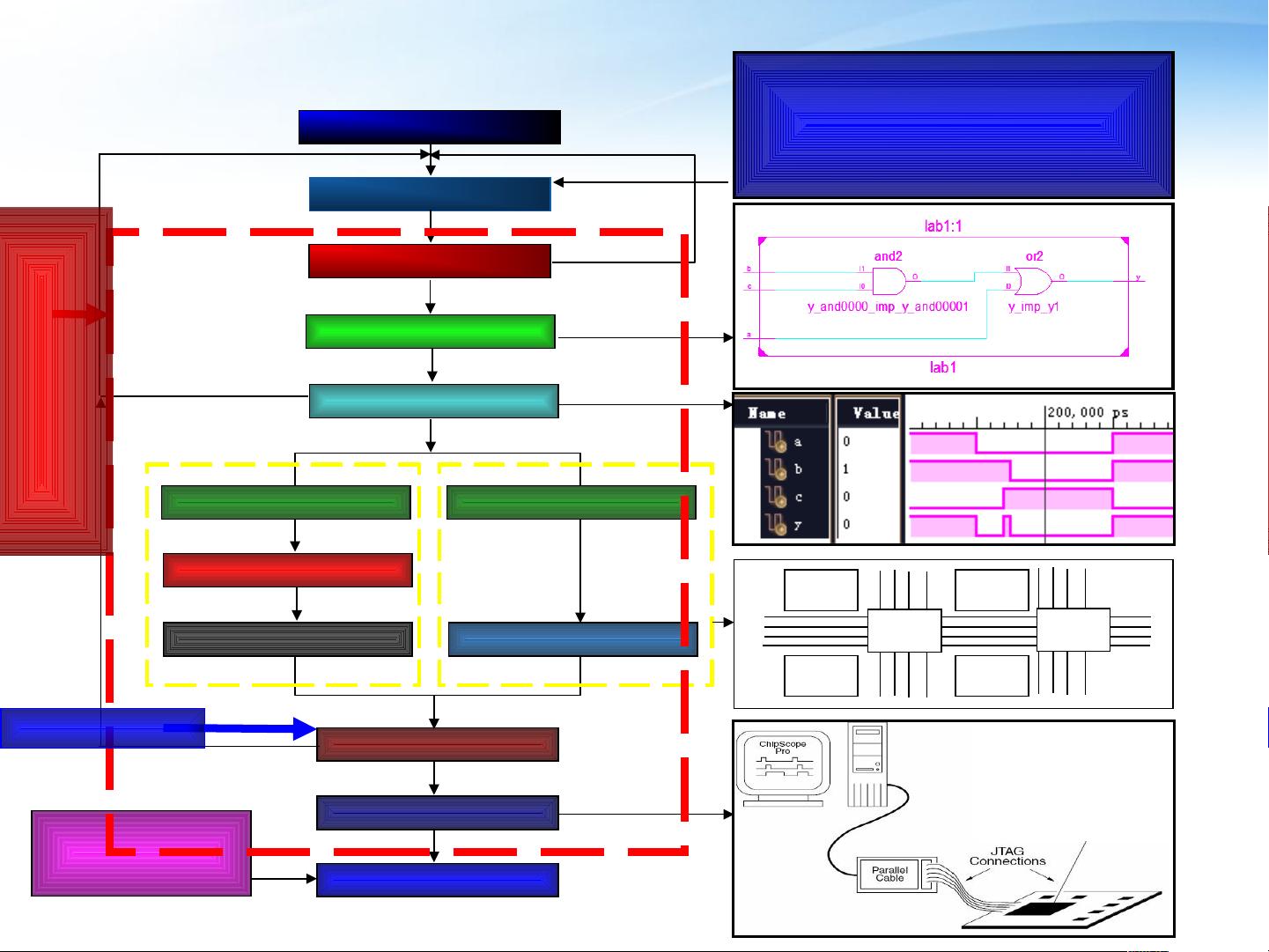

现代数字系统设计流程

设计目标

设计输入

功能级仿真

逻辑综合

时序仿真

系统调试与验证

entity lab1 is

port(a,b,c : in std_logic;

y : out std_logic);

end lab1;

architecture rtl of lab1 is

begin

y<=a or (c and b);

end rtl;

综合后仿真

转换 (Translate) 转换 (Translate)

映射 (Map)

适配 (Fit)布局和布线 (PAR)

设计下载

CPLD 设计

FPGA 设计实现

CLB

CLB

CLB

CLB

配置文件加载后,用

示波器、逻辑分析

仪、软件程序观察

计

算

机

自

动

完

成

时序收敛

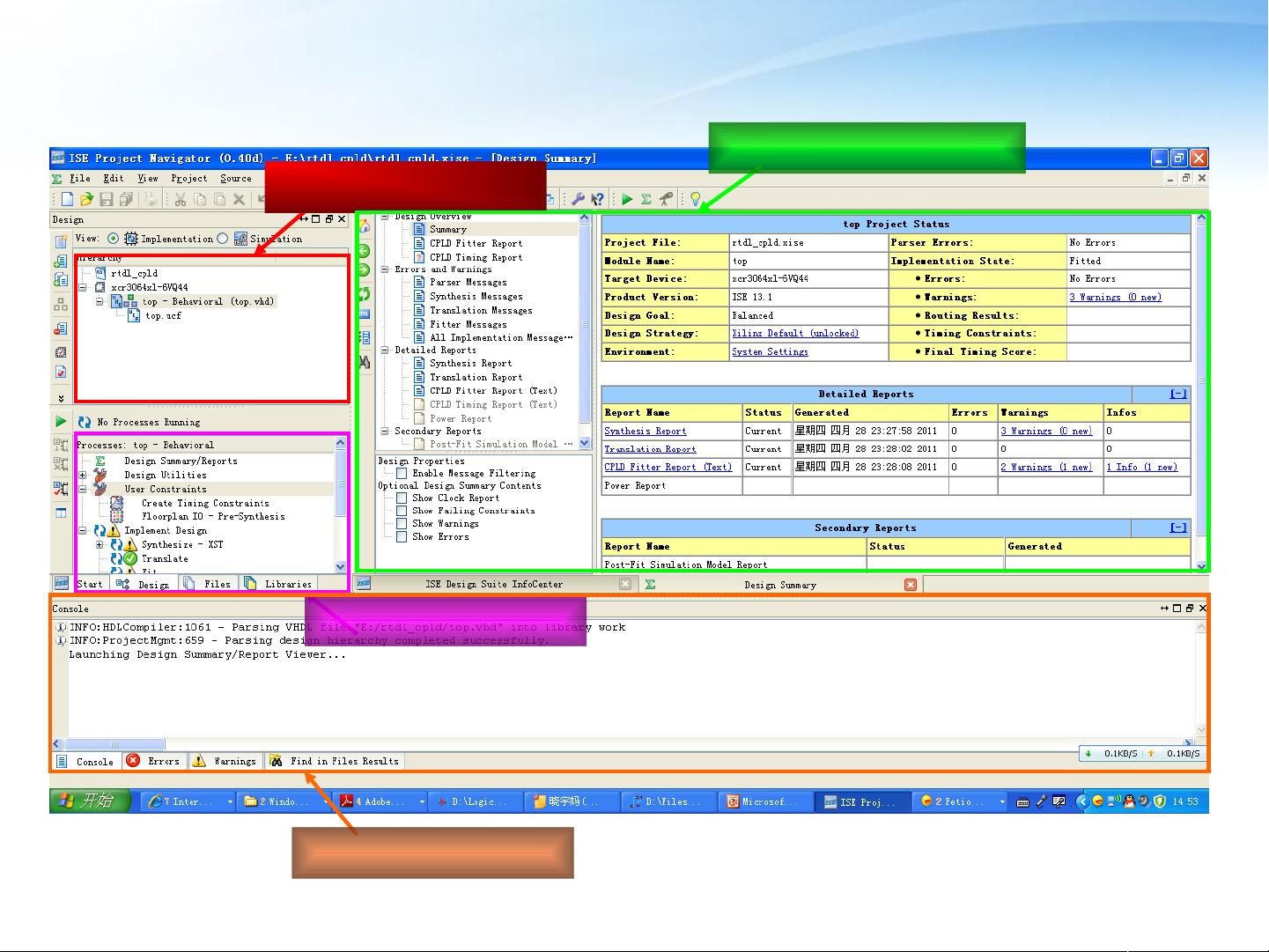

ISE13.1 集成开发环境介绍

-- 主界面介绍

源文件窗口

处理子窗口

脚本子窗口

工作区子窗口

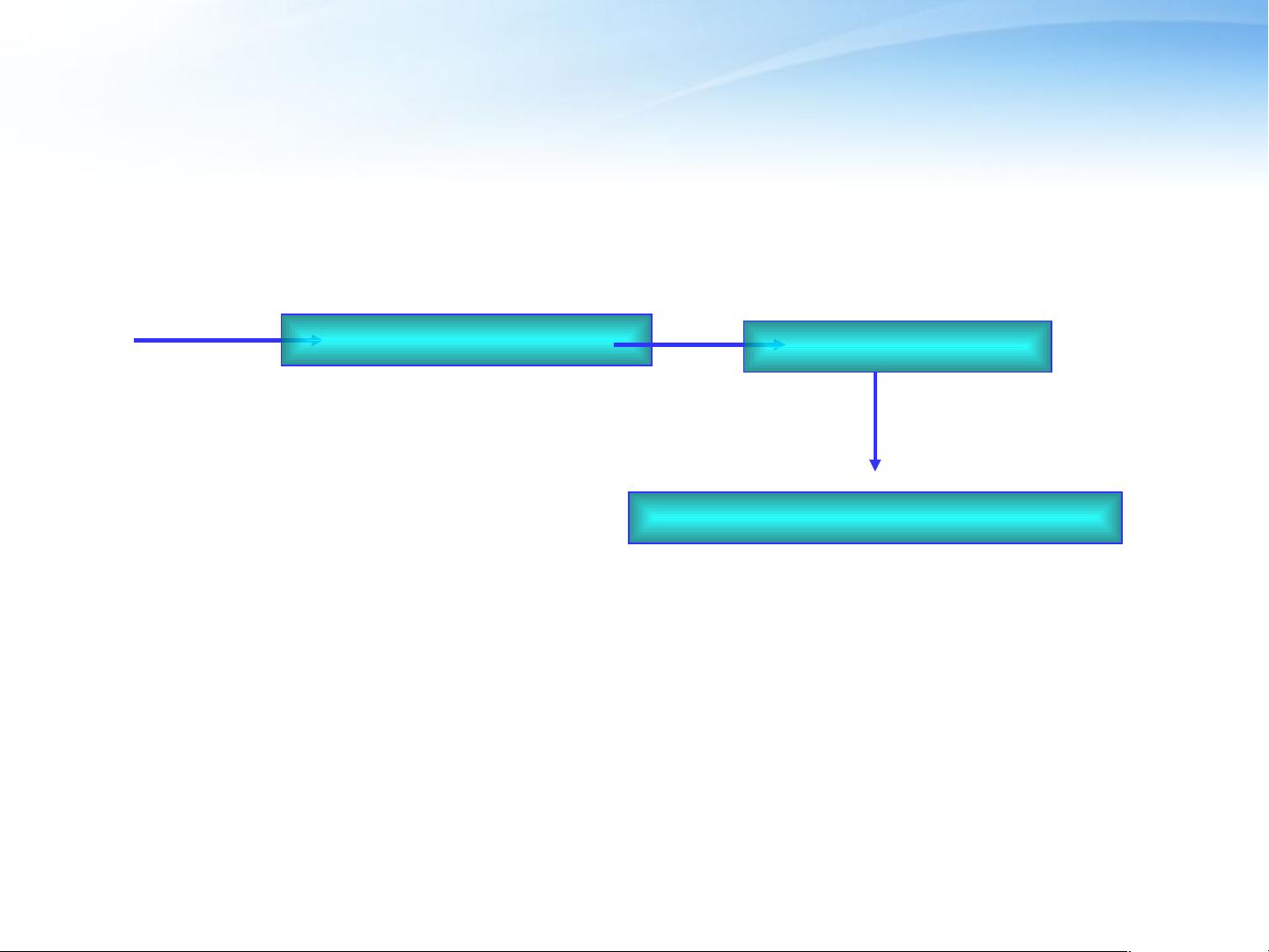

基于 VHDL 语言的 ISE 设计流程

-- 一个数字系统的设计原理

外部 50MHz 时钟

分频器生成电路

1Hz 时钟

3 位的计数器

送给三个灯显示计数的值

基于 VHDL 语言的 ISE 设计流程

-- 设计内容

使用 ISE13.1 完成一个数字系统的设计,其内容包括

:

工程的建立;

三位计数器的设计;

设计综合和查看综合结果;

三位计数器设计仿真;

分频器的设计;

用户约束的添加和设计实现;

布局布线结果的查看;

设计下载到 FPGA 芯片

PROM 文件的生成和下载到 PROM 中

- 1

- 2

前往页