没有合适的资源?快使用搜索试试~ 我知道了~

RDA5802N datasheet_v2.pdf

温馨提示

试读

29页

RDA5802N datasheet_v2.pdf RDA

资源推荐

资源详情

资源评论

Copyright © RDA Microelectronics Inc. 2006. All rights are reserved.

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in

part without prior written permission of RDA.

RDA5802N/NS/NM

SINGLE-CHIP BROADCAST FM RADIO TUNER Rev.2.0–Mar.2011

1 General Description

The RDA5802N series is the newest generation

single-chip broadcast FM stereo radio tuner with fully

integrated synthesizer, IF selectivity, RDS/RBDS and

MPX decoder. The tuner uses the CMOS process,

support multi-interface and require the least external

component. The RDA5802N series have three type

package sizes , respective are RDA5802N (QFN 4X4

mm, 24pins), RDA5802NS (QFN 3X3 mm, 20pins) and

RDA5802NM (QFN 2X2 mm, 12pins). All these make it

very suitable for portable devices.

The RDA5802N series has a powerful low-IF digital

audio processor, this make it have optimum sound

quality with varying reception conditions.

The RDA5802N series support frequency range is from

50MHz to 115MHz.

1.1 Features

CMOS single-chip fully-integrated FM tuner

Low power consumption

Total current consumption lower than 20mA at 3.0V

power supply when under normal situation

Support worldwide frequency band

50 -115 MHz

Support flexible channel spacing mode

100KHz, 200KHz, 50KHz and 25KHz

Support RDS/RBDS

Digital low-IF tuner

Image-reject down-converter

High performance A/D converter

IF selectivity performed internally

Fully integrated digital frequency synthesizer

Fully integrated on-chip RF and IF VCO

Fully integrated on-chip loop filter

Autonomous search tuning

Support 32.768KHz crystal oscillator

Digital auto gain control (AGC)

Digital adaptive noise cancellation

Mono/stereo switch

Soft mute

High cut

Programmable de-emphasis (50/75

s)

Receive signal strength indicator (RSSI) and SNR

Bass boost

Volume control and mute

I

2

S digital output interface

Line-level analog output voltage

32.768 KHz 12M,24M,13M,26M,19.2M,38.4MHz

Reference clock

Only support 2-wire bus interface

2

3

4

5

6

1

7

17

16

15

14

13

18

8 9 10 11 12

24 23 22 21 20 19

GND

PAD

GND

GND

LNAP

GND

RDA

5802N

VDD

GND

LOUT

GND

LNAN

ROUT

GND

VDD

GND

GND

SCLK

SDIO

RCLK

VIO

GND

NC

NC

GPIO1

GPIO2

GPIO3

Figure1-1. RDA5802N Top View

RDA Microelectronics, Inc. RDA5802N/NS/NM FM Tuner V2.0

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in

part without prior written permission of RDA. Page 2 of 29

Directly support 32Ω resistance loading

Integrated LDO regulator

1.8 to 5.5 V operation voltage

Support QFN 4X4mm 24pins, QFN 3X3mm 20pins and

QFN 2x2mm 12pins three package types.

1.2 Applications

Cellular handsets

MP3, MP4 players

Portable radios

PDAs, Notebook

RDA Microelectronics, Inc. RDA5802N/NS/NM FM Tuner V2.0

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in

part without prior written permission of RDA. Page 3 of 29

Table of Contents

1 General Description .................................................................................................................................... 1

1.1 Features ......................................................................................................................................... 1

1.2

Applications

.................................................................................................................................... 2

Table of Contents................................................................................................................................................. 3

2 Functional Description ............................................................................................................................... 4

2.1 FM Receiver .................................................................................................................................. 4

2.2 Synthesizer .................................................................................................................................... 4

2.3 Power Supply ................................................................................................................................ 5

2.4 RESET and Control Interface select ............................................................................................. 5

2.5 Control Interface ........................................................................................................................... 5

2.6 I

2

S Audio Data Interface ............................................................................................................... 5

2.7 GPIO Outputs ................................................................................................................................ 5

3 Electrical Characteristics ........................................................................................................................... 6

4 Receiver Characteristics ............................................................................................................................. 7

5 Serial Interface ............................................................................................................................................ 8

5.1 I

2

C Interface Timing ...................................................................................................................... 8

6 Register Definition ...................................................................................................................................... 9

9 Application Diagram................................................................................................................................. 19

9.1 RDA5802N Common Application : ............................................................................................ 19

9.1.1 Bill of Materials: ......................................................................................................................... 19

9.2 RDA5802NS Common Application: ........................................................................................... 20

9.2.1 Bill of Materials: ......................................................................................................................... 20

9.3 RDA5802NM Common Application: ......................................................................................... 21

9.3.1 Bill of Materials: ......................................................................................................................... 21

10 Physical Dimension ................................................................................................................................... 22

11 PCB Land Pattern ..................................................................................................................................... 25

12 Change List ................................................................................................................................................ 28

13 Notes: ....................................................................................................................................................... 28

14 Contact Information ................................................................................................................................. 29

RDA Microelectronics, Inc. RDA5802N/NS/NM FM Tuner V2.0

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in

part without prior written permission of RDA. Page 4 of 29

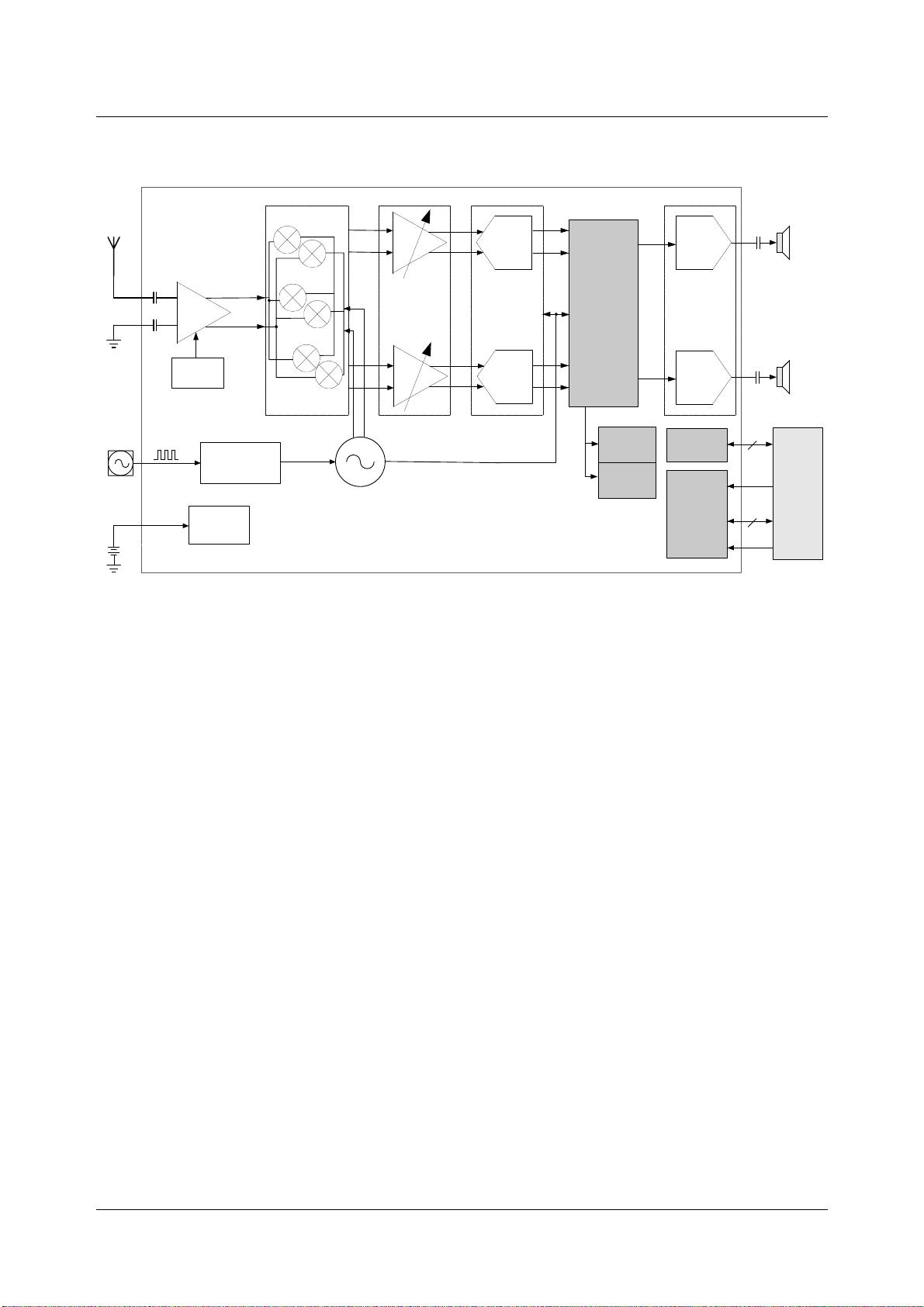

2 Functional Description

I

ADC

L

DAC

R

DAC

Q

ADC

+

-

Audio

DSP

Core

digital filter

MPX decoder

stereo/mono

audio

VCO

Synthesizer

GPIO

Interface

Bus

RSSI

VIO

SDIO

SCLK

MCU

GPIO

RDA5802N

LOUT

ROUT

LNAN

LNAP

RCLK

2.7-5.5 V

32.768 KHz

VDD

LDO

Limiter

LNA

I

PGA

Q

PGA

RDS

/RBDS

Figure 2-1. RDA5802N FM Tuner Block Diagram

2.1 FM Receiver

The receiver uses a digital low-IF architecture that

avoids the difficulties associated with direct

conversion while delivering lower solution cost

and reduces complexity, and integrates a low

noise amplifier (LNA) supporting the FM

broadcast band (50 to 115MHz), a multi-phase

image-reject mixer array, a programmable gain

control (PGA), a high resolution analog-to-digital

converters (ADCs), an audio DSP and a high-

fidelity digital-to-analog converters (DACs).

The LNA has differential input ports (LNAP and

LNAN) and supports any input port by set

according registers bits (LNA_PORT_SEL[1:0]). It

default input common mode voltage is GND.

The limiter prevents overloading and limits the

amount of intermodulation products created by

strong adjacent channels.

The multi-phase mixer array down converts the

LNA output differential RF signal to low-IF, it also

has image-reject function and harmonic tones

rejection.

The PGA amplifies the mixer output IF signal and

then digitized with ADCs.

The DSP core finishes the channel selection, FM

demodulation, stereo MPX decoder and output

audio signal. The MPX decoder can autonomous

switch from stereo to mono to limit the output

noise.

The DACs convert digital audio signal to analog

and change the volume at same time. The DACs

has low-pass feature and -3dB frequency is about

30 KHz.

2.2 Synthesizer

The frequency synthesizer generates the local

oscillator signal which divide to multi-phase, then

be used to downconvert the RF input to a

constant low intermediate frequency (IF). The

synthesizer reference clock is 32.768 KHz.

The synthesizer frequency is defined by bits

CHAN[9:0] with the range from 50MHz to

115MHz.

RDA Microelectronics, Inc. RDA5802N/NS/NM FM Tuner V2.0

The information contained herein is the exclusive property of RDA and shall not be distributed, reproduced, or disclosed in whole or in

part without prior written permission of RDA. Page 5 of 29

2.3 Power Supply

The RDA5802N integrated one LDO which

supplies power to the chip. The external supply

voltage range is 1.8-5.5 V.

2.4 RESET and Control Interface select

The RDA5802N is RESET itself When VIO is

Power up. And also support soft reset by trigger

02H BIT1 from 0 to 1. T he RDA5802N only

support I

2

C control interface bus mode.

2.5 Control Interface

The RDA5802N only supports I

2

C control

interface.

The I

2

C interface is compliant to I

2

C Bus

Specification 2.1. It includes two pins: SCLK and

SDIO. A I

2

C interface transfer begins with START

condition, a command byte and data bytes, each

byte has a followed ACK (or NACK) bit, and ends

with STOP condition. The command byte includes

a 7-bit chip address (0010000b) and a R/W bit.

The ACK (or NACK) is always sent out by receiver.

When in write transfer, data bytes is written out

from MCU, and when in read transfer, data bytes

is read out from RDA5802N. There is no visible

register address in I

2

C interface transfers. The I

2

C

interface has a fixed start register address (0x02h

for write transfer and 0x0Ah for read transfer), and

an internal incremental address counter. If register

address meets the end of register file, 0x3Ah,

register address will wrap back to 0x00h. For write

transfer, MCU programs registers from register

0x02h high byte, then register 0x02h low byte,

then register 0x03h high byte, till the last register.

RDA5802N always gives out ACK after every byte,

and MCU gives out STOP condition when register

programming is finished. For read transfer, after

command byte from MCU, RDA5802N sends out

register 0x0Ah high byte, then register 0x0Ah low

byte, then register 0x0Bh high byte, till receives

NACK from MCU. MCU gives out ACK for data

bytes besides last data byte. MCU gives out

NACK for last data byte, and then RDA5802N will

return the bus to MCU, and MCU will give out

STOP condition.

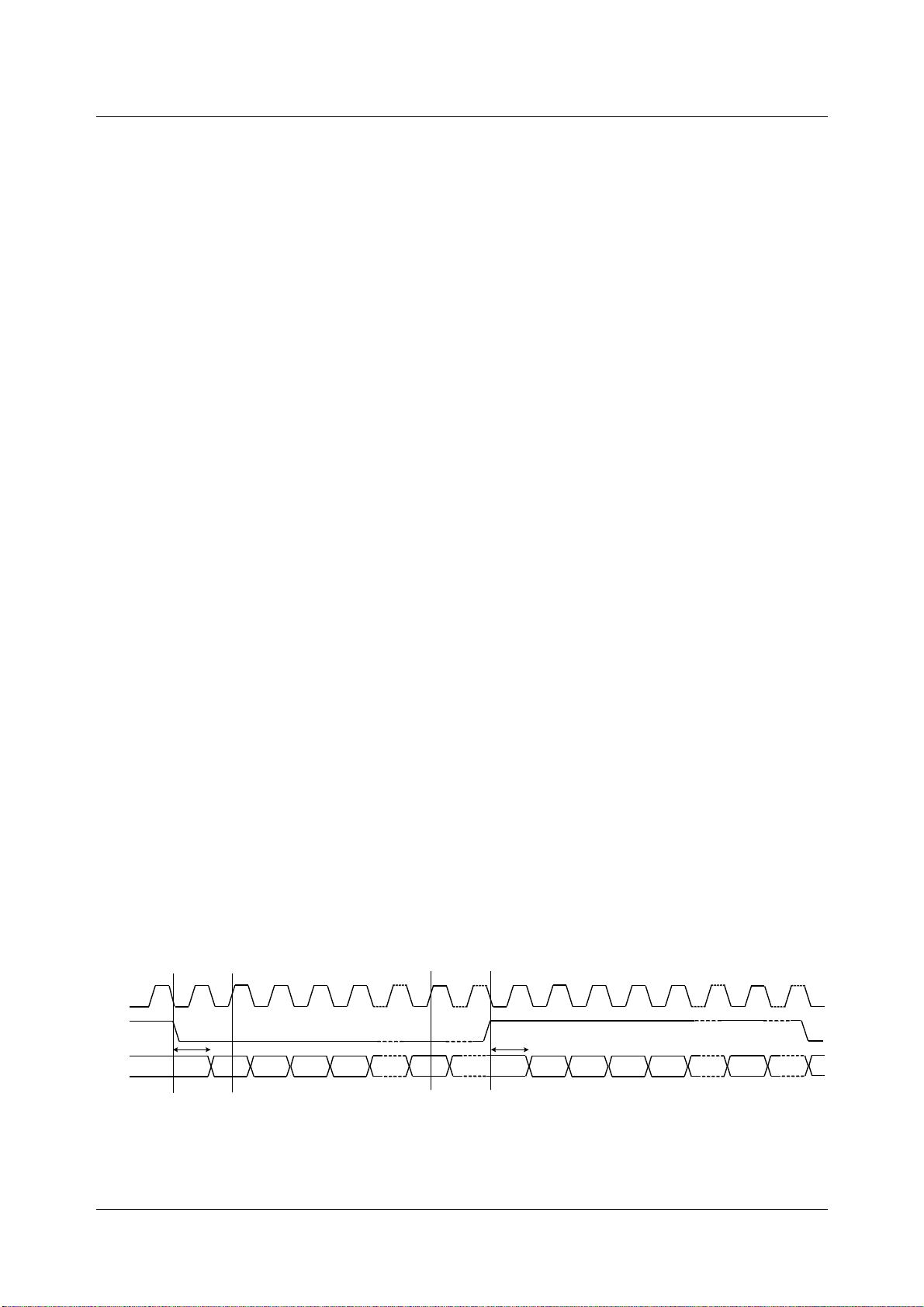

2.6 I

2

S Audio Data Interface

The RDA5802N supports I

2

S (Inter_IC Sound Bus)

audio interface. The interface is fully compliant

with I

2

S bus specification. When setting I2SEN bit

high, RDA5802N will output SCK, WS, SD signals

from GPIO3, GPIO1, GPIO2 as I

2

S master and

transmitter, the sample rate is 48Kbps ,

44.1kbps,32kbps….. RDA5802N also support as

I

2

S slaver mode and transmitter, the sample rate

is less than 100kbps.

2.7 GPIO Outputs

The RDA5802N has three GPIOs. The function of

GPIOs could programmed with bits GPIO1[1:0],

GPIO2[1:0], GPIO3[1:0] and I2SEN.

If I2SEN is set to low, GPIO pins could be

programmed to output low or high or high-Z, or be

programmed to output interrupt and stereo

indicator with bits GPIO1[1:0], GPIO2[1:0],

GPIO3[1:0]. GPIO2 could be programmed to

output a low interrupt (interrupt will be generated

only with interrupt enable bit STCIEN is set to high)

when seek/tune process completes. GPIO3 could

be programmed to output stereo indicator bit ST.

Constant low, high or high-Z functionality is

available regardless of the state of VDD supplies

or the ENABLE bit.

SCK

MSB

SD

WS

1 SCK

LEFT CHANNEL

LSB MSB

1 SCK

RIGHT CHANNEL

LSB

Figure 3-2 I2S Digital Audio Format

剩余28页未读,继续阅读

资源评论

lixiao_11162016-08-09Hardware-firmware Interface Design

lixiao_11162016-08-09Hardware-firmware Interface Design johnsonsam2014-10-04及时雨啊,客户急着要芯片资料,一时手头又没有,还好在这里找到了。

johnsonsam2014-10-04及时雨啊,客户急着要芯片资料,一时手头又没有,还好在这里找到了。

laicq

- 粉丝: 2

- 资源: 8

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功