没有合适的资源?快使用搜索试试~ 我知道了~

资源详情

资源评论

资源推荐

FUNCTIONAL BLOCK DIAGRAM

LL

DL

CLK

DR

LR

DGND

V

L

NRL

AGND

NRR

V

S

1

2

3

4

5

6

7

8

9

10

12

13

14

15

11

16

AD1866

16-BIT

DAC

16-BIT

DAC

16-BIT

SERIAL

REGISTER

16-BIT

SERIAL

REGISTER

V

B

L

V

O

R

V

S

V

B

R

V

REF

V

REF

V

O

L

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

a

Single Supply

Dual 16-Bit Audio DAC

AD1866*

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

FEATURES

Dual Serial Input, Voltage Output DACs

Single +5 Volt Supply

0.005% THD+N

Low Power –50 mW

115 dB Channel Separation

Operates at 83 Oversampling

16-Pin Plastic DIP or SOIC Package

APPLICATIONS

Multimedia Workstations

PC Audio Add-In Boards

Portable CD and DAT Players

Automotive CD and DAT Players

Noise Cancellation

PRODUCT DESCRIPTION

The AD1866 is a complete dual 16-bit DAC offering excellent

performance while requiring a single +5 V power supply. It is

fabricated on Analog Devices’ ABCMOS wafer fabrication

process. The monolithic chip includes CMOS logic elements,

bipolar and MOS linear elements and laser trimmed, thin-

film resistor elements. Careful design and layout techniques

have resulted in low distortion, low noise, high channel separa-

tion and low power dissipation.

The DACs on the AD1866 chip employ a partially segmented

architecture. The first three MSBs of each DAC are segmented

into 7 elements. The 13 LSBs are produced using standard

R-2R techniques. The segments and R-2R resistors are laser

trimmed to provide extremely low total harmonic distortion.

The AD1866 requires no deglitcher or trimming circuitry.

Each DAC is equipped with a high performance output ampli-

fier. These amplifiers achieve fast settling and high slew rate,

producing ±1 V signals at load currents up to ±1 mA. The buff-

ered output signal range is 1.5 V to 3.5 V. The 2.5 V reference

voltages eliminate the need for “false ground” networks.

A versatile digital interface allows the AD1866 to be directly

connected to all digital filter chips. Fast CMOS logic elements

allow for an input clock rate of up to 16 MHz. This allows for

operation at 2×, 4×, 8×, or 16× the sampling frequency (where

F

S

= 44.1 kHz) for each channel. The digital input pins of the

AD1866 are TTL and +5 V CMOS compatible.

*Protected by U.S. Patent Nos: 3,961,326; 4,141,004; 4,349,811; 4,857,862;

and patents pending.

The AD1866 operates on +5 V power supplies. The digital

supply, V

L

, can be separated from the analog supply, V

S

, for re-

duced digital feedthrough. Separate analog and digital ground

pins are also provided. In systems employing a single +5 volt

power supply, V

L

and V

S

should be connected together. In bat-

tery operated systems, operation will continue even with re-

duced supply voltage. Typically, the AD1866 dissipates 50 mW.

The AD1866 is packaged in either a 16-pin plastic DIP or a

16-pin plastic SOIC package. Operation is guaranteed over the

temperature range of –35°C to +85°C and over the voltage

supply range of 4.75 V to 5.25 V.

PRODUCT HIGHLIGHTS

1. Single supply operation @ +5 V.

2. 50 mW power dissipation.

3. THD+N is 0.005% (typical).

4. Signal-to-Noise Ratio is 95 dB (typical).

5. 115 dB channel separation (typical).

6. Compatible with all digital filter chips.

7. 16-pin DIP and 16-pin SOIC packages.

8. No deglitcher required.

9. No external adjustments required.

REV. 0

–2–

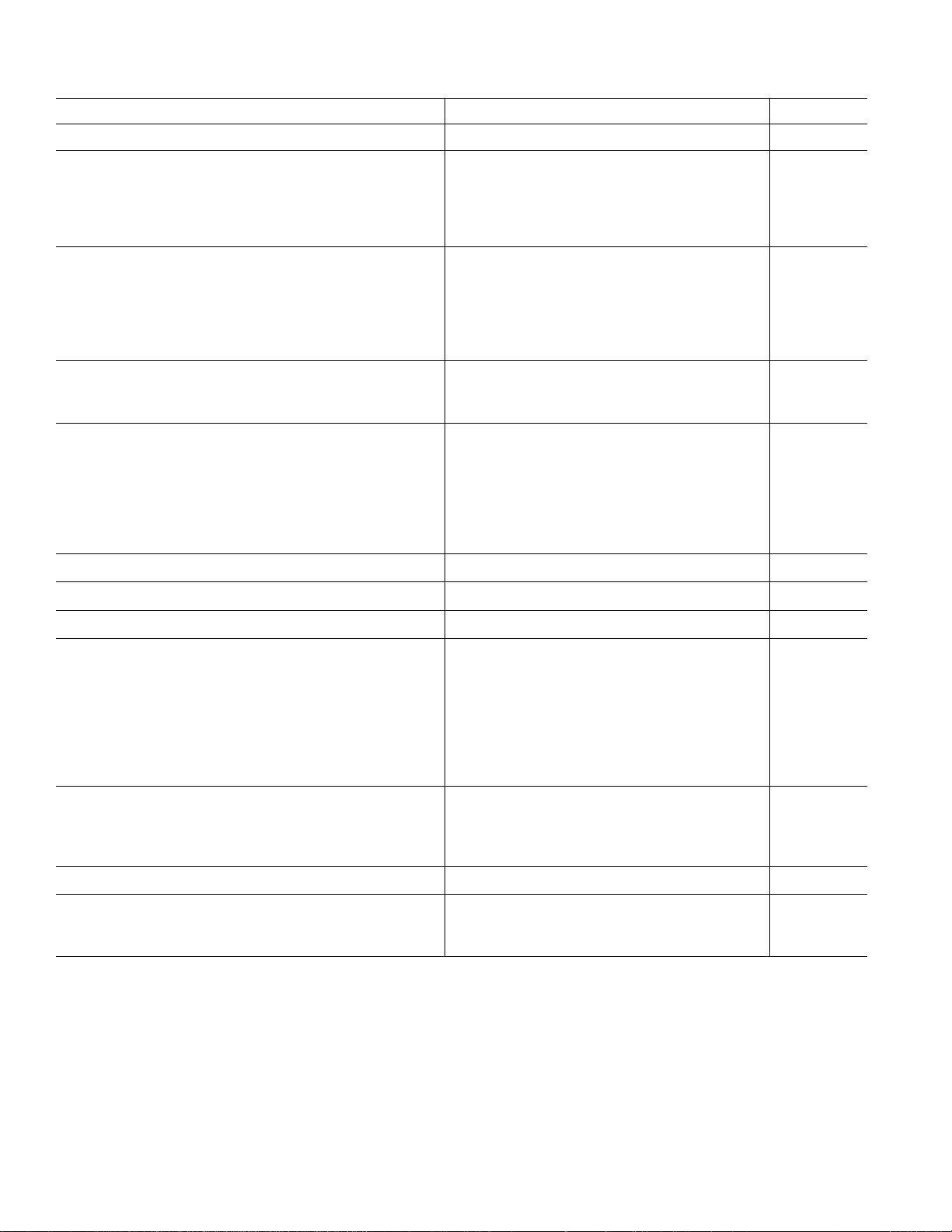

AD1866–SPECIFICATIONS

(T

A

= +258C and +5 V supplies unless otherwise noted)

Min Typ Max Unit

RESOLUTION 16 Bits

DIGITAL INPUTS V

IH

2.4 V

V

IL

0.8 V

I

IH

, V

IH

= V

L

1.0 µA

I

IL

, V

IL

= DGND –10.0 µA

Maximum Clock Input Frequency 13.5 MHz

ACCURACY

Gain Error ±3 % of FSR

Gain Matching ±3 % of FSR

Midscale Error ±30 mV

Midscale Error Matching ±10 mV

Gain Linearity Error ±3dB

DRIFT (0°C to +70°C)

Gain Drift ±100 ppm/°C

Midscale Drift –130 µV/°C

TOTAL HARMONIC DISTORTION + NOISE

0 dB, 990.5 Hz AD1866N 0.005 0.01 %

AD1866R 0.005 0.01 %

–20 dB, 990.5 Hz AD1866N 0.02 %

AD1866R 0.02 %

–60 dB, 990.5 Hz AD1866N 2.0 %

AD1866R 2.0 %

CHANNEL SEPARATION (1 kHz, 0 dB) 108 115 dB

SIGNAL-TO-NOISE RATIO (With A-Weight Filter) 95 dB

D-RANGE (With A-Weight Filter) 90 dB

OUTPUT

Voltage Output Pins (V

OL

, V

OR

)

Output Range (±3%) ±1V

Output Impedance 0.1 Ω

Load Current ±1mA

Bias Voltage Pins (V

BL

, V

BR

)

Output Range +2.5 V

Output Impedance 350 Ω

POWER SUPPLY

Specification, V

L

and V

S

4.75 5 5.25 V

Operation, V

L

and V

S

3.5 5.25 V

+I, V

L

and V

S

= 5 V 10 14 mA

POWER DISSIPATION 50 70 mW

TEMPERATURE RANGE

Operation –35 85 °C

Storage –60 100 °C

Specifications subject to change without notice.

Specifications in boldface are tested on all production units at final electrical

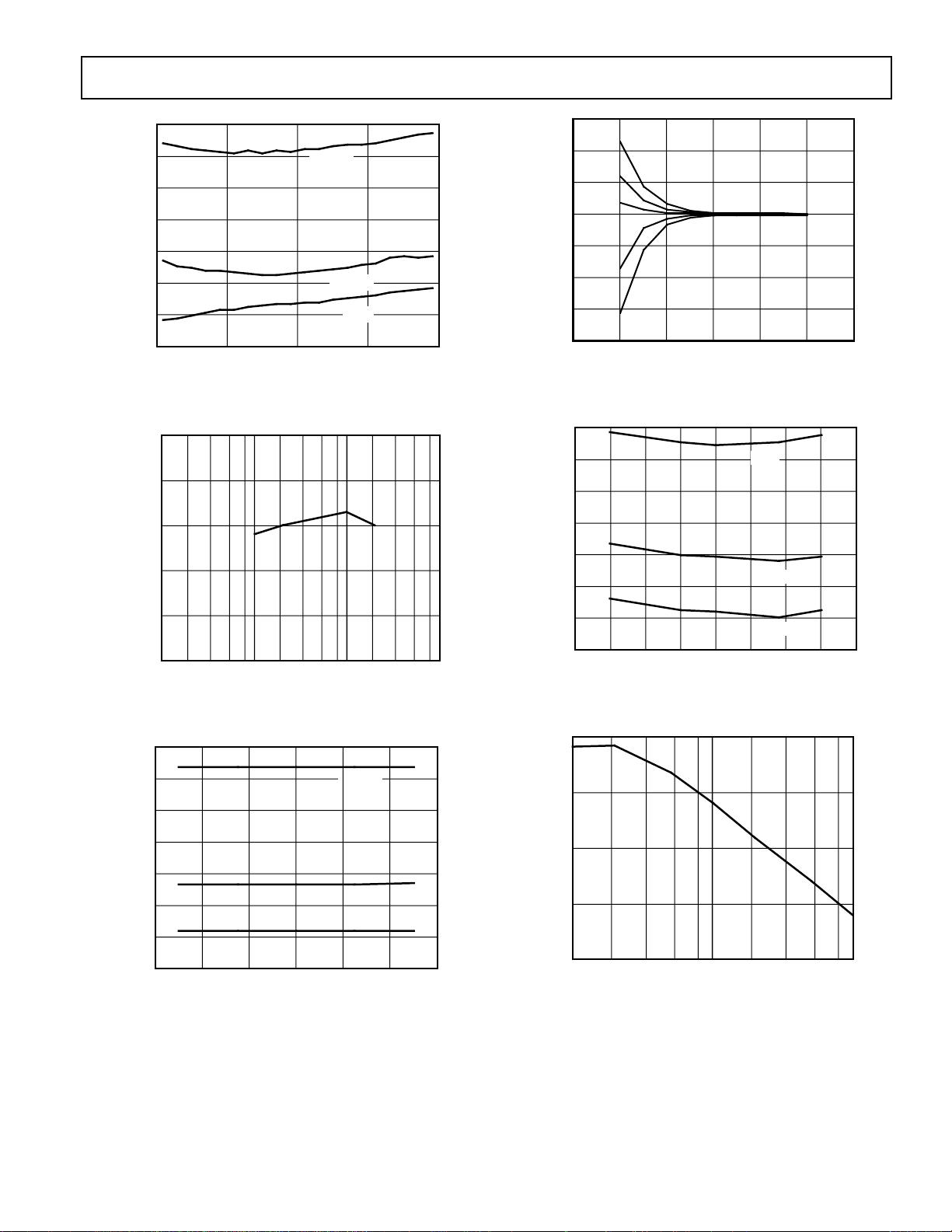

Typical Performance–AD1866

REV. 0

–3–

–100

–90

–80

–70

–60

–50

–40

–30

205005500500 15500

10500

FREQUENCY – Hz

THD+N – dB

–60dB

–20dB

0dB

Figure 1. THD+N vs. Frequency

125

120

123

121

10

3

122

10

2

124

10

4

FREQUENCY – Hz

CHANNEL SEPARATION – dB

10

5

Figure 2. Channel Separation vs. Frequency

–20dB

SUPPLY VOLTAGE

THD+N – dB

0dB

–30

–100

5.6

–70

–90

4.6

–80

4.4

–40

–60

–50

5.45.25.04.8

–60dB

Figure 3. THD+N vs. Supply Voltage

INPUT AMPLITUDE – dB

GAIN LINEARITY ERROR – dB

6

–8

20

–2

–6

–80

–4

–100

4

0

2

0

–20–40–60

125°C

–35°C

0°C

25°C

70°C

Figure 4. Gain Linearity Error vs. Input Amplitude

TEMPERATURE – °C

THD+N – dB

–30

–100

125

–70

–90

–50

–80

–75

–40

–60

–50

100755025

0

–25

–60dB

–20dB

0dB

Figure 5. THD+N vs. Temperature

FREQUENCY – Hz

PSRR – dB

80

40

10

3

10

5

70

50

10

4

60

Figure 6. Power Supply Rejection Ratio vs. Frequency

(Supply Modulation Amplitude at 500 mV p-p)

剩余11页未读,继续阅读

knightdream

- 粉丝: 1

- 资源: 6

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0