没有合适的资源?快使用搜索试试~ 我知道了~

AT45DB041B中文手册

温馨提示

试读

33页

Atmel公司的data Flash存储芯片AT45DB041B中文手册

资源推荐

资源详情

资源评论

phdkan@163.com 翻译

特点

单电源 2.5V-3.6V 或 2.7V-3.6V 供电

兼容串行外设接口

最高 20MHZ 时钟频率

页编写操作

—单周期程序重调(擦除和编写)

—2048 页(264 字节/页)主内存

支持页和块擦除操作

双 264 字节 SRAM 数据缓存—在非易失性

存储器中进行程序重调时可接收数据

能过连续地读取整个存储阵列

低功耗

—有效读取工作电流仅为 4 毫安

—CMOS 待机电流仅为 2 微安

数据保护功能

100%与 AT45DB041 及 AT45DB041A 兼容

5V 输入容限电压:SI,SCK,CS,RESET 和 WP 引脚

商用及工业用温度范围

描述

AT45DB041B 仅需 2.5V 或 2.7V 供电,采用串行接口闪存,能

够广泛的适用于各种数字语音,图像,编码以及数据存储应用。

其 4,325,376 位的内存是由 2048 个页构成,每页为 264 个字节。

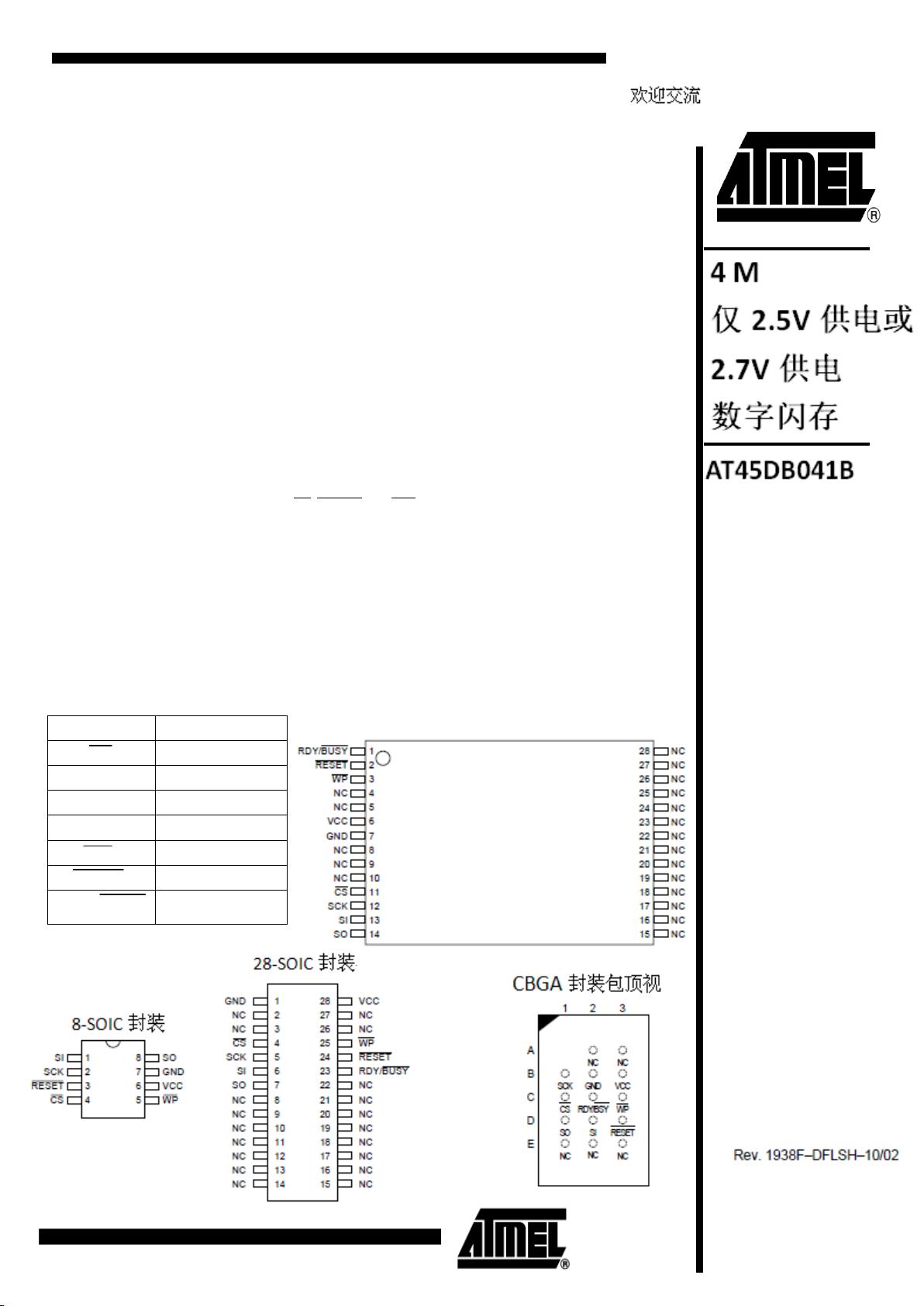

引脚配置 TSOP 顶视

类型 1

引脚名称

功能

CS

片选

SCK

连续时钟

SI

连续输入

SO

连续输出

WP

硬件页写保护

RESET

芯片复位

RDY/BUSY

等待/忙

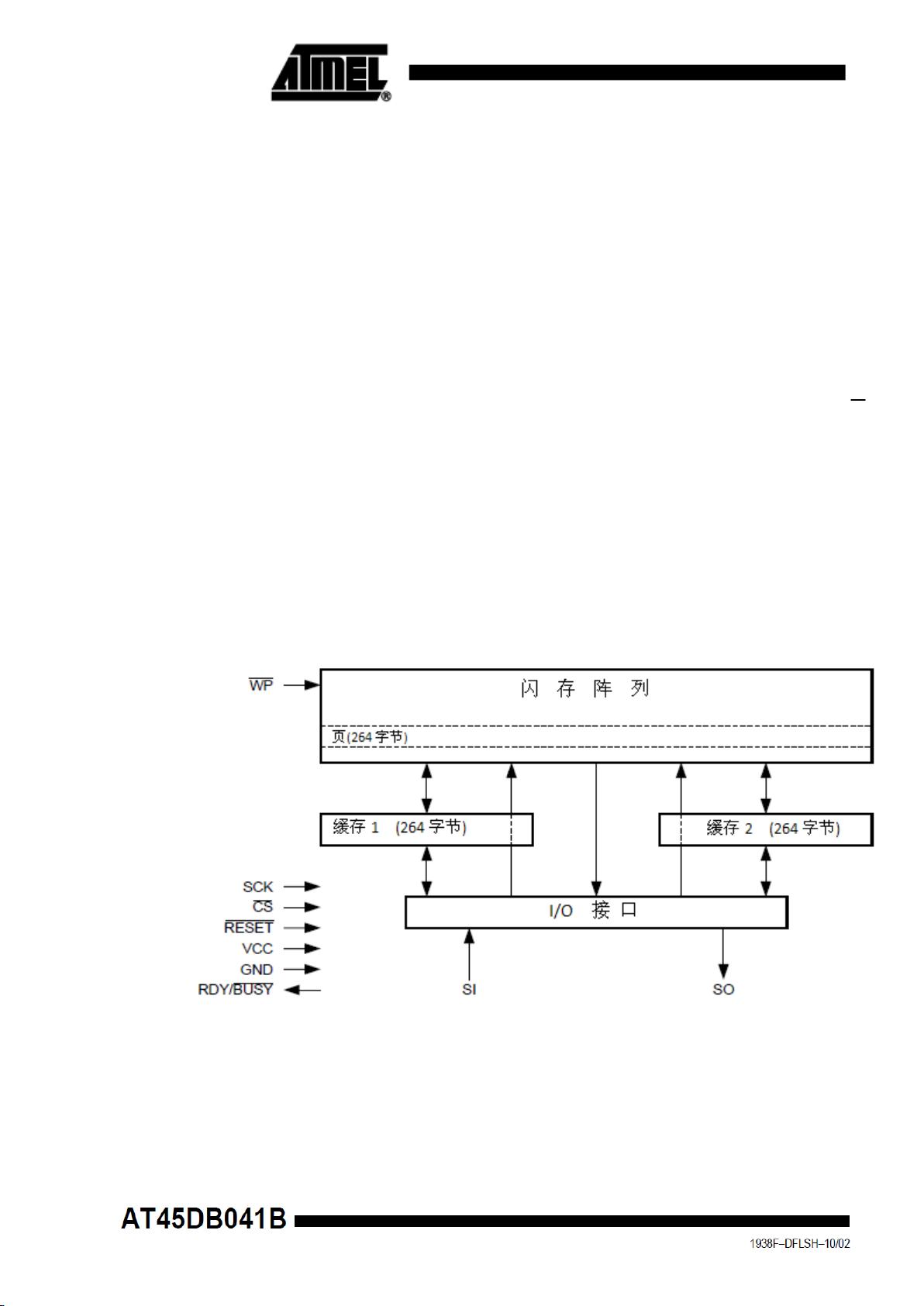

除了主存以外,AT45DB041B 还有两个容量为 264 字节的 SRAM 数据缓存。当在主内

存的某页上进行程序重调或者连续读写数据流时,数据缓存都可以接收数据。

EEPROM 仿真(位或字节可变更)能够容易地处理独立的三步读-修改-写操作。不同

于传统的以多路地址线和并行接口随机访问的闪存芯片,本数字闪存是利用 SPI 串

行接口来顺序存取其数据。该数字闪存支持 SPI 模式 0 和模式 3。其简单的串行接口

使得外围硬件设计变得容易,增强了系统的可靠性,最大化减小了开关噪声,降低

了封装尺寸和有效引脚数量。该器件能够最优化的运用于以高密度,少引脚数量,

低电压和低功耗为基本要求的各类商业和工业场合。该器件的有效工作电流为 4 毫

安,能运行达到 20MHZ 的时钟频率。

AT45DB041B 不需要高输入电压就可以进行简单在系统编写。在进行编写和读操作时,

本器件需要单独的电源供电,电压为 2.5V 至 3.6V 或者 2.7V 至 3.6V。片选引脚 CS

和一个由连续输入 SI,连续输出 SO 和连续时钟 SCK 组成的三线访问接口使得

AT45DB041 正常工作。

所有的编写周期都是自同步的,因而在编写之前都无需分开的擦除周期。

当器件从 Atmel 公司出厂后,存储阵列中最高页可能没有被擦除净。也就是说,最

后一个页中的内容可能并非是 FFH。

框图

存储阵列

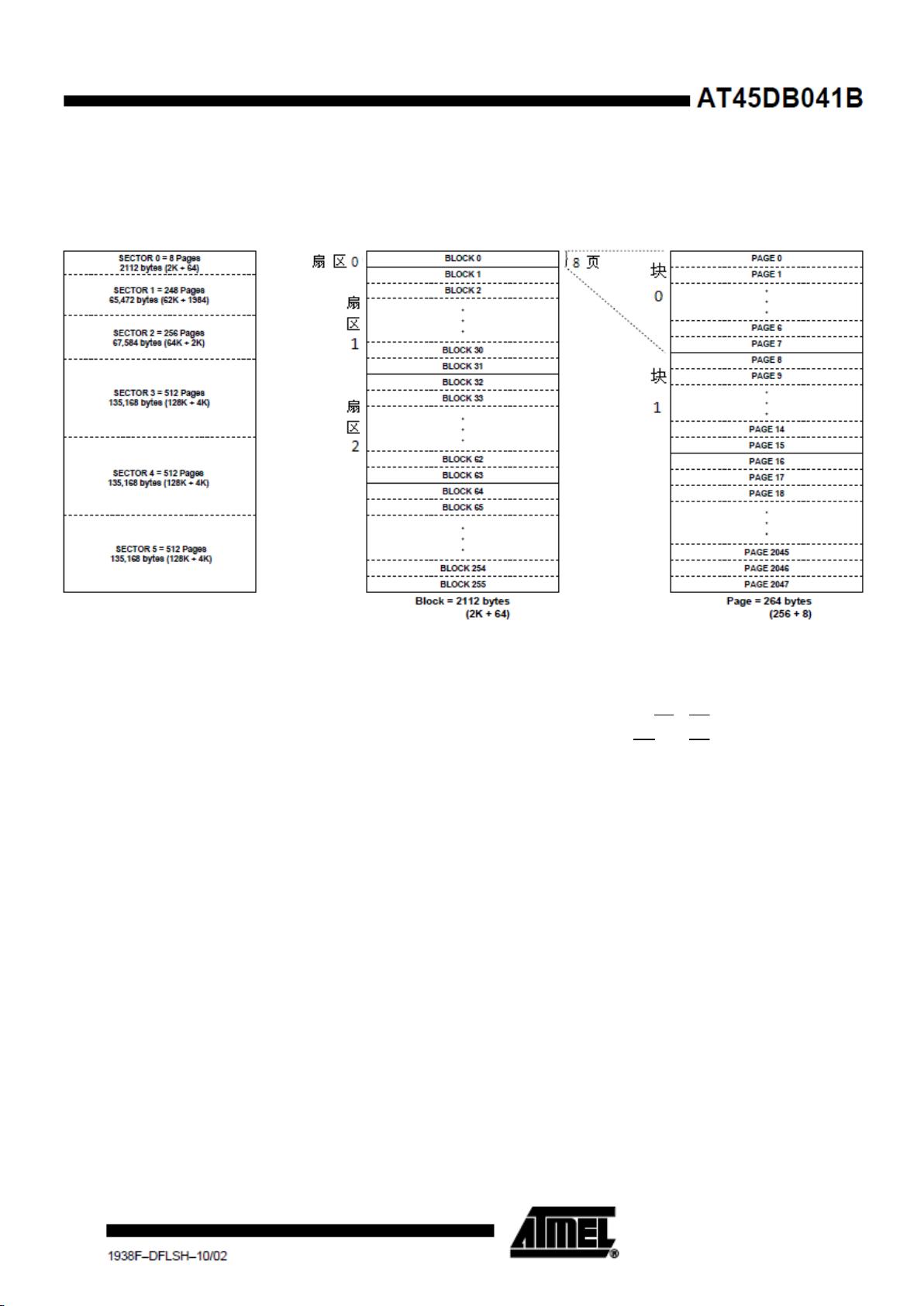

为提供最佳的灵活性,AT45DB041B 的存储阵列被分为由扇区,块,和页组成的三种

颗粒等级。存储器体系结构框图说明了每个等级的细目分类和一个扇区,块含页面

数的详细结构。所有对于数字闪存的编写操作都以逐页为基础,但可选择的擦除操

作能够在块级或者页面级完成。

存储器体系结构框图

扇区结构 块结构 页结构

器件操作 设备运行受微处理器的指令控制。指令清单和与之相的操作码都包含在表一至

表四中(见第 10,11 页)。一条有效的指令起始于 CS 管脚的下降沿,并跟随相

应的 8 位操作码和指定的缓存或主存地址码。当 CS 管脚为低电平时,轮换时钟

管脚 SCK 控制操作码和指定的缓存或主存地址码通过 SI 脚的载入。所有的指

令、地址和数据都从高字节开始传送。

缓存地址是引用自数据手册中的术语 BFA8-BFA0 来表示必须的 9 位地址码从而

指定一缓存中的一个字节地址。主存地址引用了术语 PA10-PA0 和 BA9-BA0,

其中 PA10-PA0 表示必须的 11 位地址码来指定一个页地址,而 BA8-BA0 表示必

须的 9 位地址码来指定一页中的一个字节地址。

读取命令 通过指定适当的操作码,数据能够从主内存或者两个数据缓存中的任一个中进

行读取。该数字闪存支持与 SCK(连续时钟)信号相关的两种读取模式。两种

模式的不同之处在于未激活态的 SCK 信号以及从哪个时钟周期开始数据输出。

这两个种类总共由 4 种模式构成,分别定义为未激活态时钟极性低或未激活态

时钟极性高和 SPI 模式 0 或 SPI 模式 3.一个独立的操作码(参考第 10 页的表 1

完整表单)用于选择以哪种类型来读取。每种模式更详细的时钟周期请参见本

数据手册中的“位级读取时序”框图。

连续阵列读取:通过给主存阵列提供一个初始地址,只需一个时钟信号,就能

使用该命令来从器件中读取连续的数据流,而不需要附加的地址信息和其他的

控制信号。本数字闪存内部整合了一个地址计数器,它能够基于每个时钟周期

自动的增加,因此不用附加地址序列就可以完成连续读操作。要完成一个连续

的读操作,操作码 68H 或者 E8H 后必须跟 24 位地址码和 32 位任意码。24 位地

址码序列的前 4 位是保留位,这是为了让器件具备向上和向下兼容不同密度器

件的的能力(参见“读/写指令序列”图)。接下来的 11 位地址码(PA10-PA0)

要从主存中读取的页,而 24 位地址码的最后 9 位(BA8-BA0)指明了该页中的

起始字节的地址。跟在 24 位地址码后的 32 位任意码是用来初始化读操作。接

下来,在 SCK 脚上的时钟脉冲就使得连续的数据从 SO 脚上输出。

当加载操作码,地址码,任意码和读取数据的时候,CS 脚上必须保持低电平。

在连续阵列读取时,读到主存中页末端的时候,器件将会继续从下一页的起始

处读取,而在页面交叉处(某页的末端至下页的起始处)是没有时间开销的。

当读到主存阵列中的最后一位,器件将会继续回读至内存中第一页的起始处。

CS 脚上一个由低到高电平的跃变将终止读取操作和 SO 脚上的三态。连续阵列

读取的最大 SCK 频率是由

CAR

f

来规定的。连续阵列读取不经由两个数据缓存,

因此使缓存中的内容保持不变。

主存页读取:主存页读取允许用户从主存的 2048 页中的任意某一页直接读取数

据,不经由两个数据缓存,因此使缓存中的内容保持不变。要进行一个页读取,

先要给器件发送操作码 52H 或者 D2H,且其后必须跟着 24 位地址码和 32 位任

意码。其中 24 位地址码序列的首 4 位为保留位,后 11 位(PA10-PA0)指明了

该页的地址,最后 9 位地址码(BA8-BA0)指明了该页中首字节的地址。而跟在

24 位地址码后的 32 位任意码是用于初始化读取操作。在 32 位任意码后,SCK

脚上的脉冲信号会可使连续的数据从 SO(连续输出)脚上输出。当在加载操作

码,地址码,任意码和读取数据时,CS 脚必须保持低电平。在进行主存页读取

操作期间,当读到主存中某一页的末端时,器件将会继续从相同的页的起始处

开始读。CS 脚上低电平到高电平的跃变将终止读取操作和 SO 脚上的三态。

缓存读取:数据能从 2 个数据缓存的任一个中读取,用不同的操作码可指明从

哪个缓存中读取。操作码 54H 或 D4H 用于从缓存 1 中读取,操作码 56H 或 D6H

用于从缓存 2 中读取。要完成缓存读取操作,8 位操作码后须跟着 15 位任意码,

9 位地址码,和 8 位任意码。因为缓存的容量为 264 字节,故要求 9 位地址码

(BFA8-BF10)来指明从缓存中读取的第一个字节。当在加载操作码,地址码,

任意码和读取数据时,CS 脚必须保持低电平。当读到缓存的末端时,器件将继

续回读到缓存的起始处。CS 脚上低电平到高电平的跃变将终止读取操作和 SO

脚上的三态。

状态寄存器读取:状态寄存器能用于决定器件的读/忙状态,主存页到缓存比较

操作的结果,或器件密度。要读取状态寄存器,操作码 57H 或 D7H 必须装载至

器件。操作码的最后一位移入以后,状态寄存器的 8 位码,从最高位(位 7)

开始,会在接下来的 8 个时钟周期内从 SO 脚移出。状态寄存器的高 5 位包含了

器件信息,而低 3 位为以后扩展作为保留位以及有未定义值。当状态寄存器的

0 位被移出,这个过程将重复,从最高位再次开始移出(只要 CS 脚保持低电平

且 SCK 处于轮换时钟态)。因状态寄存器内的数据会保持更新,所以每次重复过

程都会输出新的数据。

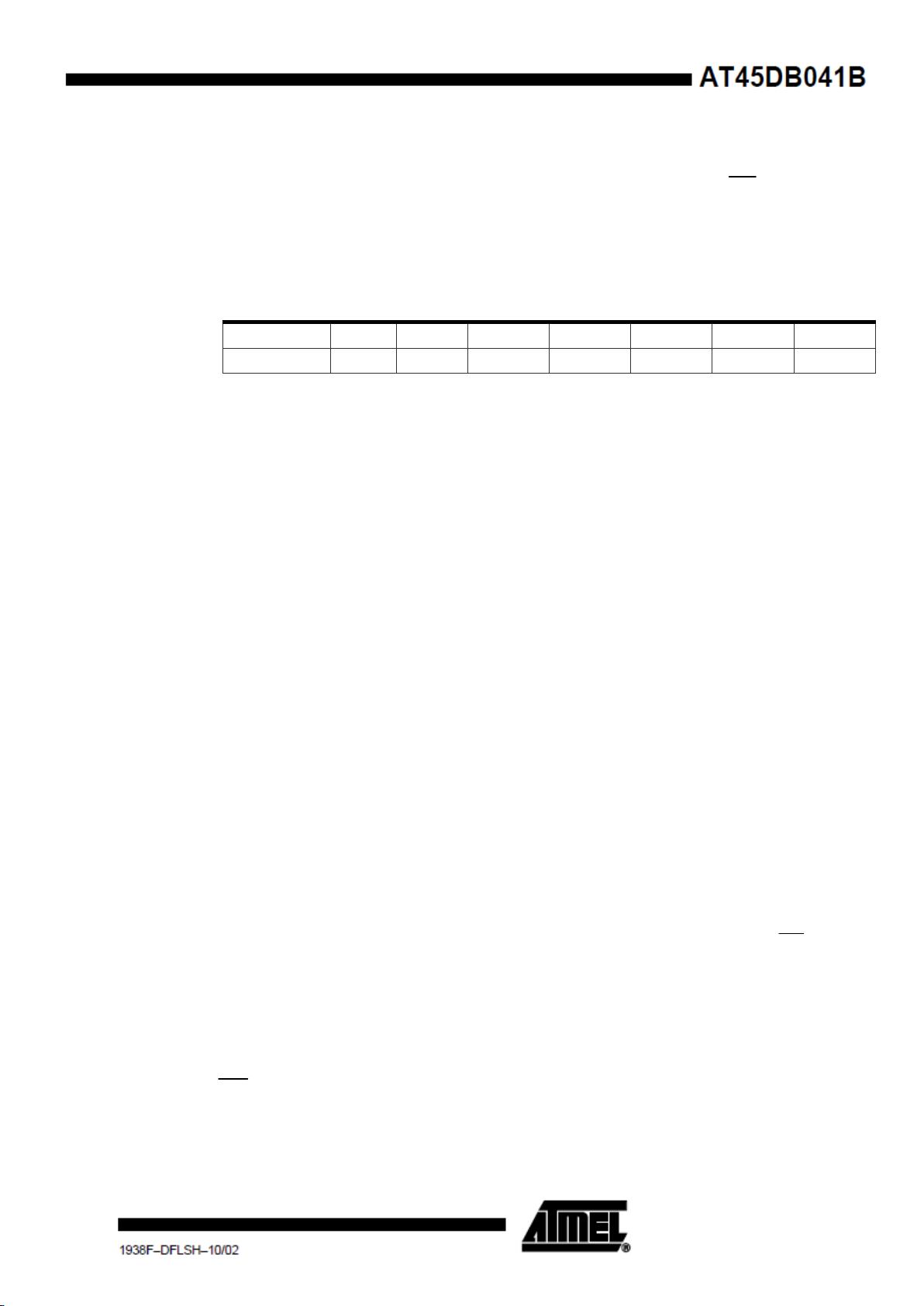

状态寄存器格式

状态寄存器的位 7 来指示准备/忙状态。如果位 7 的值为 1,那么器件就不为忙

状态且准备接收下一条命令。如果位 7 的值为 0,那么器件就处于忙状态。

当位 7 被输出后,用户可通过停止 SCK 信号来把状态寄存器的位 7 连续的拉低。

位 7 的值会连续地从 SO 脚上输出,而且只要器件不再处于忙状态,那么 SO 脚

就会从 0 变为 1。共有 8 种操作能使器件处于忙状态,分别是:主存页到缓存的

传送,主存页与缓存比较,带内置擦除的缓存至主存页的编写,不带内置擦除

的缓存至主存页的编写,页擦除,块擦除,主存页编写和自动页重写。

状态寄存器的位 6 用于表示最近一次的主存页与缓存比较操作的结果。如果位 6

的值为 0,那么就表示主存页中的数据与缓存中的数据相同。如果位 6 的值为 1,

那么主存页中的数据和缓存中的数据至少有一位不同。

状态寄存器的位 5,4,3 和 2 用于表示器件密度。对于 AT45DB041B,此四位就

为 0,1,1 和 1。该 4 位二进制对应的十进制数值并不等于器件密度;此 4 位码

表示的是与一系列数字闪存器件相关的不同密度的组合码,共允许有 16 种不同

的密度配置。

编写和擦除命令

写缓存:数据能从 SI 脚移入至缓存 1 或缓存 2 中的一个。要加载数据至任意一

缓存,8 位操作码(84H 用于缓存 1,87H 用于缓存 2)后必须跟着 15 位任意

码和 9 位地址码(BFA8-BFA0)。 9 位地址码指明了要写入缓存中的首字节。数据

紧随着地址码输入。如果写到缓存末端,器件就回转至缓存起始处。CS 上一个

由低到高电平的跃变,将结束写缓存操作。

带内置擦除的缓存至主存页的编写:写入缓存 1 或缓存 2 中的数据能够编写至主

存中。要完成此操作,8 位操作码(83H 用于缓存 1,86H 用于缓存 2)必须跟着

4 位保留位,11 位用于指定目的页的地址码(PA10-PA0), 和 9 位任意码。当在

CS 脚上出现由低到高电平的跃变时,该部分会首先在 1 秒内擦除主存中选定的

页,然后将储存在缓存中的数据编写至主存中的指定页。擦除和页编写操作都是

内部自同步,而且会在t

EP

的最大值内完成。在这个时间内,状态寄存器将指示

器件处于忙状态。

位 7

位 6

位 5

位 4

位 3

位 2

位 1

位 0

准备/忙

比较

0

1

1

1

×

×

剩余32页未读,继续阅读

资源评论

w_xinggang2012-09-14不错,内容号,要是能有中文的就更好了

w_xinggang2012-09-14不错,内容号,要是能有中文的就更好了 L187763515532013-08-11翻译得很清楚

L187763515532013-08-11翻译得很清楚 i99ln442013-07-06不错,真是原版,可以参考。

i99ln442013-07-06不错,真是原版,可以参考。

SuperRabbit

- 粉丝: 2

- 资源: 18

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- #P0015. 全排列 超级简单

- pta题库答案c语言之排序4统计工龄.zip

- pta题库答案c语言之树结构7堆中的路径.zip

- pta题库答案c语言之树结构3TreeTraversalsAgain.zip

- pta题库答案c语言之树结构2ListLeaves.zip

- pta题库答案c语言之树结构1树的同构.zip

- 基于C++实现民航飞行与地图简易管理系统可执行程序+说明+详细注释.zip

- pta题库答案c语言之复杂度1最大子列和问题.zip

- 三维装箱问题(Three-Dimensional Bin Packing Problem,3D-BPP)是一个经典的组合优化问题

- 以下是一些关于Linux线程同步的基本概念和方法.txt

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功