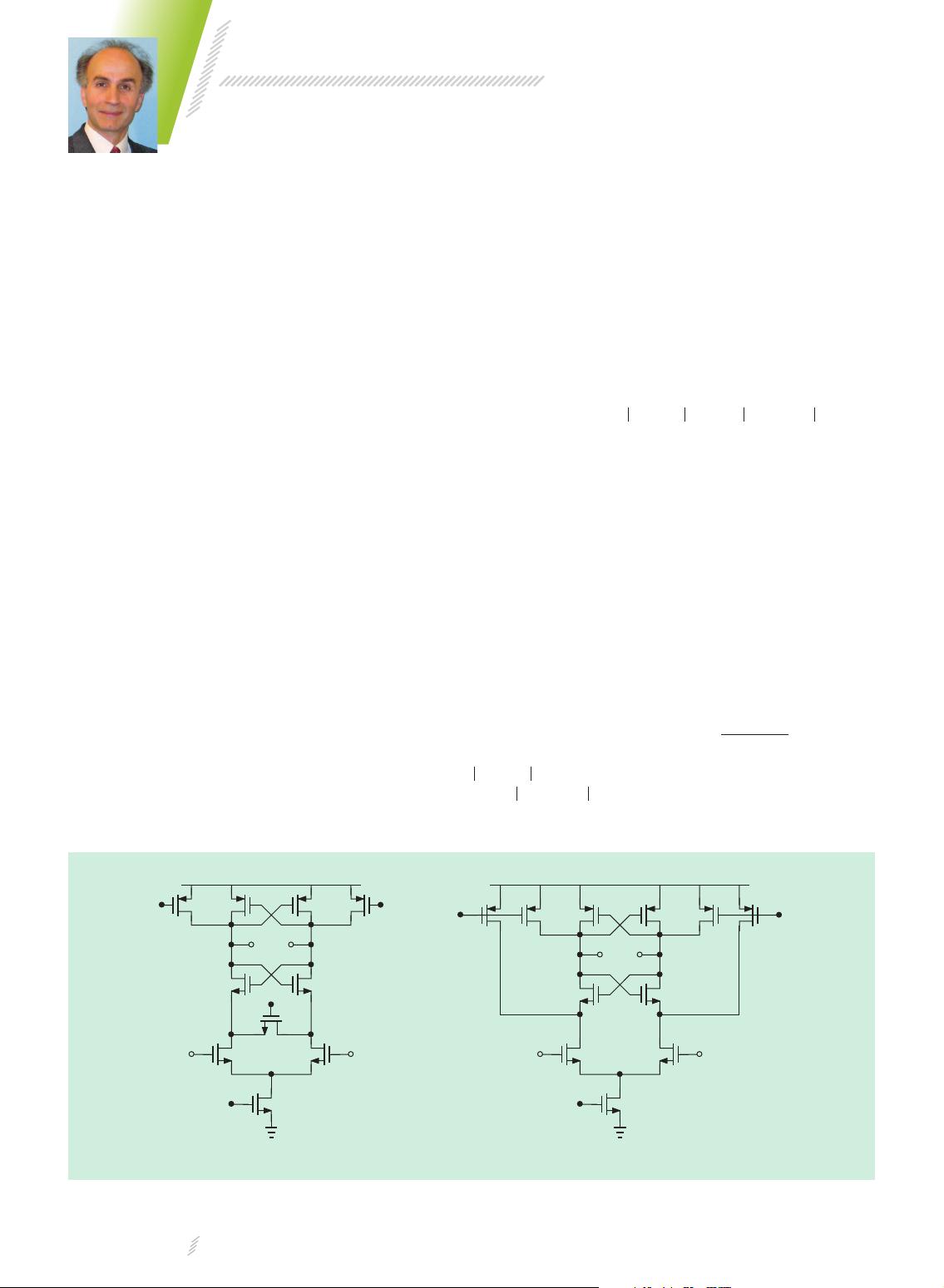

高速锁存比较器是模拟电路中的重要组成部分,尤其在模拟到数字转换器(ADC)中广泛应用。本篇文章将深入探讨一种被称为"StrongARM"锁存器的电路结构,该电路因其零静态功耗、直接输出轨至轨信号以及主要由一个差分对产生的输入参考偏移等特性而广受欢迎。 StrongARM锁存器最早由Toshiba的Kobayashi等人提出,并在Digital Equipment Corporation的StrongARM微处理器中得以应用,因此得名。其基本结构包括一个时钟控制的差分对、两个交叉耦合的对管以及四个预充电开关。在后续的发展中,该电路进行了改进,如图1(b)所示,它由时钟控制的差分对MM1和MM2、交叉耦合的对管MM3和MM4以及MM5和MM6,以及预充电开关SS1和SS2组成。 StrongARM锁存器的工作过程可以分为四个阶段: 1. 预充电阶段:CK信号为低,M1和M2关闭,节点P、Q、X和Y被预充电至VDD电平,电路简化为图2(a)所示状态。 2. 放大阶段:CK信号变为高,SS1和SS2断开,M1和M2导通,根据输入差分电压VV12,流过一对差分电流。由于MM3和MM6初始关闭,电流从CP和CQ流出,导致VVPQ-电压上升,可能超过输入电压VV12。这一阶段称为放大模式,因为在此期间,尾电流相对稳定,可以表示为: (g, m1) * VVCt = VVPQ - VV12 其中,g, m1是MM1和MM2的跨导。 3. 锁存阶段:当输入电压达到一定阈值后,VVPQ-足以使MM3或MM6导通,导致电流路径改变,锁存输入电压的状态。 4. 输出阶段:一旦MM3或MM6导通,电流路径被固定,输出X和Y将保持在相应的高或低电平,直到下一次CK信号变化。 StrongARM锁存器的这种工作机制使其成为高速比较器的理想选择,因为它能快速响应输入电压变化并提供足够的增益来放大小信号。同时,由于其零静态功耗,它在低功耗应用中具有显著优势。此外,由于输入偏移主要由一个差分对产生,这有助于减少噪声和提高精度。 在实际设计和应用中,工程师们会根据具体需求调整StrongARM锁存器的参数,例如通过改变MOSFET的尺寸来优化速度与增益之间的平衡,或者通过增加补偿电路来改善温度和电源电压变化的影响。StrongARM锁存器是模拟电路设计中的一种强大工具,对于理解高速锁存比较器的工作原理至关重要,也是模拟ADC设计者的必备知识。

- 粉丝: 0

- 资源: 3

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- new_bird_c-c语言入门

- christmasTree-圣诞树html网页代码

- working-shell脚本入门——流程控制

- hadoop_install-sqoop数据导入

- ThinkCMF-mysql安装

- BigData-Notes-sqoop的安装与配置

- C语言-leetcode题解之28-implement-strstr.c

- C语言-leetcode题解之27-remove-element.c

- C语言-leetcode题解之26-remove-duplicates-from-sorted-array.c

- C语言-leetcode题解之24-swap-nodes-in-pairs.c

信息提交成功

信息提交成功

评论0