Philips Semiconductors

I

2

S bus specification

February 1986

2

3.0 THE I

2

S BUS

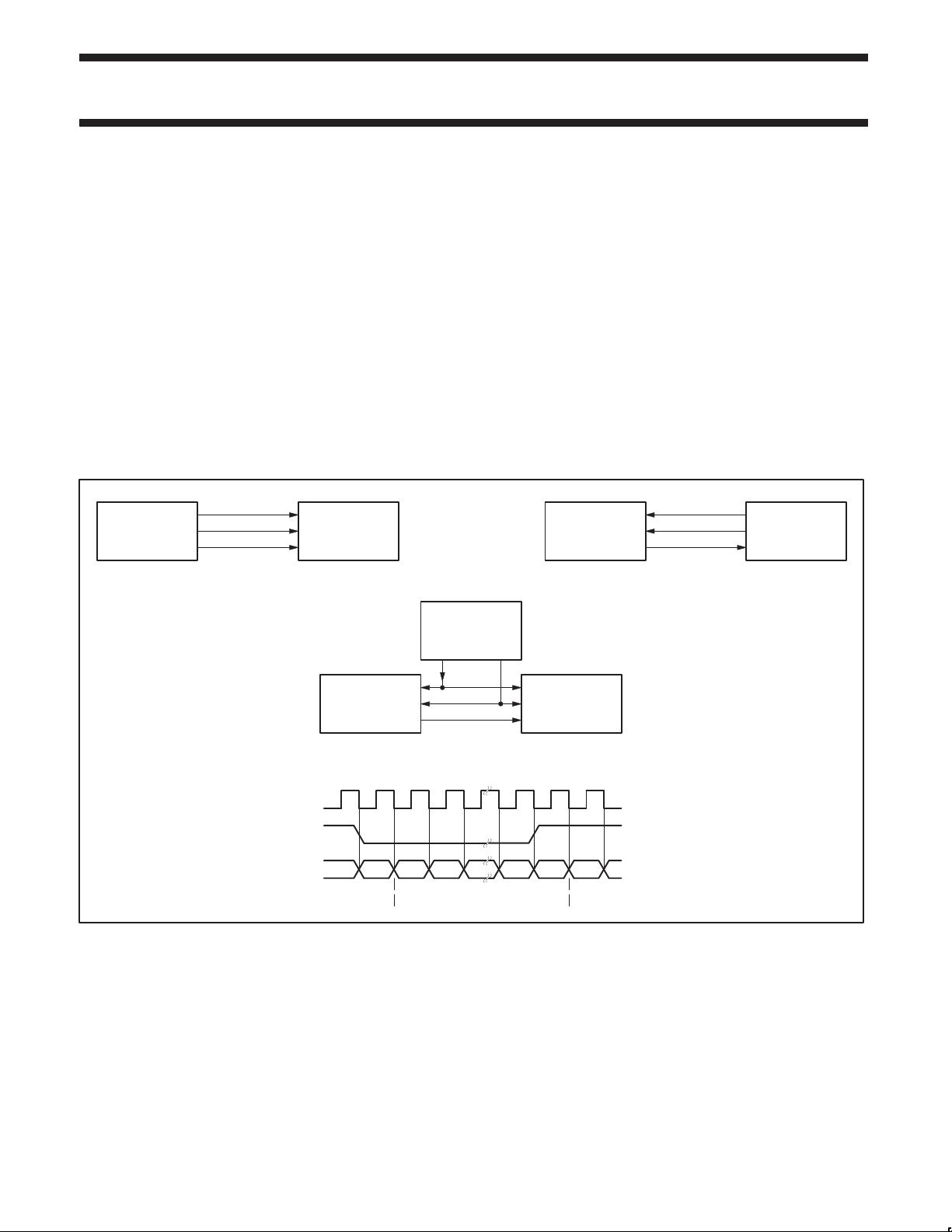

As shown in Figure 1, the bus has three lines:

•continuous serial clock (SCK);

•word select (WS);

•serial data (SD);

and the device generating SCK and WS is the master.

3.1 Serial Data

Serial data is transmitted in two’s complement with the MSB first.

The MSB is transmitted first because the transmitter and receiver

may have different word lengths. It isn’t necessary for the transmitter

to know how many bits the receiver can handle, nor does the

receiver need to know how many bits are being transmitted.

When the system word length is greater than the transmitter word

length, the word is truncated (least significant data bits are set to ‘0’)

for data transmission. If the receiver is sent more bits than its word

length, the bits after the LSB are ignored. On the other hand, if the

receiver is sent fewer bits than its word length, the missing bits are

set to zero internally. And so, the MSB has a fixed position, whereas

the position of the LSB depends on the word length. The transmitter

always sends the MSB of the next word one clock period after the

WS changes.

Serial data sent by the transmitter may be synchronized with either

the trailing (HIGH-to-LOW) or the leading (LOW-to-HIGH) edge of

the clock signal. However, the serial data must be latched into the

receiver on the leading edge of the serial clock signal, and so there

are some restrictions when transmitting data that is synchronized

with the leading edge (see Figure 2 and Table 1).

3.2 Word Select

The word select line indicates the channel being transmitted:

•WS = 0; channel 1 (left);

•WS = 1; channel 2 (right).

WS may change either on a trailing or leading edge of the serial

clock, but it doesn’t need to be symmetrical. In the slave, this signal

is latched on the leading edge of the clock signal. The WS line

changes one clock period before the MSB is transmitted. This allows

the slave transmitter to derive synchronous timing of the serial data

that will be set up for transmission. Furthermore, it enables the

receiver to store the previous word and clear the input for the next

word (see Figure 1).

4.0 TIMING

In the I

2

S format, any device can act as the system master by

providing the necessary clock signals. A slave will usually derive its

internal clock signal from an external clock input. This means, taking

into account the propagation delays between master clock and the

data and/or word-select signals, that the total delay is simply the

sum of:

•the delay between the external (master) clock and the slave’s

internal clock; and

•the delay between the internal clock and the data and/or

word-select signals.

For data and word-select inputs, the external to internal clock delay

is of no consequence because it only lengthens the effective set-up

time (see Figure 2). The major part of the time margin is to

accommodate the difference between the propagation delay of the

transmitter, and the time required to set up the receiver.

All timing requirements are specified relative to the clock period or to

the minimum allowed clock period of a device. This means that

higher data rates can be used in the future.

SD

and

WS

SCK

T

t

RC*

t

LC

≥ 0.35T t

HC

≥ 0.35T

V

H

= 2.0V

V

L

= 0.8V

t

htr

≥ 0

t

dtr

≤ 0.8T

T = clock period

T

tr

= minimum allowed clock period for transmitter

T>T

tr

∗ t

RC

is only relevant for transmitters in slave mode.

SN00120

Figure 2. Timing for I

2

S Transmitter

评论22

最新资源