没有合适的资源?快使用搜索试试~ 我知道了~

芯片设计进阶之路_121

1.该资源内容由用户上传,如若侵权请联系客服进行举报

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

版权申诉

0 下载量 26 浏览量

2023-11-10

18:06:13

上传

评论

收藏 14.84MB PDF 举报

温馨提示

试读

242页

资源芯片设计进阶之路_121知识分享

资源推荐

资源详情

资源评论

芯片设计进阶之路_121

目录

芯片设计进阶之路_121 1

第1篇 芯片设计进阶之路——Reset深入理解 2

第2篇 芯片设计进阶之路—亚稳态和同步器 24

第3篇 芯片设计进阶之路——跨时钟信号处理方法 37

第4篇 芯片设计进阶之路——SpyGlass CDC流程深入理解(一) 56

第5篇 芯片设计进阶之路——SpyGlass CDC流程深入理解(二) 69

第6篇 芯片设计进阶之路——从CMOS到建立时间和保持时间 86

第7篇 芯片设计进阶之路——SOC电源管理系统 104

第8篇 芯片设计进阶之路——低功耗深入理解(一) 110

第9篇 芯片设计进阶之路——门控时钟 123

第10篇 ISP从算法到硬件设计——从CCM到sensor结构 131

第11篇 芯片设计进阶之路——低功耗之多电压技术 159

第12篇 低功耗技术——低功耗中使用的特殊单元 166

第13篇 AXI3与AXI4区别及互联 190

第14篇 MIPI APHY:专为汽车而生 200

第15篇 TOF技术全解读 219

第16篇 光与影之歌:GPU基本处理流程 227

芯片设计进阶之路——Reset深入理解

Reset深入理解

------------------------------------------

版权声明:

本文作者: 烓围玮未

微信公众号:芯片设计进阶之路

首发于知乎专栏《芯片设计进阶之路》,转发无需授权,请保留这段声明。

------------------------------------------

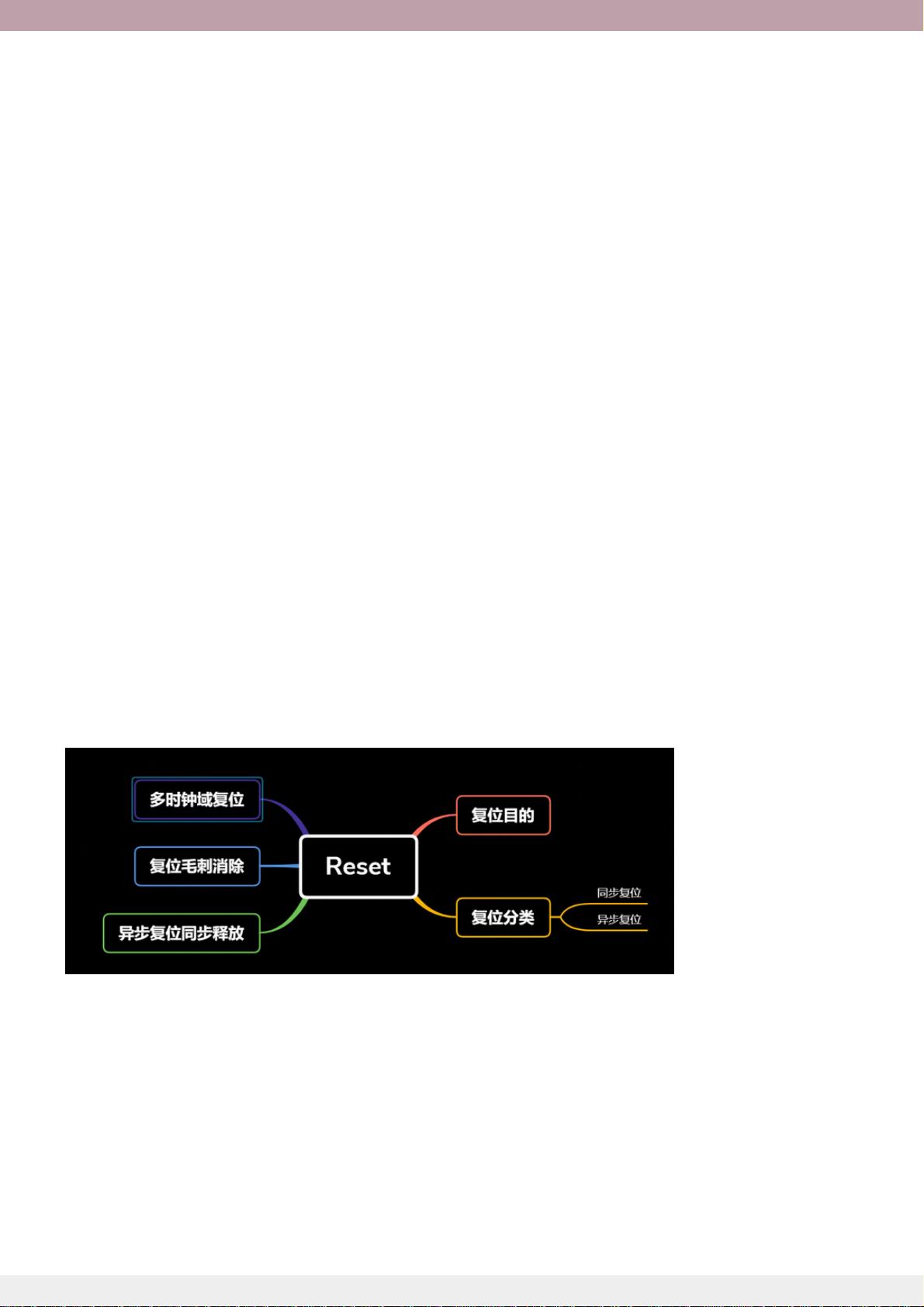

首先上思维导图:

如果要问“芯片中怎么复位才对?”

很多人都会回答“异步复位同步释放”。

但是为什么要用异步复位同步释放,是不是所有的芯片都必须采用这种方式,估计很少人能回答

上来。那么让我们从为什么要复位开始。

1. 复位的目的

第1篇 芯片设计进阶之路——Reset深入理解

第 1 页 /共

240 页

复位信号在数字电路里面的重要性仅次于时钟信号。对一个芯片来说,复位的主要目的是使芯片

电路进入一个已知的,确定的状态。主要是触发器进入确定的状态。在一般情况下,芯片中的每

个触发器都应该是可复位的。在某些情况下,当在高速应用程序中使用流水线触发器(移位寄存器

触发器)时,为了实现更高的性能设计,可能会从某些触发器中消除复位。这种类型设计需要在复

位激活期间,运行预先确定数量的时钟周期,以使ASIC处于已知的状态。

1.1 为什么需要复位呢?

1)复位可以使电路从确定的初始状态开始运行:

上电复位:上电的时候,为了避免上电后进入随机状态而使电路紊乱,这个时候就需要上电

复位。

中间复位:有时候,要求电路从初始状态开始执行电路的功能,要对电路进行复位,让它从

最初的状态开始运行。

2) 复位可以使电路从错误状态回到可以控制的确定状态:

如果电路发生了异常,比如状态不正常,中断异常,firmware程序跑飞,这个时候就可以对

电路进行复位,让它从错误的状态回到一个正常的状态。

3) 电路仿真时需要电路具有已知的初始值

在仿真的时候,信号在初始状态是未知状态(也就是所谓的x,不过对信号初始化之后的这种情况

除外,因为仿真的时候对信号初始化就使信号有了初始值,这就不是x了)。

对于 (数字系统一般分为数据通路和控制通路,数据通路一般是对输入的数据进行处理,数据通路

控制通路则是对运行的情况进行操作),在实际电路中,只要输入是有效数据(开始的时候可能不

是有效的),输出后的状态也是确定的;在仿真的时候,也是输入数据有效了,输出也就确定了。

也就是说,初始不定态对数据通路的影响不明显。

对于 ,在实际电路中,只要控制通路完备(比如说控制通路的状态机是完备的),即使初控制通路

始状态即使是不定态,在经过一定的循环后,还是能回到正确的状态上;然而在仿真的时候就不行

了,仿真的时候由于初始状态为未知态,控制电路一开始就陷入了未知态;仿真跟实际电路不同,

仿真是“串行”的,仿真时控制信号的初始不定态会导致后续的控制信号结果都是不定态,也就

是说,初始的不定态对控制通道是致命的。

1.2 不需要复位的情况

复位信号很重要,但是并不是每一部分的电路都需要复位电路,一方面是复位电路也消耗逻辑资

源、占用芯片面积,另一方面是复位信号会增加电路设计的复杂性(比如要考虑复位的策略、复位

的布局布线等等)。

当某个电路的输出在任何时刻都可以不受到复位信号的控制就有正确的值时,比如说数据通路中

的对数据进行处理的部分。在某些情况下,当流水线的寄存器(移位寄存触发器)在高速应用中

时,应该去掉某些寄存器的复位信号以使设计达到更高的性能,因为带复位的触发器比不带复位

的触发器更复杂,反应也更慢。

第1篇 芯片设计进阶之路——Reset深入理解

第 2 页 /共

240 页

2. 同步复位

2.1 同步复位的实现方式

同步复位的前提是,复位信号只会在时钟的有效边沿去影响或者复位flip-flop。Reset可以作为

组合逻辑的一部分送给FF的D端。这种情况下,编码方式必须是if/else 优先级的方式,而且

reset只能放在if条件下,其他组合逻辑放到else逻辑下。

正确的方式去构建同步复位FF的verilog代码如下:

如果没有严格遵守这种方式,会有两个问题:

1、一些仿真器中,基于逻辑方程,逻辑可能组织复位到达触发器。这只是一个仿真问题,不是硬

件问题。但是复位的一个主要目的,就是仿真的时候将电路置于一个已知的确定状态。

2、由于复位树的高扇出,复位信号可能是一个相对于时钟周期的“延迟到达信号”,尽管复位将

从复位缓冲区树中进行缓冲,但明智的做法是限制复位到达本地逻辑后必须经过的逻辑量。就是

说必须对复位信号少做逻辑。

下面的列子是一个同步复位的,带进位的计数器(loadable counter with synchronous reset)

第1篇 芯片设计进阶之路——Reset深入理解

第 3 页 /共

240 页

剩余241页未读,继续阅读

资源评论

北极象

- 粉丝: 1w+

- 资源: 345

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功