没有合适的资源?快使用搜索试试~ 我知道了~

数字电子闹钟综合设计实验

温馨提示

试读

22页

综合运用MAX+PlusⅡ图形编辑器、文本编辑器等设计输入手段,通过本实验设计输入,应用层次化、模块化设计方法, 掌握自顶向下、自底向上及混合式设计方法及图形文件的编译、适配和仿真,完成数字电子闹钟的全部设计并编程(下载)。(一) 设计要求 1. 功能要求: a) 输入: i. CLK——时钟频率为10 MHz的输入,分频产生秒时钟。 ii. MOD——工作方式选择。 iii. ADJ——调校。 b) 输出: i. 六位LED数码管显示,动态扫描驱动。 ii. 一位LED报警、一位蜂鸣器报警信号。 c) 电路分五个工作状态,由MOD、ADJ按键组合选择控制选择: i. 正常计时:二位时、二位分、二位秒LED显示,十进制数表示。 ii. 调校计时_时:显示时、分、秒;时闪烁;通过ADJ按键修改计时的时值。 iii. 调校计时_分:显示时、分、秒;分闪烁;通过ADJ按键修改计时的分值。 iv. 调校计时_秒:显示时、分、秒;秒闪烁;通过ADJ按键对秒值清零。 v. 调校定闹_时:显示闹时、闹分;闹时闪烁;通过ADJ按键设定闹时值。 vi. 调校定闹_分:显示闹时、闹分;闹分闪烁;通过ADJ按键设定闹分值。 d) 当正常计时的时、分值等于预设的闹时、闹分值时,LED、蜂鸣器报警信号有效。 2. 扩展(在上述功能要求基础上,选做): a) 秒表功能:最大显示99分、59秒、10分之1秒、100分之1秒;可暂停、继续、停止、重新开始等;可增加必要的操作键和LED显示。 b) 在秒表功能基础上,再增加分段计时及累计功能:具体功能和输入输出可自定。

资源推荐

资源详情

资源评论

综合实验 数字电子闹钟综合设计实验

一、实验目的

综合运用 MAX+PlusⅡ 图形编辑器、文本编辑器等设计输入手段,通过本实验设计输入,

应用层次化、模块化设计方法, 掌握自顶向下、自底向上及混合式设计方法及图形文件的

编译、适配和仿真,完成数字电子闹钟的全部设计并编程(下载)。

二、实验器材

微机系统,MAX+PlusⅡ 10.2 开发工具软件,LP-2900 EDA 实验装置。

三、实验内容

(一) 设计要求

1.功能要求:

a) 输入:

i. CLK——时钟频率为 10 MHz 的输入,分频产生秒时钟。

ii. MOD——工作方式选择。

iii. ADJ——调校。

b) 输出:

i. 六位 LED 数码管显示,动态扫描驱动。

ii. 一位 LED 报警、一位蜂鸣器报警信号。

c) 电路分五个工作状态,由 MOD、ADJ 按键组合选择控制选择:

i. 正常计时:二位时、二位分、二位秒 LED 显示,十进制数表示。

ii. 调校计时_时:显示时、分、秒;时闪烁;通过 ADJ 按键修改计时的时

值。

iii. 调校计时_分:显示时、分、秒;分闪烁;通过 ADJ 按键修改计时的分

值。

iv. 调校计时_秒:显示时、分、秒;秒闪烁;通过 ADJ 按键对秒值清零。

v. 调校定闹_时:显示闹时、闹分;闹时闪烁;通过 ADJ 按键设定闹时值。

vi. 调校定闹_分:显示闹时、闹分;闹分闪烁;通过 ADJ 按键设定闹分值。

d) 当正常计时的时、分值等于预设的闹时、闹分值时,LED、蜂鸣器报警信号

有效。

2.扩展(在上述功能要求基础上,选做):

a) 秒表功能:最大显示 99 分、59 秒、10 分之 1 秒、100 分之 1 秒;可暂停、

继续、停止、重新开始等;可增加必要的操作键和 LED 显示。

b) 在秒表功能基础上,再增加分段计时及累计功能:具体功能和输入输出可自

定。

(二) 实验过程安排

全部实验内容由五个子实验组成,并分五次进行:

子实验一:

1. 建立一个总工作目录并建立顶层的项目文件(TOP.gdf),按设计要求划分功能

模块,运用图形设计方法,建立各功能模块的符号,及初步的信号连接。

2. 在总工作目录下建立一个子工作目录并建立一个低层的计时模块文件

(MDL1.gdf), 按设计要求,运用图形或文本设计方法,完成计时模块的逻辑描

述设计、编译及仿真设计,并应具备正常计时电路的 24 进制计时、60 进制计

分、60 进制计秒及闹钟定时电路的 24 进制计时、60 进制计分的的功能。

3. 可向下功能划分,作子模块设计,但要求有子模块仿真设计。

子实验二:

4. 在总工作目录下建立一个子工作目录并建立一个低层的七段 LED 显示译码模块

文件(MDL2.gdf), 按设计要求,运用图形或文本设计方法,完成六位七段 LED

数码管的显示译码及动态扫描驱动的逻辑描述设计、编译及仿真设计,并应具

备调校时、分、秒时的闪烁功能。

5. 可向下功能划分,作子模块设计,但要求有子模块仿真设计。

子实验三:

1. 在总工作目录下建立一个子工作目录并建立一个低层的控制模块文件

(MDL3.gdf), 按设计要求,运用图形或文本设计方法,完成正常计时、调校、

定闹及到时报警的逻辑描述设计、编译及仿真设计,并应具备调校时、分、秒

时的闪烁功能。

2. 可向下功能划分,作子模块设计,但要求有子模块仿真设计。

子实验四:

1. 在总工作目录下建立一个子工作目录并建立一个低层的分频模块文件

(MDL4.gdf), 按设计要求,运用图形或文本设计方法,完成 10MHz 输入到

1Hz 输出的逻辑描述设计、编译及仿真设计。

2. 可向下功能划分,作子模块设计,但要求有子模块仿真设计。

子实验五:

1. 熟悉 LP-2900 EDA 实验装置的面板布局及主要操作单元的引脚序号,正确掌握

LP-2900 EDA 实验装置的使用。

2. 将子实验一~子实验四的各模块设计,例化(引用)为顶层项目文件

(TOP.gdf)的各模块,完善总体控制及连接,分配指定引脚,完成顶层项目文

件的逻辑描述设计、编译及仿真设计、适配。

3. 实现顶层项目设计文件对 FPGA(EPF10K10TC144-3)的编程(下载)。

4. LP-2900 EDA 实验装置加电,验证并确保其功能符合要求,交实验指导老师检

查登记。

(三) 实验设计

1. 设计文件层次图

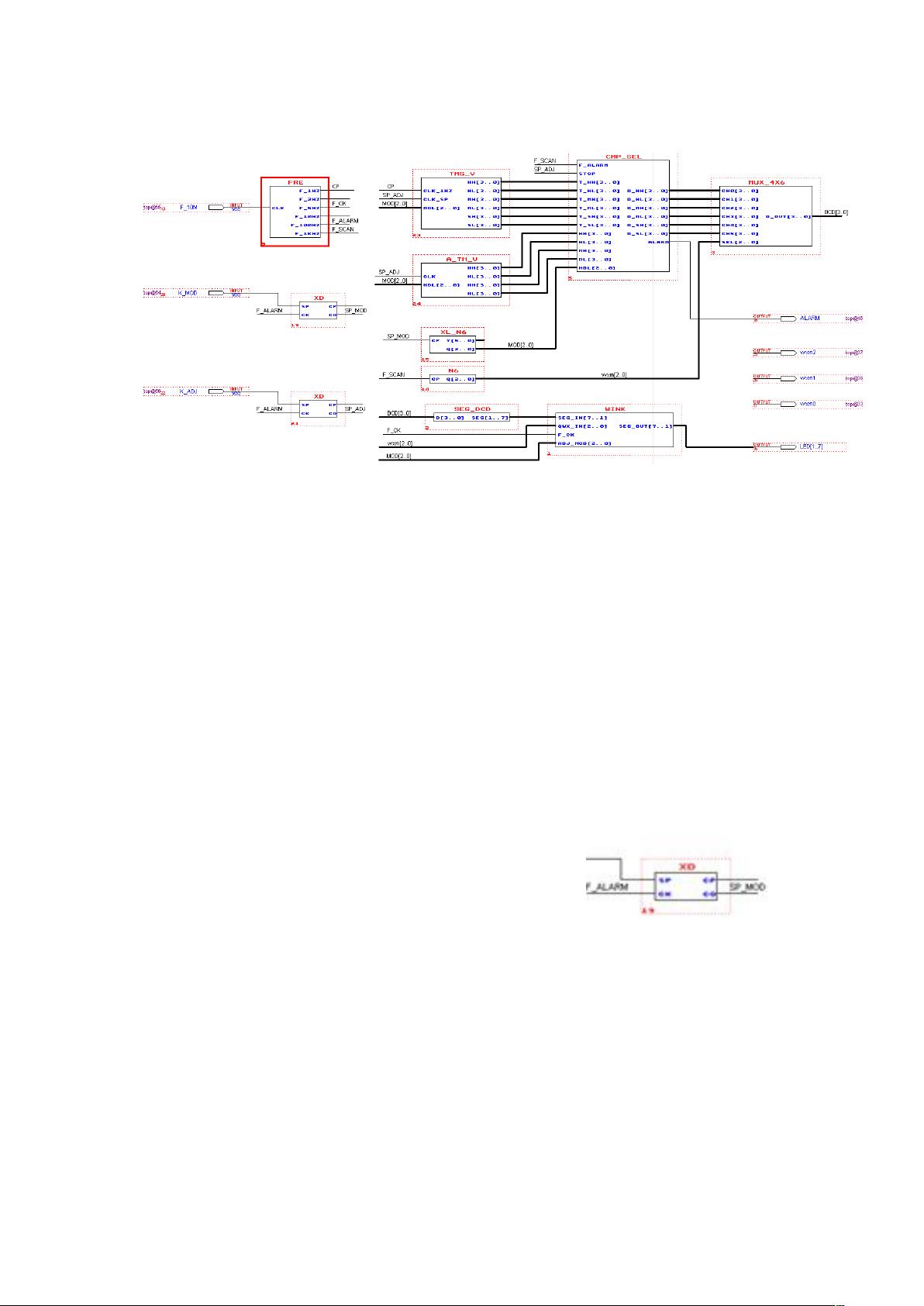

2. 顶层项目设计文件(TOP.gdf)图及模块说明

3. 各子模块文件(图)及设计要点说明

4. 各仿真测试波形文件图及计要点说明

5. 总体设计、实验结果的文字说明

简单分析顶层文件

模块简单介绍

1、XD:防抖模块。实现功能在一段时间内(很小),不管按下几下键都认为是一

下。

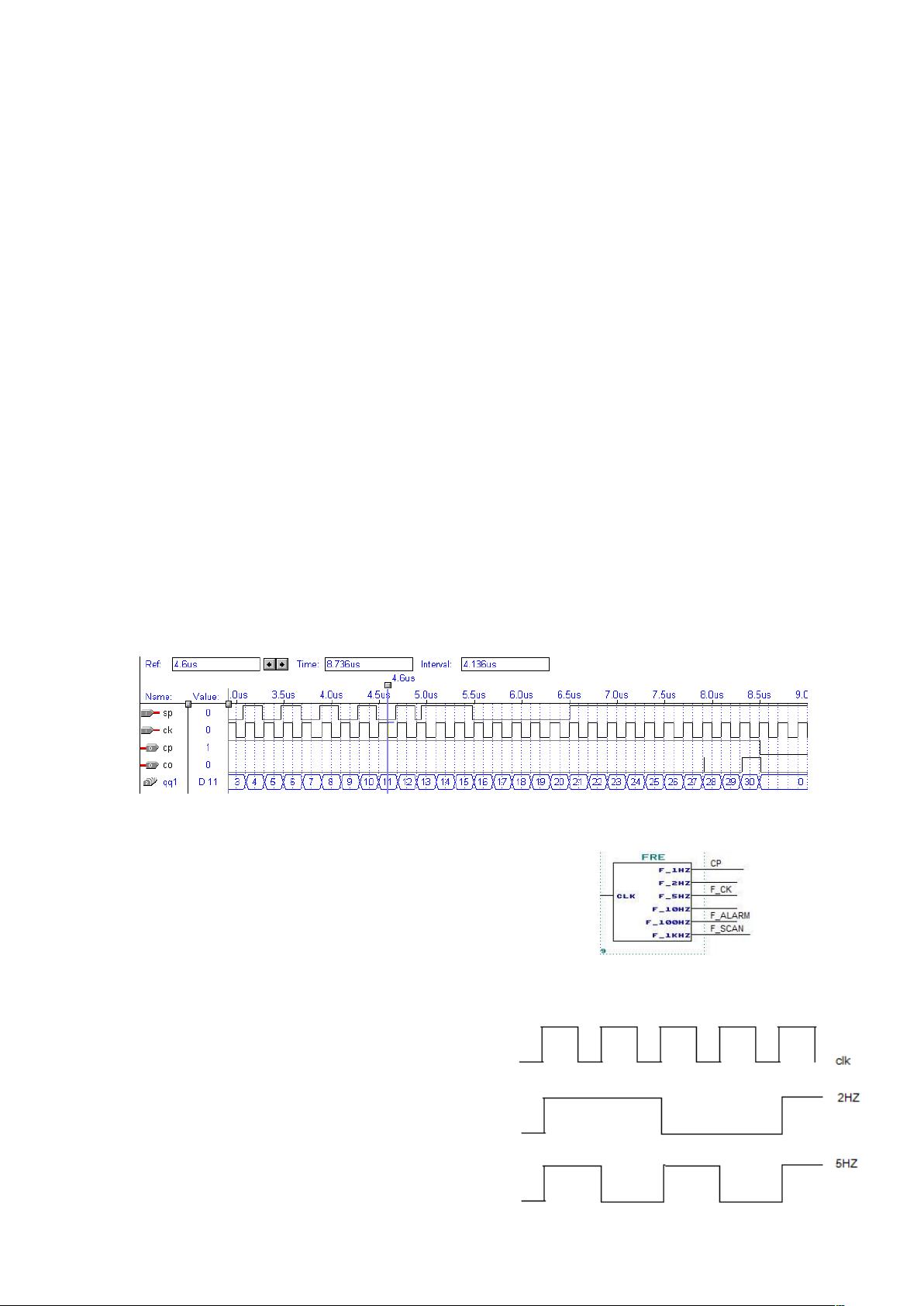

2、FRE:多级分频器。把 10MKZ 脉冲进行分频处理。

3、XL_N6:模式选择器。调表的时分秒、闹钟的时分。

4、MUX_4X6:6 选一选择器,选择其中一位输出到七段扫描器上。

5、SEG_DCD:七段译码器。

6、WINK:闪烁模块。

7、TIMER:实现闹钟计时功能。

8、AlARM_TIMER:实现闹钟定时定分功能。

9、CMP_SEL:比较器。比较正常计时和预订闹钟时间是否一致。

1>、防抖模块

XD.Vhd

LIBRARY IEEE; 模块截图如下

USE IEEE.STD_LOGIC_1164.ALL;

USE ieee.std_logic_ARITH.all;

USE ieee.std_logic_UNSIGNED.all;

ENTITY xd IS

PORT( sp : IN STD_LOGIC;

ck : IN STD_LOGIC;

cp,co : out STD_LOGIC);

END xd;

ARCHITECTURE arch OF xd IS

SIGNAL cr : STD_LOGIC;

CONSTANT N : INTEGER := 30;

BEGIN

PROCESS(ck,sp)

VARIABLE qq0 : STD_LOGIC;

VARIABLE qq1 : INTEGER RANGE 0 TO 63;

顶层文件图

BEGIN

IF sp='0'THEN qq0:='1';

elsif cr='0' then qq0:='0';

END if;

IF ck='1'AND ck'EVENT

THEN IF qq0='1'THEN

IF qq1<=N-1 THEN qq1:=qq1+1;cr<='1';

ELSE qq1:=0;cr<='0';

END if;

END if;

END if;

IF qq1=N THEN co<='1';

ELSE co<='0';

END if;

cp<=qq0;

end process;

END arch;

作用说明:具有延时功能,输入脉冲为 100HZ,防抖界限为 63,输入脉冲为 1KHZ,防抖

界限为 10000.延时时间大于抖动时间。当在一段时间内,按下 adj 和 mod 键只认为是一

次按下。避免产生了连续按下结果错误的情况。

仿真图如下:

2>、分频器模块

FRE.VHD

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_ARITH.all;

USE ieee.std_logic_UNSIGNED.all;

ENTITY FRE IS

PORT

( --en,rst : IN STD_LOGIC ;

clk : IN STD_LOGIC ;

F_1HZ,F_2HZ : OUT STD_LOGIC

;

F_5HZ,F_10HZ : OUT STD_LOGIC

;

F_100HZ : OUT STD_LOGIC ;

F_1KHZ : OUT STD_LOGIC );

END FRE;

ARCHITECTURE A OF FRE IS

COMPONENT CNT10 --调用底层文件,引用 CNT10,十进制计数器。

PORT (en,rst : IN STD_LOGIC ;

clk : IN STD_LOGIC ;

q : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ;

co : OUT STD_LOGIC );

END COMPONENT;

SIGNAL FRE1M,FRE100K,FRE10K,FRE1K,FRE100,FRE10,FRE1:STD_LOGIC;

SIGNAL FRE5,FRE2 :STD_LOGIC;

SIGNAL cnt5 :std_logic_vector(2 downto 0);

SIGNAL PD,ND :STD_LOGIC;

BEGIN

ND<='0';

PD<='1';

U0:CNT10 PORT MAP (EN=>PD,CLK=>CLK ,RST=>nd,co=>FRE1M); --运用连接语句,接连符

号左边是结构体,

U1:CNT10 PORT MAP (EN=>PD,CLK=>FRE1M ,RST=>nd,co=>FRE100K); --右边是实体。

U2:CNT10 PORT MAP (EN=>PD,CLK=>FRE100K ,RST=>nd,co=>FRE10K);

U3:CNT10 PORT MAP (EN=>PD,CLK=>FRE10K,RST=>nd,co=>FRE1K);

U4:CNT10 PORT MAP (EN=>PD,CLK=>FRE1K ,RST=>nd,co=>FRE100);

U5:CNT10 PORT MAP (EN=>PD,CLK=>FRE100,RST=>nd,co=>FRE10);

U6:CNT10 PORT MAP (EN=>PD,CLK=>FRE10 ,RST=>nd,co=>FRE1);

F_1HZ<=FRE1; --将节点信号送入实际端口,赋给输出。

F_2HZ<=FRE2;

F_5HZ<=FRE5;

F_10HZ<=FRE10;

F_100HZ<=FRE100;

F_1KHZ<=FRE1K;

FP5: --2 分频 5HZ

process(fre10)

begin

if fre10'event and fre10='1' then --输入的信号值为 fre10,上升沿时,fre5 取反。

fre5<=not fre5;

end if;

剩余21页未读,继续阅读

资源评论

szetosaya2013-12-09功能很全,完全符合要求。

szetosaya2013-12-09功能很全,完全符合要求。

huishouwuyu

- 粉丝: 0

- 资源: 3

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- python 函数的动态参数python 函数的动态参数python 函数的动态参数python 函数的动态参数.txt

- JAVA基于遗传算法的中药药对挖掘系统的设计与实现(源代码+论文)

- 课堂实验 实现对电影的爬取做可视化

- java Web实现用户登录功能.txt

- 基于SpringBoot+MyBatis-Plus+Vue+element ui的前后端分离的影院选座购票系统源码.zip

- 财大===统计学复习资料===2023-2024-02.zip

- Filo - The Cable Simulator v1.5

- 2024年 Java 面试八股文(20w字2024年 Java 面试八股文(2024年 Java 面试八股文(20w字).txt

- Unity简单版本小地图功能

- 基于UCI Heart Disease数据集的心脏病分析python源码+数据集+分析报告+演讲PPT.zip

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功